인프런 커뮤니티 질문&답변

NPU 설계에서, low-level 설계가 무엇인가요?

작성

·

1.8K

1

제가 아직 완강을 하지 않아서 드리는 질문이면 죄송합니다..^^

Deep learning 설명 중에, 이미지를 예시로 들면서 low-level feature라는 단어를 언급하셨는데요,

실제 NPU설계 시 Low-level 설계라 하면, 이를 위 설명과 연관지어서 이해할 수 있을까요?

GPU에 비견했을 때, 연산하는 정보가 이미지가 아닌, 다른 목적(음성, 텍스트 등)일 때 해당하는 정보를 처리하는 Processing unit이라고 이해했습니다. (틀리다면 정정 부탁드립니다..^^)

이런 부분에 대해서, 혹시 low-level설계에 관해 아시는 바를 좀더 구체적으로 설명주실 수 있을까요?

- 강의 내용외의 개인 질문은 받지 않아요 (개별 과제, 고민 상담 등..)

- 저 포함, 다른 수강생 분들이 함께보는 공간입니다. 보기좋게 남겨주시면 좋은 QnA 문화가 될 것 같아요. (글쓰기는 현업에서 중요한 능력입니다!)

- 학습 관련 질문을 남겨주세요. 상세히 작성하면 더 좋아요!

- 먼저 유사한 질문이 있었는지 검색해보세요.

- 서로 예의를 지키며 존중하는 문화를 만들어가요.

- 잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

답변 2

1

0

안녕하세요 :)

먼저 다음 문장을 동일하게 생각하시는 것 같아서 말씀드리고 시작할께요.

"Deep learning 설명 중에, 이미지를 예시로 들면서 low-level feature" , "실제 NPU설계 시 Low-level 설계" 는 서로 다른 개념이다 말씀드리고 시작하겠습니다.

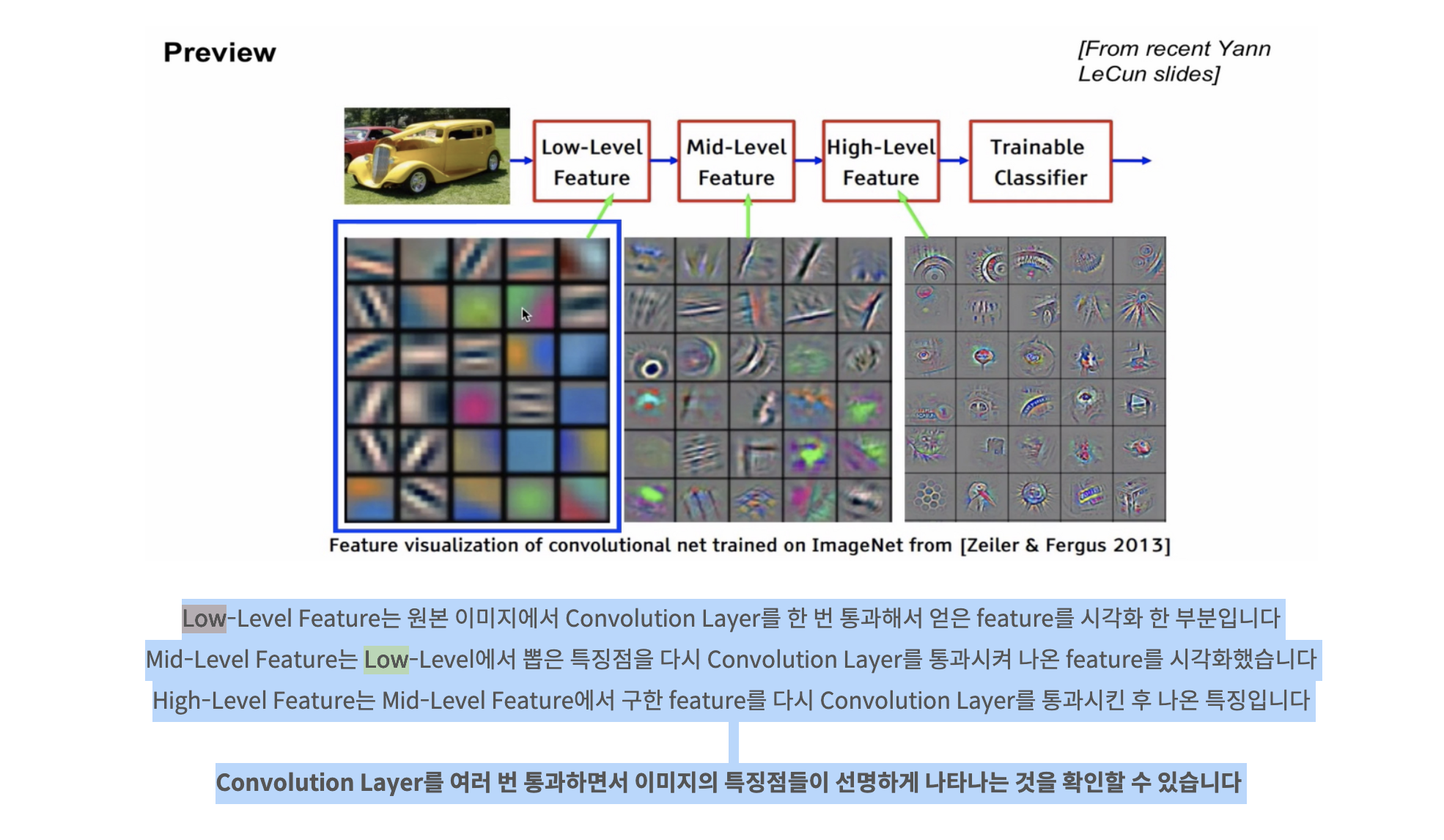

Deep learning 설명 중에, 이미지를 예시로 들면서 low-level feature

출처 : https://machine-learning-engineer.tistory.com/12

DNN 의 Layer 를 거치면서 만들어지는 것이, Feature map 입니다.

DNN 의 Layer 를 거치면서 만들어지는 것이, Feature map 입니다.

low-level-feature 는 DNN 의 Layer 의 출력 중 초반부 (앞단) 의 출력을 의미합니다.

반대로 후반부로 가면 High-level-feature 가 되겠죠?

실제 NPU설계 시 Low-level 설계

앞서 설명드린 이야기는 순수 AI 알고리즘 만의 이야기 였다면, 해당 주제는 설계 관점의 이야기 입니다.

어떻게 보면 HW 뿐만 아니라 SW 도 Low-level-design 이라는 개념을 갖고 있죠.

https://en.wikipedia.org/wiki/Low-level_design

NPU 설계라고 물어봐 주셨으니, HW 설계 관점에서 답변드리면

설계시, Bottom -> Top 으로 올라가는 방법으로 설계한다 이렇게 답변드리고 싶네요.

"GPU에 비견했을 때, 연산하는 정보가 이미지가 아닌, 다른 목적(음성, 텍스트 등)일 때 해당하는 정보를 처리하는 Processing unit이라고 이해했습니다."

GPU 의 Processing Unit 은 연산의 기본 단위 (곱하고, 더하고, 등등) 라고 생각해 주시면 될 것 같아요.

영상에서 구글의 TPU 를 예를 들면서 다뤘던 것으로 기억합니다.

즐공하세요 :)

안녕하세요 :)

단순히 같은 표현이었군요, 주신 설명은 Hierarchical design에서 하위 블락 설계에 해당한다는 말씀이네요.

다음 이야기라면 맞습니다.

사실 NPU와 GPU의 해당 low-level unit의 구체적인 차이가 궁금했습니다.

"구체적인 차이"는 설계자가 아닌한 정확한 답변은 어려울 것 같아요.

GPU 의 경우는 다음 링크가 도움이 되실꺼에요 :) http://nvdla.org/

예를들어 GPU는 그래픽을 처리하는 데 적합한 instruction set을 갖춘 processing unit을 설계한다고 하면,

맞습니다.

NPU의 경우에는 처리하고자 하는 데이터에 타겟하여(NPU의 적용제품에 따라 다르게) 매 제품(?) 마다 다른 식으로 설계되는 것인지,

회사마다 다겠지만, NPU 의 경우 보통 "Processing Unit 의 개수를 얼만큼 사용해주느냐" 에 따라 Low-end ~ High-end 급으로 나눕니다. (곱하고 더하고를 효율적으로 하기 위한)

물론 타겟이 어디냐에 따라 Architecture 자체가 다를 수 있죠.

결론은 회사마다 칩 내부 구성은 다르며, 제품의 타겟을 어디에 두느냐에 따라 다르다. (다른식으로 설계된다)

정확하게 이거다 답변은 어려운 점은 이해 부탁드릴께요.

즐공하세요 :)

네, 굉장히 빠른 답변을 주셔서 놀랐네요. 감사합니다.

단순히 같은 표현이었군요, 주신 설명은 Hierarchical design에서 하위 블락 설계에 해당한다는 말씀이네요.

사실 NPU와 GPU의 해당 low-level unit의 구체적인 차이가 궁금했습니다.

예를들어 GPU는 그래픽을 처리하는 데 적합한 instruction set을 갖춘 processing unit을 설계한다고 하면, NPU의 경우에는 처리하고자 하는 데이터에 타겟하여(NPU의 적용제품에 따라 다르게) 매 제품(?) 마다 다른 식으로 설계되는 것인지, 아니면 바로 이런 부분을 re-programmable하게 하기 위해서 FPGA을 아키텍쳐적으로 결합하고자 하는 것인지요..

짧게 주워모은 지식으로 이해해보고자 하는데, 맞는 방향으로 이해하고 있는지 여쭈어 봅니다.

미리 감사드립니다.