-

질문 & 답변

카테고리

-

세부 분야

반도체

-

해결 여부

미해결

PS 설계부분 관련

22.10.10 17:16 작성 조회수 181

1

- 강의 내용외의 개인 질문은 받지 않아요 (개별 과제, 고민 상담 등..)

- 저 포함, 다른 수강생 분들이 함께보는 공간입니다. 보기좋게 남겨주시면 좋은 QnA 문화가 될 것 같아요. (글쓰기는 현업에서 중요한 능력입니다!)

- 학습 관련 질문을 남겨주세요. 상세히 작성하면 더 좋아요!

- 먼저 유사한 질문이 있었는지 검색해보세요.

- 서로 예의를 지키며 존중하는 문화를 만들어가요.

- 잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

안녕하세요. 이번 ai-hw강의 잘 들었습니다. 강의 수강 후 궁금한 점이 몇 가지 있어 질문드립니다.

이번 PS부분 설계에서 feature map, weight, bias의 값들을 모두 랜덤 값으로 넣어 주었는데, 사실 코드를 보면 각각의 배열에 같은 숫자만 반복해서 들어가는거 아닌가요? (예를 들면 bias[och] = {42, 42, 42, ...}와 같이)

PS에서 PL부분으로 데이터를 넘겨줄 때,

Xil_Out32 ((u32) (XPAR_CNN_CORE_TEST_CI3_CO_0_BASEADDR + F_VAL_ADDR), (u32) fmap_rand_val);

와 같이 한 줄로만 넘겨주었는데 for문 없이 어떻게 데이터가 순차적으로 넘어가나요? PL부분에서 받는 데이터의 크기를 정해주었기 때문에 그 정도에 부합하는 횟수만큼만 받는건가요? 아님 사실 데이터가 순차적으로 넘어가는게 아니라 한 개의 데이터만 axi4 lite 레지스터에 넣어놓고 PL에서 계속 그 데이터만 참고하는 건가요?

답변을 작성해보세요.

0

설계독학맛비

지식공유자2022.10.11

안녕하세요 :)

Q1. 이번 PS부분 설계에서 feature map, weight, bias의 값들을 모두 랜덤 값으로 넣어 주었는데, 사실 코드를 보면 각각의 배열에 같은 숫자만 반복해서 들어가는거 아닌가요? (예를 들면 bias[och] = {42, 42, 42, ...}와 같이)

A1. 알고계신대로 중복해서 들어가게 됩니다. 이 부분은 Core 입장에서는 다른값들 입력 처리가 가능합니다. 하지만 입력을 넣어주는 방법이 현재 미완성상태 이기 때문에 FPGA 시간에서 배운 axi4-lite 를 사용했습니다. 현재까지 배운 내용으로 서로다른 입력을 받고 싶다면,

1) AXI4-Lite 의 Reg 수를 늘리시고,

2) 중복 대신 각각 Port 에 값을 할당하시면 됩니다.

Q2. PS에서 PL부분으로 데이터를 넘겨줄 때,

Xil_Out32 ((u32) (XPAR_CNN_CORE_TEST_CI3_CO_0_BASEADDR + F_VAL_ADDR), (u32) fmap_rand_val);

와 같이 한 줄로만 넘겨주었는데 for문 없이 어떻게 데이터가 순차적으로 넘어가나요? PL부분에서 받는 데이터의 크기를 정해주었기 때문에 그 정도에 부합하는 횟수만큼만 받는건가요? 아님 사실 데이터가 순차적으로 넘어가는게 아니라 한 개의 데이터만 axi4 lite 레지스터에 넣어놓고 PL에서 계속 그 데이터만 참고하는 건가요?

해당 함수는 한 값만 넘어갑니다. 즉 Q1 에서의 중복 값을 사용했습니다.

핑계?를 조금 대자면 이는 아직 저희가 AXI4 Standard 를 배우지 못한 상태라서, AXI4-Lite 를 사용하려다 보니 이렇게 구현이 되었습니다.

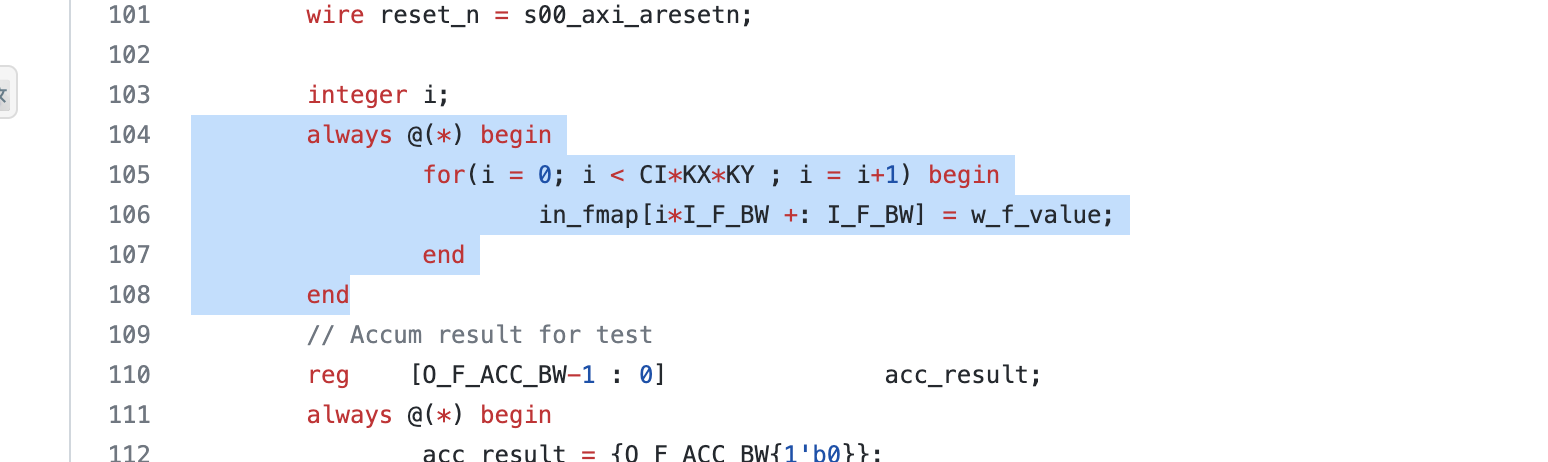

cnn_core_top.v 의 104~108 line을 보시면

입력을 배열에 중복해서 넣고있죠.

입력을 배열에 중복해서 넣고있죠.

이 부분을 서로 다른 입력을 받도록 수정하시면 궁금증이 해소가 대실꺼에요.

즐공하세요 :)

Junghwan Goh

질문자2022.10.12

답변 감사합니다! 저 질문이 좀 더 있는데요,

그럼 서로 다른 값을 연속(?)적으로 받고 싶으면 저번 FPGA강의에서 BRAM을 사용한 방법이 그나마 괜찮은가요?

LUT의 양은 어떻게 짐작할 수 있나요? 사실 저번 FPGA강의에서 실습한 FC Layer의 곱 연산 수도 꽤 많았던 걸로 기억하는데 그때와 비교해서 이번 CNN Core의 LUT 사용량이 더욱 많은 것 같아서요.

설계독학맛비

지식공유자2022.10.13

안녕하세요 :)

Q1. 그럼 서로 다른 값을 연속(?)적으로 받고 싶으면 저번 FPGA강의에서 BRAM을 사용한 방법이 그나마 괜찮은가요?

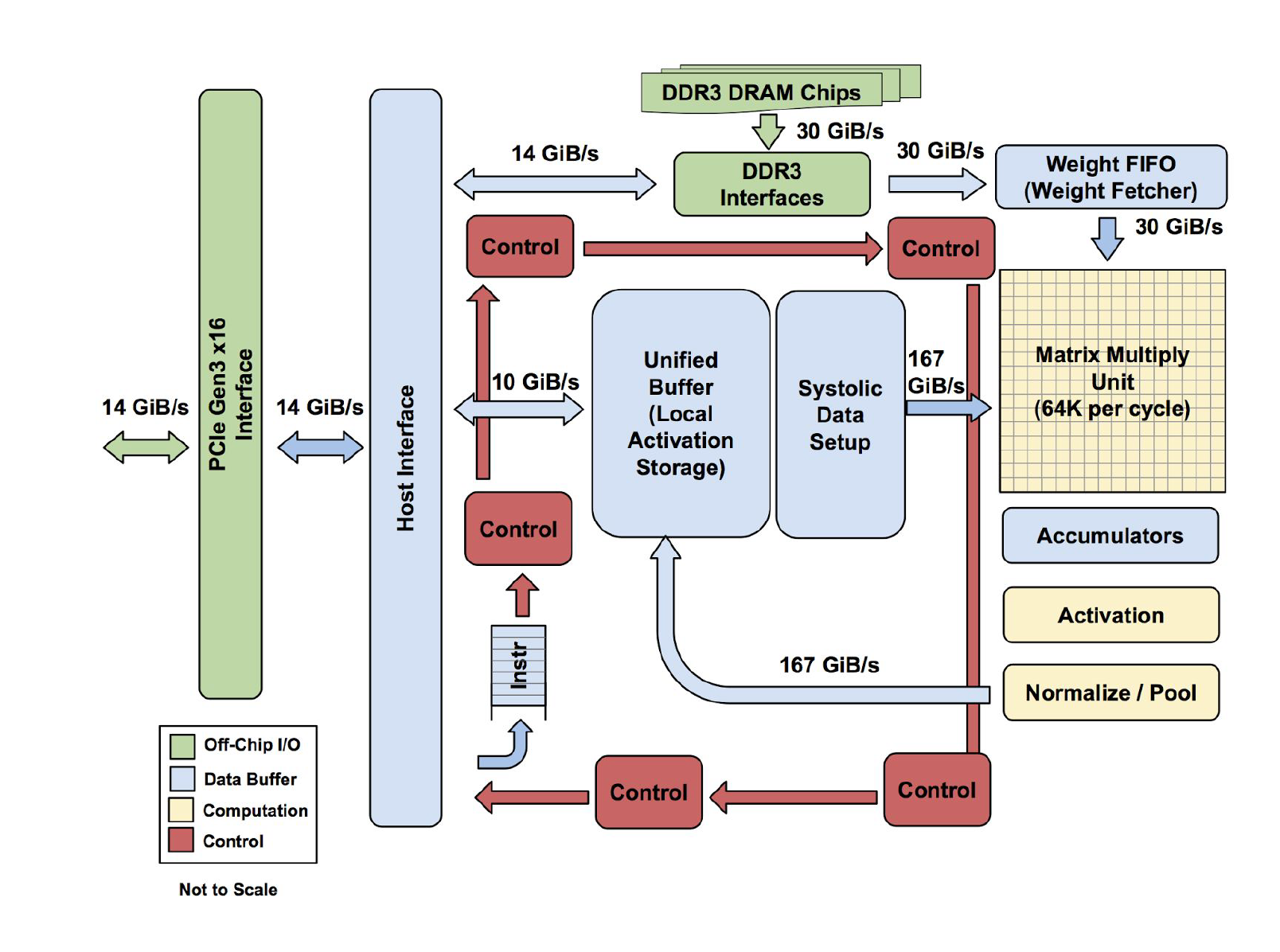

구글의 tpu 그림을 보시면, "Buffer" 라는 키워드가 보이실꺼에요.

이 Buffer 가 거의 대부분 FPGA 에서는 BRAM, ASIC 에서는 SRAM 으로 사용됩니다.

이 Buffer 가 거의 대부분 FPGA 에서는 BRAM, ASIC 에서는 SRAM 으로 사용됩니다.

"Data 를 Buffer 에 넣어주고 빼가고"가 가속기의 핵심입니다. 저의 답은 가속기 설계에서 Buffer 부분이 없으면 안된다, 이 방법 말고는 없죠. 결국 얼마나 효율적으로 R/W 를 해줄 것인가가 설계 경험의 차이라고 답변드리고 싶어요.

FPGA 강의에서는 AXI4-Lite 까지 다뤘습니다. 강의에서도 언급했지만 이는 고속 대량의 Data 를 R/W 하기에 적합하지 않아요. Core 를 쉬지 않고 돌릴 수 있는 Data Flow 를 만들어주시면 됩니다. (AXI4 Standard I/F 를 공부하시면 될 것 같아요. DMA 설계 역량이 필요합니다.)

Q2. LUT의 양은 어떻게 짐작할 수 있나요? 사실 저번 FPGA강의에서 실습한 FC Layer의 곱 연산 수도 꽤 많았던 걸로 기억하는데 그때와 비교해서 이번 CNN Core의 LUT 사용량이 더욱 많은 것 같아서요.

이 부분은 해봐야 알 수 있습니다. FPGA 의 Chip 마다 동일 코드에서 사용되는 Resource 가 다르다, 필요 bit 수, MAC 수 등등 변수가 너무 많아요.

실제로도 작은 부분을 설계 해보고 FPGA 올린 후, 예상 값을 추정합니다.

FPGA 강의에서의 FC Layer 의 Bits 수와 MAC 수, AI HW 강의의 CNN Core 의 Bits 수와 MAC 수 를 고려해보시면 될 것 같아요. 이 부분은 숙제로 남기겠습니다.

즐공하세요 :)

답변 1