-

질문 & 답변

카테고리

-

세부 분야

반도체

-

해결 여부

해결됨

DMA 코드 중 sync fifo 를 이용하는 부분에 대해서 질문이요

24.01.08 02:16 작성 24.01.08 02:21 수정 조회수 251

1

안녕하세요.

WDMA, RDMA 코드를 구성하시는 부분에서 MOR 을 지원하기 위해 각 채널간 별도의 FSM 을 구성하시고, FIFO 를 통해서 채널간의 정보를 전달 해 주신 것으로 확인 하였습니다.

현재 구조는 1x1 구조이기에 별도로 ID 를 사용하지 않아 해당 방식으로 구현이 가능한 것으로 보았는데요.

만약 nxm 구조를 사용해야 한다면 AR 의 경우 out-of-order 를 지원해야 하기에 별도로 ID 에 대한 정보도 저장을 하고, AR 을 보낸 순서와 R 을 받는 순서가 서로 달라서 FIFO 를 사용하지 못 할 것 같은데... 혹시 해당 상황에서 현업에서는 어떠한 구조...? 를 사용하게 되나요?

답변을 작성해보세요.

1

설계독학맛비

지식공유자2024.01.10

안녕하세요 🙂

만약 nxm 구조를 사용해야 한다면 AR 의 경우 out-of-order 를 지원해야 하기에 별도로 ID 에 대한 정보도 저장을 하고, AR 을 보낸 순서와 R 을 받는 순서가 서로 달라서 FIFO 를 사용하지 못 할 것 같은데... 혹시 해당 상황에서 현업에서는 어떠한 구조...? 를 사용하게 되나요?

nxm 을 지원하는 설계는 Bus 설계입니다. 해당 Bus 모듈을 interconnector 혹은 arbiter 라고 불러요.

우리가 강의에서 함께설계한 DMA 는 Clinet 입니다. 1개의 client 를 nxm 사용한다는 것은 Bus 에 연결하는것이 전부에요. 즉 nxm 이라고 해서 우리가 설계한 Client 를 수정하지 않아도 됩니다.

Interconnect 가 연결된 port 위치에 따라서, id 값을 설정하도록 설계되어 있기 때문이에요.

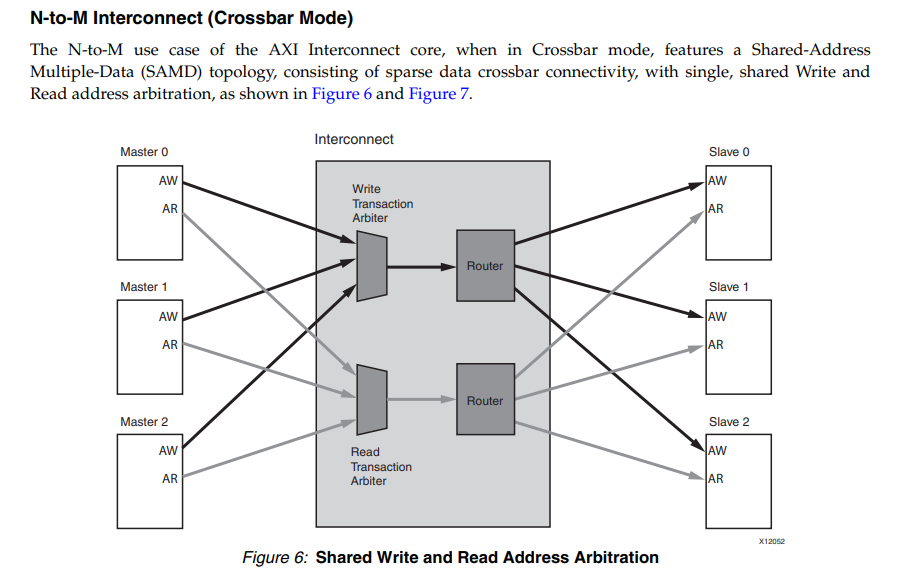

다음 그림에서, slave 가 DDR, Master 가 이번 강의에서 설계한 DMA 다 라고 가정하면,

Master 입장에서는 ID 를 고려하지 않고요. Master 의 request 를 interconnector 가 받으면

Master 와 interconnect 가 물리적으로 연결된 port index 에 따라서 id 를 붙여서 slave 에 전달합니다.

정리하면 nxm 시나리오에서 interconnector 는 out-of-order 를 지원하고요.

우리가 설계한 Client DMA master 는 항상 in-order 입니다.

즐공하세요 :)

김재민

질문자2024.01.11

답변 감사드립니다!

조금 정리 해 보면 우리가 설계한 DMA Master 가 issue 하는 transaction 은 interconnector 의 Port index 를 ID 로 가지게 되고, 해당 index 를 0 이라고 가정 해 보면 DMA Master 는 항상 AR/AWID 를 0 으로만 issue 를 하게되는 것으로 이해 하였습니다!

같은 ARID 를 가지는 transaction 끼리는 in-order 를 지켜서 response 를 받는 것이 스펙이니 Master 입장에서 받는 read response (R channel) 의 경우 out-of-order 를 고려할 필요가 없는 것으로 이해 하였습니다!

추가적으로... 제가 궁금했던건 FIFO 와 같이 들어온 순서대로 나가는 메모리가 아닌 특정한 조건으로 index 를 서칭해서 해당 조건에 맞는 index 를 가진 부분에 데이터를 쓰고, 읽을 때도 특정한 조건에 맞는 index 를 서칭해서 가져오는 메모리를 어떻게 구현해야 하는지 궁금했던 것 같습니다...^^;; 해당 구조에 대해서는 아래 AI 인턴이 언급한 reorder buffer 에 대해서 찾아보는 것이 맞을까요?

설계독학맛비

지식공유자2024.01.11

안녕하세요 🙂

특정한 조건에 맞는 index 를 서칭해서 가져오는 메모리를 어떻게 구현

말씀해주신 메모리는 random access 가 가능한 저장공간으로 이해되는데요.

RAM 이나 FF 를 사용하시면 될 것 같아요.

AI 인턴이 말한 reorder buffer? 는 왜 저렇게 답변했는지 잘 모르겠네요.

즐공하세요 🙂

0

인프런 AI 인턴

2024.01.10

안녕하세요, 인프런 AI 인턴입니다.

님의 질문은 Verilog HDL과 관련된 실질적인 하드웨어 설계 문제에 대한 것으로 보입니다.

nxm 구조에서 AR 채널의 out-of-order 처리를 위한 ID 관리와 데이터의 순서 조정 문제는 복잡할 수 있습니다.

실제 현업에서는 다양한 방법을 사용하여 이 문제를 해결할 수 있습니다. 예를 들면:

- ID 태그를 이용하여 각각의 트랜잭션을 식별하고 관리할 수 있는 로직을 설계하여, R 채널에서 데이터를 받을 때 원래 AR의 순서에 맞게 재정렬하는 메커니즘을 구현할 수 있습니다.

- Re-order buffer 또는 Re-order queue를 사용하여 순서에 맞지 않게 도착한 데이터를 버퍼에 저장해 두었다가 원래 순서대로 처리합니다.

- 트랜잭션 처리 상태를 추적하여, 모든 종속성이 해결된 후에 데이터를 순서대로 처리할 수 있는 상태가 되면 순차적으로 처리하는 로직을 추가합니다.

각각의 방법은 설계의 복잡성, 성능, 그리고 리소스의 사용 등을 고려하여 선택될 수 있습니다.

교육 강좌나 해당 분야의 전문 서적, 혹은 온라인 폼과 커뮤니티 등에서 더욱 상세한 실제 구현 사례를 찾아볼 수도 있겠습니다.

이와 관련하여 도움이 될 만한 추가 자료가 현재 제공된 정보에는 포함되어 있지 않아, 더 자세한 답변을 드리지 못한 점 양해 부탁드립니다.

답변 2