-

질문 & 답변

카테고리

-

세부 분야

반도체

-

해결 여부

미해결

bram 생성 관련 질문 있습니다.

21.08.27 20:57 작성 조회수 419

1

bram을 통해 데이터 다루는 챕터인데 bram을 vivado hls에서 코드로 변환 시킨건가요? vivado에서 block degine에 bram 생성하는 것도 있긴한데 그건 사용자가 코드를 변환 시킬수가 없네요.designe block말고 vi 에디터로 bram을 관련 코드를 다룬다고 한다면 bram을 어떻게 생성할수있는건가요?

설계독학맛비's 실전 FPGA를 이용한 HW 가속기 설계 (LED 제어부터 Fully Connected Layer 가속기 설계까지)

[FPGA 12장] AXI4-Lite I/F 를 사용하여 Register 가 아닌 메모리에 Write / Read 해보기 - 코드리뷰편

강의실 바로가기

답변을 작성해보세요.

1

공기정

2023.12.31

너무 오래전 글이라 너무 뒷북이긴 하지만

vivado에 있는 Templete코드

xilinx_true_dual_port_no_change_2_clock_ram으로 한번 lab12 구현해보았습니다.

테스트벤치 결과 잘 됩니다.

dual_port_2_clock_ram #

(

.RAM_WIDTH (MEM0_DATA_WIDTH ), // Specify RAM data width

.RAM_DEPTH (MEM0_MEM_DEPTH ), // Specify RAM depth (number of entries)

.RAM_PERFORMANCE ("LOW_LATENCY" ), // Select "HIGH_PERFORMANCE" or "LOW_LATENCY"

.INIT_FILE ("" ) // Specify name/location of RAM initialization file if using one (leave blank if not)

)

dual_port_2_clock_ram_inst

(

// Core

.addra ( ), // Port A address bus, width determined from RAM_DEPTH

.ena ( ), // Port A RAM Enable, for additional power savings, disable port when not in use

.regcea ( ), // Port A output register enable

.wea ( ), // Port A write enable

.douta ( ), // Port A RAM output data, width determined from RAM_WIDTH

.dina ( ), // Port A RAM input data, width determined from RAM_WIDTH

.clka ( ), // Port A clock

.rsta ( ), // Port A output reset (does not affect memory contents)

// Ctrl

.addrb (mem0_addr1), // Port B address bus, width determined from RAM_DEPTH

.enb (mem0_ce1 ), // Port B RAM Enable, for additional power savings, disable port when not in use

.regceb (mem0_ce1 ), // Port B output register enable

.web (mem0_we1 ), // Port B write enable

.doutb (mem0_q1 ), // Port B RAM output data, width determined from RAM_WIDTH

.dinb (mem0_d1 ), // Port B RAM input data, width determined from RAM_WIDTH

.clkb (mem0_clk1 ), // Port B clock

.rstb (mem0_rst1 ) // Port B output reset (does not affect memory contents)

);

이런식으로 instanciation 했구요

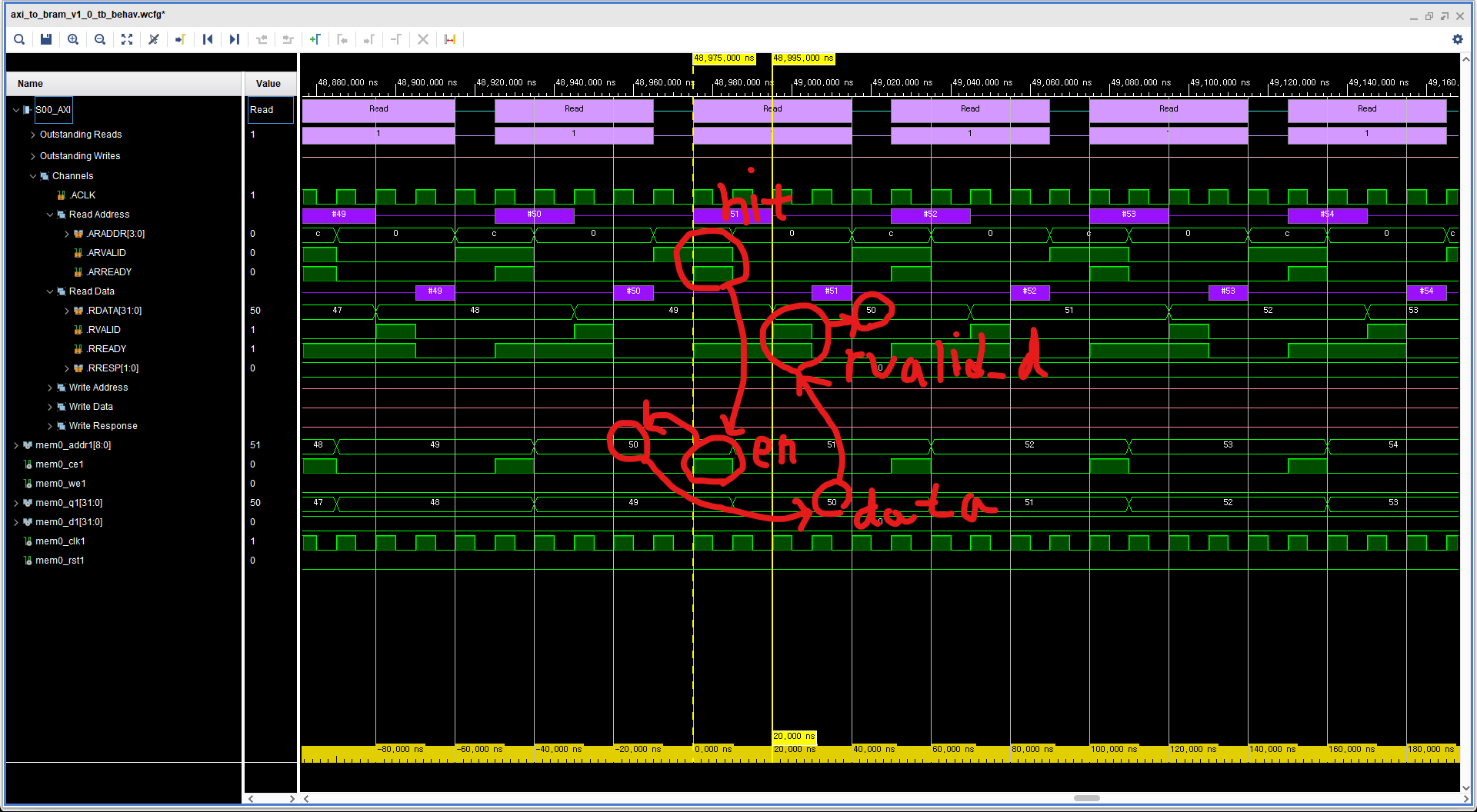

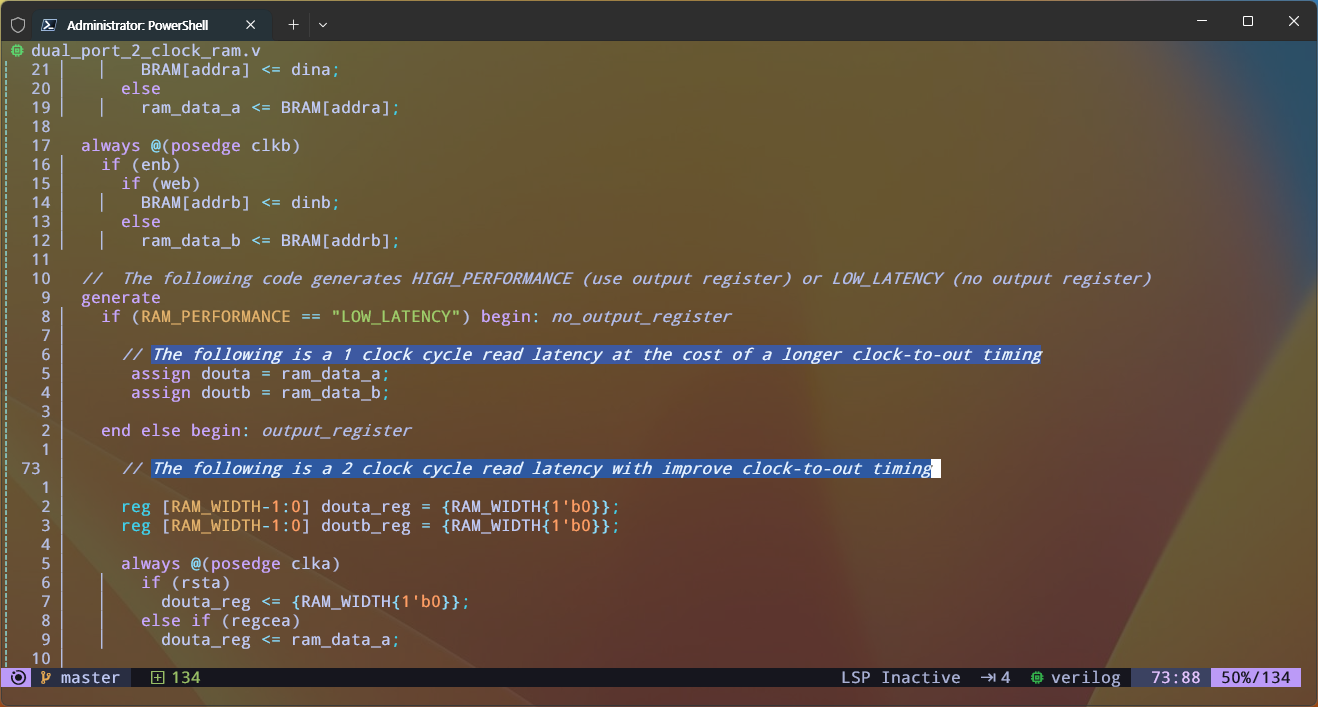

RAM_PERFORMANCE의 default값인 HIGH_PERFORMANCE로 하지 않고 LOW_LATENCY로 한 이유는

HIGH_PERFORMANCE로 하였을 경우에는 2클럭 더 늦게 나옵니다.

low latency일 경우에는 1클럭 딜레이지만 high performance일 경우 2클럭 딜레이라고 코드에 써 있습니다.

제 프로젝트랑 소스코드입니다. 프로젝트 들어가서 run simulation누르시면 볼 수 있습니다.

https://drive.google.com/file/d/1hljaATJFlQ2pbz08046E_j8vVR0-XFAh/view?usp=sharing

필요하신분들 참고 부탁드립니다!!

설계독학맛비

지식공유자2023.12.31

공기정님!! 오래간? 만이네요 ㅎ 이렇게 정리해 주셔서 감사합니다.

새해를 앞두고 이런 선물을, 복 받으실 꺼에요.

추가로 적자면

High performance == High frequency 이기 때문에, reg to reg delay 를 최소화 하기 위해서 2 cycle 이 되었고요. FPGA 상에서 제 경험상 5 cycle 이상도 해본 적이 있어요. (Routing delay 최소화)

올 한해도 고생 많으셨고요. 새해 복 많이 받으세요!!

공기정

2024.01.01

HIGH_PERFORMANCE는 주파수 높은 경우 타이밍문제 줄일려고 쓰는거 같다고 그렇게 예상하고 있었는데 진짜였네요!! 감사합니다!!

맛비님 덕에 대학교 3학년을 무사히 마치게 되었습니다. (특히 디지털 시스템 수업에서 맛비님의 덕을 많이 봤습니다.)

올해에는 더 성장할수 있도록 최선을 다하려고 합니다.

맛비님도 2023년 동안 매우 고생하셨구

새해복 많이 받으시고 올해엔 원하는 바 다 이루시길 바랍니다!!

1

0

설계독학맛비

지식공유자2021.08.27

안녕하세요 :)

제가 전달드린 코드는 vivado hls 에서 변환해서 만든게 맞아요.

직접 FPGA 에서 implementation 이 가능한 BRAM .v 코드를 만들고 싶다고 하시면..

다음 방법을 시도해 보시는 건 어떨까요?

저도 처음해보는데, 궁금해서 찾아봤습니다. 결론은 잘됩니다 :)

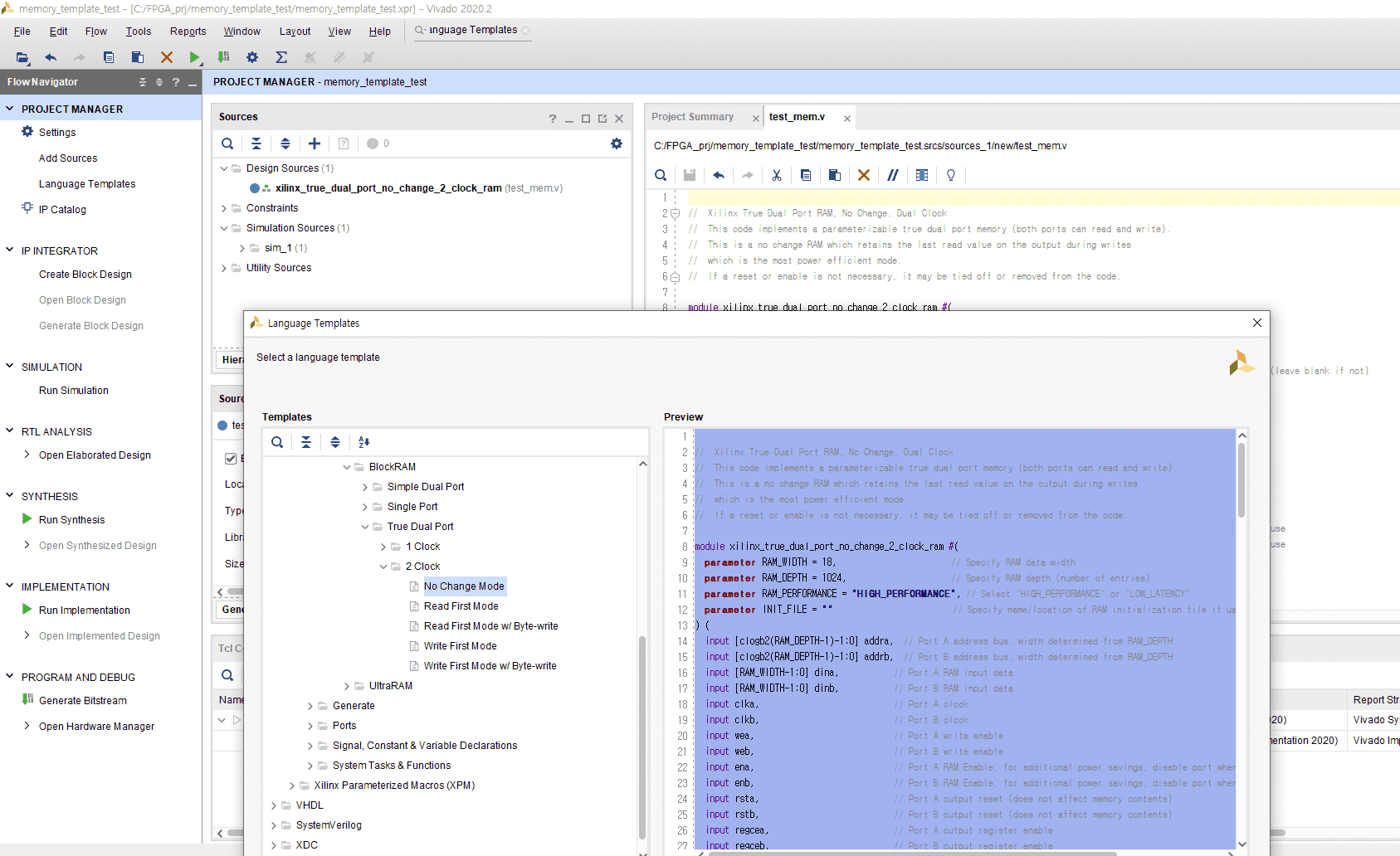

Template 코드 확인

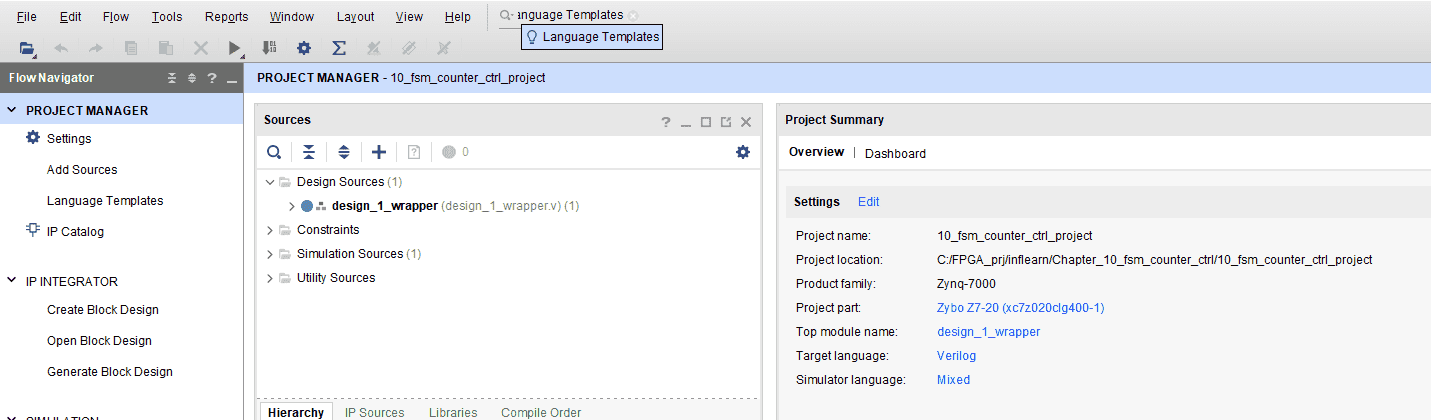

1. 먼저 vivado tool 에서 프로젝트 아무거나? 하나 여시구요. (저는 chapter 10 을 열었습니다.)

2. 그 상태에서 위의 돋보기에 "Language Templates" 이라고 검색해서 눌러주세요

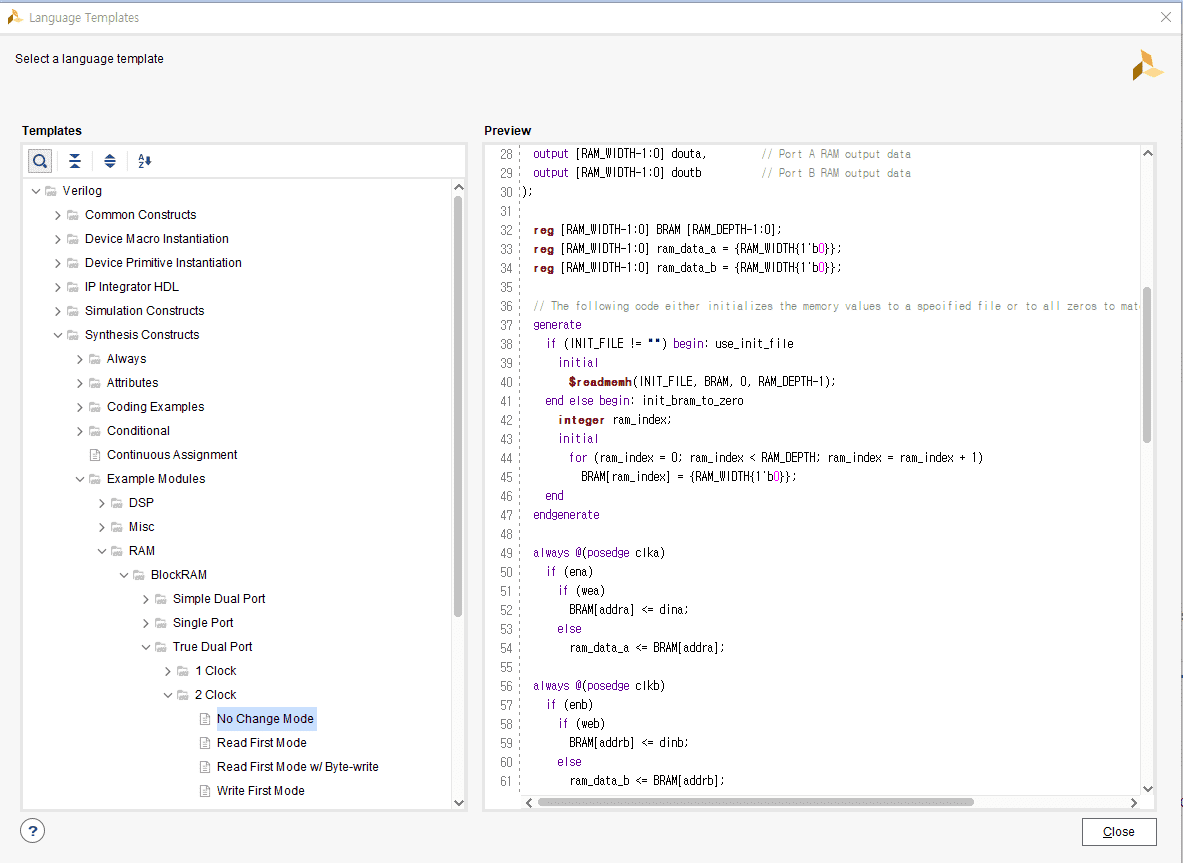

3. Veriog -> Synthesis Constructs -> Example Modules -> RAM -> BlockRAM -> 원하시는 메모리 코드 선택

4. 원하시는 RAM 선택 후, 우측에 있는 코드를 복사해서 사용

너무 성의 없어보여서, 제가 아주 간단하게 Test 해봤습니다.

1. 프로젝트를 하나 만듭니다.

2. template code 메모리를 .v 코드로 복 붙 했습니다.

3. synthesis 눌렀습니다.

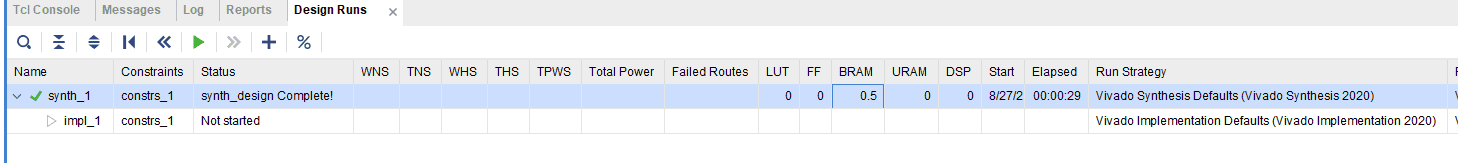

4. 결과 확인

BRAM 0.5 로 resource 잡히신거 보이시나요? 잘되네요 ㅎ

참고로 implementation 을 통한 bitstream 은 당연히 이 예제에서 안되는건 아시죠?

여기있는 Templete 코드들을 응용하시면 원하는 답이 되지 않을까 생각합니다. (다양한 모듈들이 있네요)

음..;;; 제가 Test 했던 project 파일 첨부파일로 안올라가네요...?

링크로 걸어드립니다. 확인해보세요.

원하시는 답변 맞나요....??!

즐공하세요 :)

답변 3