-

질문 & 답변

카테고리

-

세부 분야

반도체

-

해결 여부

해결됨

HDL 14장 실습관련 질문 있습니다.

23.04.10 02:16 작성 23.04.10 03:21 수정 조회수 311

1

안녕하세요 맛비님 14장 8승기 설계 후 Simulation 과정에서 의문점이 들어 질문 드리게 되었습니다.

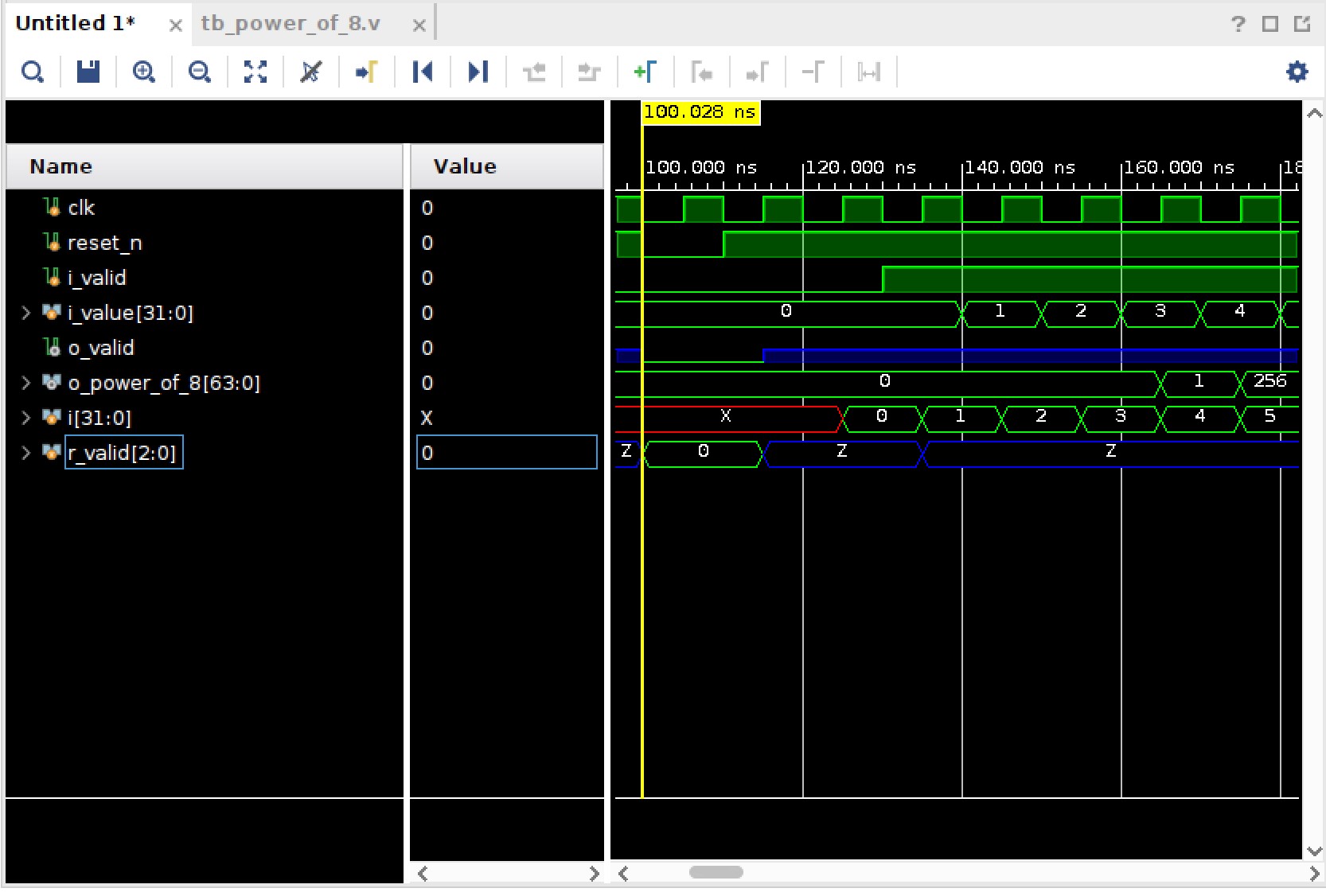

1) 우선 simulation결과는 위와 같은데, r_valid, o_valid가 0으로 초기화(@100ns)는 되었는데 그 다음 rising edge부터 Z로 나오네요.

제 코드가 문제가 있어서 이렇게 나오나 싶어서 맛비님의 코드로 다시 돌려봐도 이렇게 나옵니다. 혹시 다른 질문 내용 중 문제점을 찾을 수 있나 확인해봤는데, high impedence Z는 signal이 연결되지 않은 거라고 답변해 주셨는데, 올려주신 코드대로 simulation을 돌렸는데 왜 이렇게 되는 건지 이유가 궁금합니다.

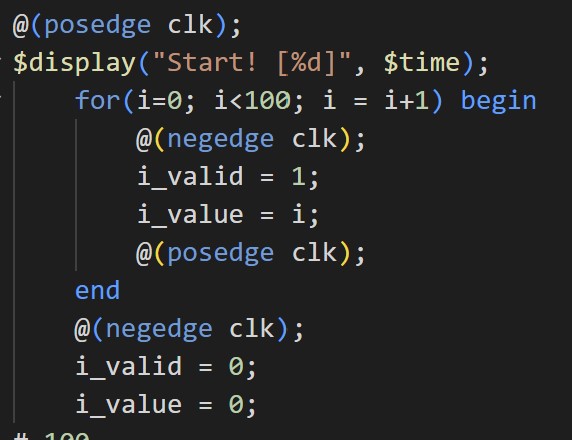

2) Testbench의 Initial Block에서

0부터 99까지의 수의 8승을 test하기 위하여 위 코드를 사용하셨는데,

@(posedge clk);

부분이 있는 이유가 뭔지 궁금합니다. Clock의 positive edge에서 반응하긴 하지만, 그 다음에 뭔가를 하지 않고 바로 다음 loop를 돌거나, for문을 탈출하는데, 결국 이 부분이 하는 역할이 뭔지 궁금합니다. @(posedge clk); 이후에 지시하는 바가 없기 때문에 결국 sensitivity list를 통해서 들어왔다 해도 없는거랑 똑 같은 것 아닌가요? 아니면 다음 negedge가 오기 전에 posedge까지 해당 loop를 유지하기 위해 있는 건가 싶기도 했는데 그런 의미인가요? 어떤 의미가 있는 부분인지 여쭤보고 싶습니다!

3) 강의 듣다가 문득 생각이 난 것인데, 왜 Linux(WSL)환경에서 설계를 하는게 중요한가요?

결국 synthesis까지 가면 Linux기반의 EDA tool을 쓸 수밖에 없어서 그런건가요? script기반의 자동화에 용이해서 그런가요? 어떤 점에서 rtl 엔지니어들이 대부분 현업에서 Linux기반으로 작업을 하시는데 큰 이유가 되는 것인지 궁금합니다. 중요하다고 말씀은 하셨는데, 아직 체감이 되는 단계는 아니어서요..

긴 글 읽어주셔서 감사합니다. 강의 항상 잘 듣고 있습니다 :)

답변을 작성해보세요.

1

설계독학맛비

지식공유자2023.04.10

안녕하세요 :)

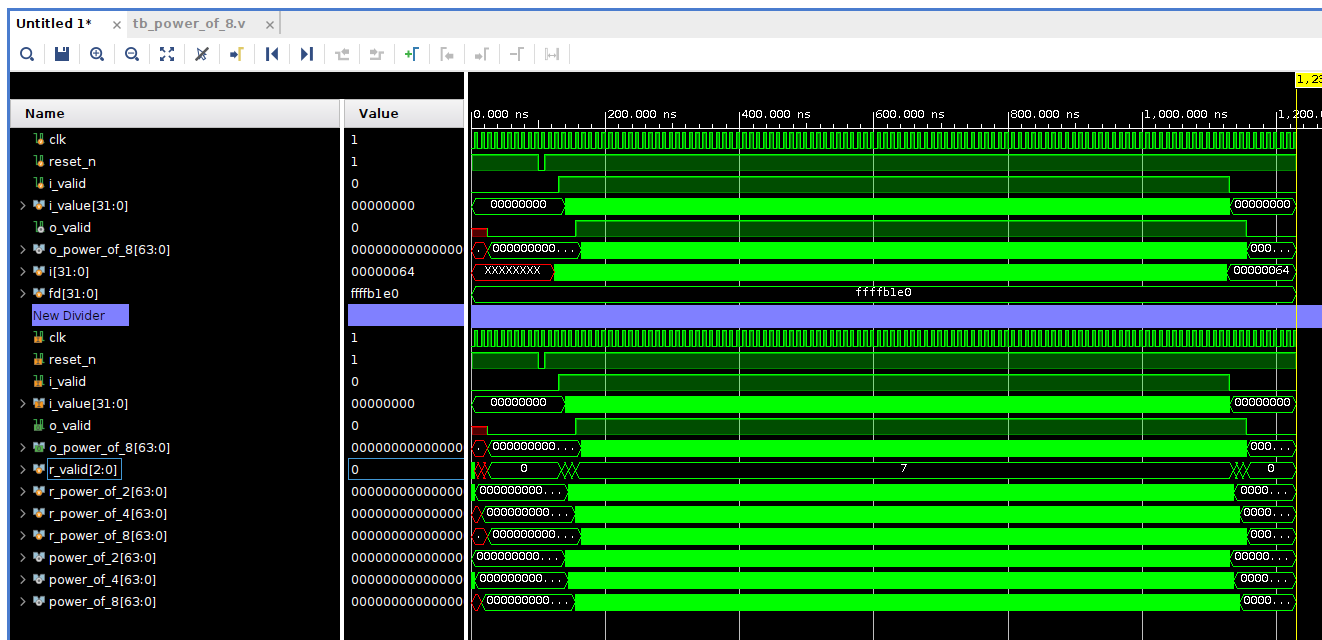

A1. 제가 직접 돌린 waveform 인데, 'z' 은 발견되지 않았습니다.

제가 드린 코드 그대로 사용한 것이 맞는지 확인해보실 수 있을까요? (testbench 라던가, dut 라던가.., 무언가 실수가 있으셨을 가능성이 있어보여요)

A2. 아 그 부분은 말씀 해주신게 맞습니다.

posedge 부분은 빼셔도 될 것 같아요. (현 코드에서 역할은 없습니다.)

A3. 이 강의를 만들때, 굳이?! 힘들게 리눅스 환경을 드리려고 한 이유가 있습니다.

linux 를 굳이 드린 이유는 현업에서 쓰니까 라는 이유에서이고.

현업에서 왜쓰는가? 는 알고계신 EDA Tool 이 리눅스에서 제공되니까. 그 이유는 큰 이유입니다.

칩 설계 tool 없이 아무것도 할 수 없으니까요. :)

체감이 안된다는 저도 공감합니다. 예전에는 script 기반의 어쩌고 저쩌고.. 어떤게 편하다. 이런식으로 설명을 해보려고 했는데, 직접 경험해 보지않는한 제가 글로 적어도 와닿지 않을것이고...

그리고 조금만 노력하면 제가 적어보려고 했던 장점들은 사실 어느 OS 건 다 됩니다.

자기가 가장 편한 환경을 쓰면 되겠습니다. 하.지.만! 리눅스는 배워두셔야 현업에서 도움이 되실겁니다.

개인적인 생각으로는,

회사에서 리눅스를 이제까지 많이 써왔던 이유는....?!!! (리눅스는 무료입니다, 무료치고 안정적이죠. 생태계도 발전이 잘 되어왔고) -> 그런 무료OS 라는 "그 어떤 모든것을 상쇄할 수 있는 최고의 장점"으로 인해서. 모든 EDA Tool 을 리눅스에서 돌아가게 만들지 않았을까는 뇌피셜이 있습니다 ㅎ

즐공하세요 :)

답변 1