설계독학맛비's 실전 Verilog HDL Season 2 (AMBA AXI4 완전정복)

설계독학맛비

₩385,000

중급이상 / Verilog HDL, FPGA, amba, 임베디드

4.9

(49)

설계독학과 함께 Verilog HDL을 이용하여 SoC Bus의 기본이 되는 AMBA AXI4 설계와 VIP 검증 경험을 쌓아봅시다!

중급이상

Verilog HDL, FPGA, amba

현업자와 함께 Verilog HDL을 이용하여 비메모리 반도체 설계의 기본 지식과 경험을 쌓아봅시다.

한화시스템/ICT

임직원들도 이 강의를 듣고 있어요!

한화시스템/ICT

임직원들도 이 강의를 듣고 있어요!

먼저 경험한 수강생들의 후기

5.0

한진규

"학생이라면 처음엔 가격이 부담될 수 있지만, 들을수록 지불한 가격 이상의 가치가 있는 강의" Pipeline까지 수강 완료했습니다. 빨리 좋은 수강평을 남기고 싶은 마음을 참을 수 없어 미리 작성합니다. 졸업예정자인데 하반기 대기업 예비합격으로 멘탈이 나간 상태였습니다. "직무에서 우대하는 FPGA/Verilog라도 공부해서 다음 지원때 어필하자"라는 가벼운 마음으로 수강을 시작했지만, 정말 이 분야에 흥미를 가지게해준 강의입니다. (+귀에 쏙쏙 박히는 설명과, 어렵지만 끈질기게 매달리며 하나씩 이해해가는 과정은 정말 흥미롭습니다.) 빨리 완강하고 피나게 연습하여 스펙만 보고 직접 설계할 수 있는 수준에 다다르고 싶습니다. 그 후 빨리 fpga를 이용한 다양한 실습과 프로젝트도 진행해보고싶네요. 양질의 강의 제공해주셔서 감사합니다 맛비님.

5.0

dos12345

5점 줄 수 밖에 없는 강의였습니다. 내용도 자세하게 설명해주시고 혹시나 모르는 부분이 있어서 질문하면 답변도 빠르게 해주셔서 너무 좋았습니다(물론 구글링이나 다른 수강생들의 질문 참고하면 웬만한 문제는 다 해결됩니다.). 특히 맛비님의 컴퓨터 환경과 제 컴퓨터 환경이 달라서 vivado 설치할 때 힘들긴 했지만 빠른 피드백 덕분에 무사히 설치할 수 있었습니다. 그리고 새로운 버전의 vivado 설치영상을 다시 올리신 것 같던데 이런 부분 너무너무 좋습니다. 앞으로도 건강하시고 오래오래 강의해주세요!

5.0

움직이는YM

Verilog 와 비메모리 설계에 관심이 있으신 분들은 꼭 한번 수강해보는 것을 추천드리는 강의입니다 맛비님께서 사소한 질문도 정말 잘 받아주시고 피드백도 빨라서 수업 듣는 것에는 불편함이 없었습니다 하지만 이런 분께는 추천하지 않지 않습니다 Verilog 문법의 v도 모르시는 분입니다. 제가 처음에 이런 상태로 수강을 했다가 verilog 문법에 대한 설명이 거의 나오지 않아 당황했던 기억이 있습니다. 맛비님도 대략은 설명해 주시지만 기본적인 verilog 문법 정도는 알고 들으셔야 도움이 됩니다 반대로 학교에서 verilog 수업을 한 번은 들으셨던 분, 개인적으로 verilog를 한 번 공부해본적이 있으셨던 분은 정말 도움이 많이 될 것이라고 생각합니다. 학교에서나 혼자 공부하면서 배울 수 없었던 핵심적인 내용만을 잘 다루고 계십니다. 종합적으로 강추하는 강의입니다.

비메모리 반도체 설계 기본지식

학교에서 배울 수 없는 현업자가 설계한 Verilog HDL 설계 및 검증 방법

FPGA를 시작하기 위한 설계 기초 지식

현업에서 필요한 설계지식! (멀뚱거리지 마세요)

비메모리 설계 엔지니어가 알려주는

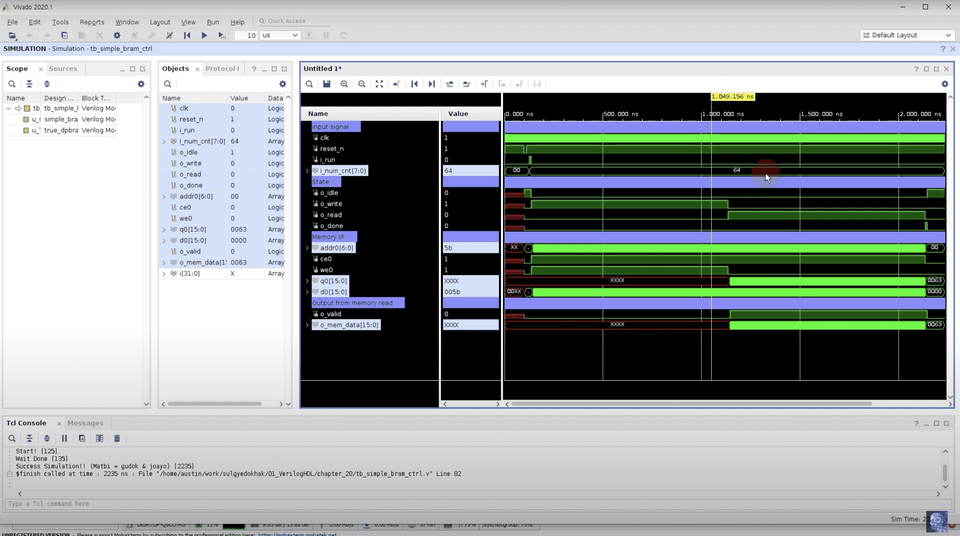

실전 Verilog HDL: Clock부터 Internal Memory까지!

설치가 가장 어렵습니다.

해당 환경은 여러분들의 설계인생에 도움이 되리라 의심치 않음으로, 설치에 성공하신 분들께서 수강신청 부탁드립니다. (설치 영상은 무료 오픈중)

현업자인지라, 시간상 모든 버전을 서포트하기 어려워서

강의에서 사용한 설치 영상의 버전을 맞춰서 설치 부탁드립니다. vivado 2020.1 ~ vivado 2022.2 추천

tool 은 tool 입니다. 여러분들에게 전달해드릴 설계지식과 코드는 tool 버전에 영향을 받지 않습니다.

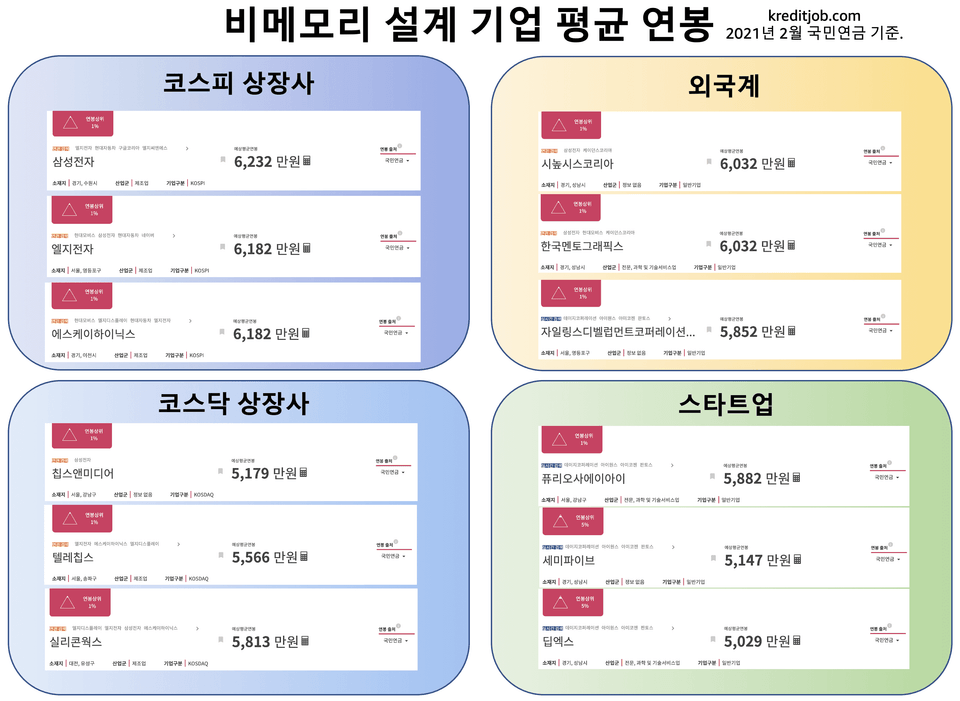

아시다시피 한국은 메모리 반도체 강국입니다. 비메모리 반도체 강국이 아닙니다.

정부와 기업이 많은 투자를 하고 있고, 실제로 국내에 많은 설계 회사들이 있습니다.

취업사이트인 원티드, 링크드인, 사람인 등등 "Verilog HDL" 키워드를 검색해보세요.

전 세계 많은 회사들이 반도체 설계 엔지니어를 찾고 있습니다.

가고싶은 회사가 있으신가요? 그 회사의 연봉을 검색해보세요.

크레딧잡에서 비메모리 설계관련 회사들을 예를 들면, 국내 기업 평균 연봉상위 1%입니다.

받는 만큼 공부해야하는 직업이고, 쉬운길이 아닙니다.

필독문서를 읽어주셔서 진심으로 감사합니다.

여기까지 읽으셨으면 제 강의를 수강하지 않으셔도,

여러분들은 훌륭한 설계 엔지니어가 되실거라 확신합니다.

선택은 여러분들의 몫 입니다.

여러분들을 현업에서 만나 뵙기를 기대합니다.

감사합니다. 맛비 드림.

학습 대상은

누구일까요?

대학교 전자과 2~4학년 수준 지식을 갖추신 분.

Verilog HDL language 를 공부해보신 분

설계 실무를 경험하고 싶으신 분

비메모리 설계분야로 취업을 희망하시는 분

선수 지식,

필요할까요?

C 언어

Verilog HDL

4,319

명

수강생

373

개

수강평

1,311

개

답변

5.0

점

강의 평점

5

개

강의

현) Global Top5 Fabless기업에서 HW IP 설계하고 있습니다.

세상에 없던 그리고 여러분들의 현업 생활에 도움이 되는, "진짜 반도체 설계 실무 강의"를 만들고 있습니다.

설계독학 로드맵과 함께 여러분들의 실력을 키워보아요.

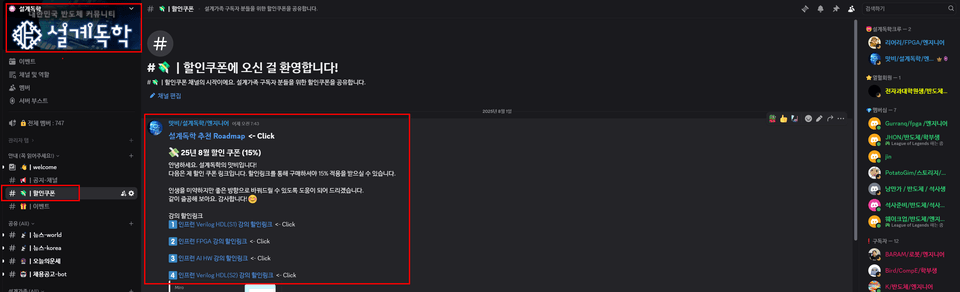

여러분들과 소통하기 위한 설계독학 커뮤니티 를 운영하고 있습니다.

(커뮤니티에 가입하셔서, 15% 할인쿠폰도 받아보아요.)

함께 즐공하고 성장해요!

전체

43개 ∙ (7시간 34분)

해당 강의에서 제공:

전체

172개

5.0

172개의 수강평

수강평 2

∙

평균 평점 5.0

5

설치하는데 꼬박 하루 걸리고 지금 수강신청하여 듣기 시작하였지만, 이렇게 언제든지 들을 수 있는 verilog 관련 강의를 올려주신점 정말 감사드립니다. 이런 강의는 2~30만원이 절대 아깝지 않다고 생각이 들고, 다음 강의도 꼭 들을 예정입니다. 혹시라도 FPGA로드맵 강의를 전부 찍어주신다면 저도 끝까지 달리도록 하겠습니다.!!

수강평 진심으로 감사드립니다! 현업하고 병행하느라 계획한 로드맵이 나오는 과정이 조금 더디긴 해요 ㅠ 그래도 좋은 퀄리티를 위해 최선을 다하고 있으니까 다음 강의도 재밌게 들어주세요. FPGA 는 이미 나온상태라 같이 들으시면 역량에 배가 되시리라 생각됩니다. 즐공하세요!

수강평 1

∙

평균 평점 5.0

5

IDEC나 SW-SOC같은 외부수업도있지만, IDEC같은경우 교수님둘이 많은 내용을 함축적으로 전달할려고해서 이해가 않되는 경우가 많음. 그렇다고 다시보기할수도없고. SW-soc같은경우는 시즌제? 강의 신청으로하는데 ( 온라인 강의같은경우 예전에 했던거 반복해서 틀어주는데 왜 수강신청같은걸 넣는지 모르겠음) 겁나 취업연계강의 아니면 겁나 간단한거함 솔직히 책보는게 더 도움됨. 이분 강의는 현직자입장에서 예제코드기반해서 설명해줘서 나름 이해도 되고 FPGA설계 할때 도움진짜 많이됨 강추!. 감사합니다 맛비님

와.. 수강평 감사합니다 :) 부족한 부분이 있었겠지만 (없다면 말이안되죠) 잘 봐주셨다니 다행입니다. 앞으로도 학교에서 알려주지 않는 내용들을 다뤄보도록 하겠습니다. (학교 수업이 중요하지 않다는 뜻은 아니에요 ㅎ) 즐공입니다 :)

신규가입 25% 할인

월 ₩37,124

5개월 할부 시

25%

₩247,500

₩185,620