(질의응답 History 3.) always(*) 문에 관하여

어느 블로그에 Verilog HDL 문법 중, always(*) 를 쓰면 비메모리 설계 인생이 망할? 것 처럼 적어놓으신 경력자 분이 계시더군요.

그 글 때문인지, 여러번 질문을 받았구요. 제 답변을 적어봤습니다.

IEEE 에서 쓰라고 만든 문법이구요.. 결론은 제대로 알면 써도 됩니다.

꼰대력을 발동해서 더 적자면!!!

지식은 반드시 걸러서 받아드리셔야 합니닷! 물론 제가 알려드리는 내용이 틀릴 수 있어요, 제가 틀린 부분을 찾아내셨다면, 여러분들이 더 뛰어난 것이니 좋아하시면 됩니다 :)

추가로 어디가 틀렸는지 알려주시면 정말 감사하겠습니다 ㅠ.ㅠ

Q.

FSM으로 uart 설계중이었는데 그 보통 state 컨트롤시 always(*) 조합회로로 컨트롤을 하는데 이거에 대한 글을 쓴 블로그를 보았는데요. 진짜 always(*)문 안에 레지스터를 쓰게되면 실제 양산시에 큰 문제가 생기나요?

갑자기 궁금해서 여쭤봅니다. (글 링크는 안알랴줌... 괜히 볼까봐..;;;;)

맛비's A.

예전에 어떤 학생도 이분 글로 물어보던데.. 음..

개인적으로 그렇게 동의하는 글은 아니에요. 다 틀렸다는 아닌데.. 공격적인 말투하고.. 본인말이 무조건 맞다 식의 문장이 조금 걸릴 뿐.. (다 맞지 않지만요)

저희 회사 사장님 및 선배들.. 다 망했겠네요..ㅎ 저도 이번생의 설계 엔지니어는 망했군요.. ㅠㅠ

always(*) 문 이 문법은 쓰세요. Verilog 2001 정식 문법입니다.. 왜 그걸 이렇게 표현했는지.. 이거 Combinational Logic 입니다......

저분 글에 반박하면

<저분 글 발췌>

always@(*)

어떤 양아치가 이런 문장을 책에 처음 썼는지 모르겠으나 이 후로 나온 책들이 모두 이런 문장을 사용했다. 이 문장은 일단 컴비네이셔널 로직을 register 로 선언하게 된다. register 로 선언되면 메모리가 된다. 컴비네이셔널 로직에 플립플롭이나 래치가 되면 시그날 처리가 애매해 진다.

IEEE 라고 하는 양아치...? 가 만들었구요.. ㅠ.ㅠ

reg 로 선언했다고 해서 register 아니구요. Combinational Logic 으로 만들어집니다. (이 한줄이면 충분해요.)

<저분 댓글>

당연히 reg 로 선언해서 컴비네이셔널 로직으로 합성이 가능하죠. 그런데 그게 경우에 따라 레지스터가 될수도 있잖아요. 컴비네이셔널 로직을 설계하는데 만에하나 레지스터나 래치같은 형태로 합성되면 회로에 재앙이 발생합니다.

코딩 스타일로 충분히 막을 수 있는 재앙을 왜 잘못될 확률이 있는 방식으로 설계하냐는 말이죠.

경우에 따라서.. 가 어떤 경우인지는 모르겠는데, 문법을 정확하게 모르면 안쓰는 것이 좋다 의 뉘앙스로는 공감합니다.

하지만 저는 써요 ![]()

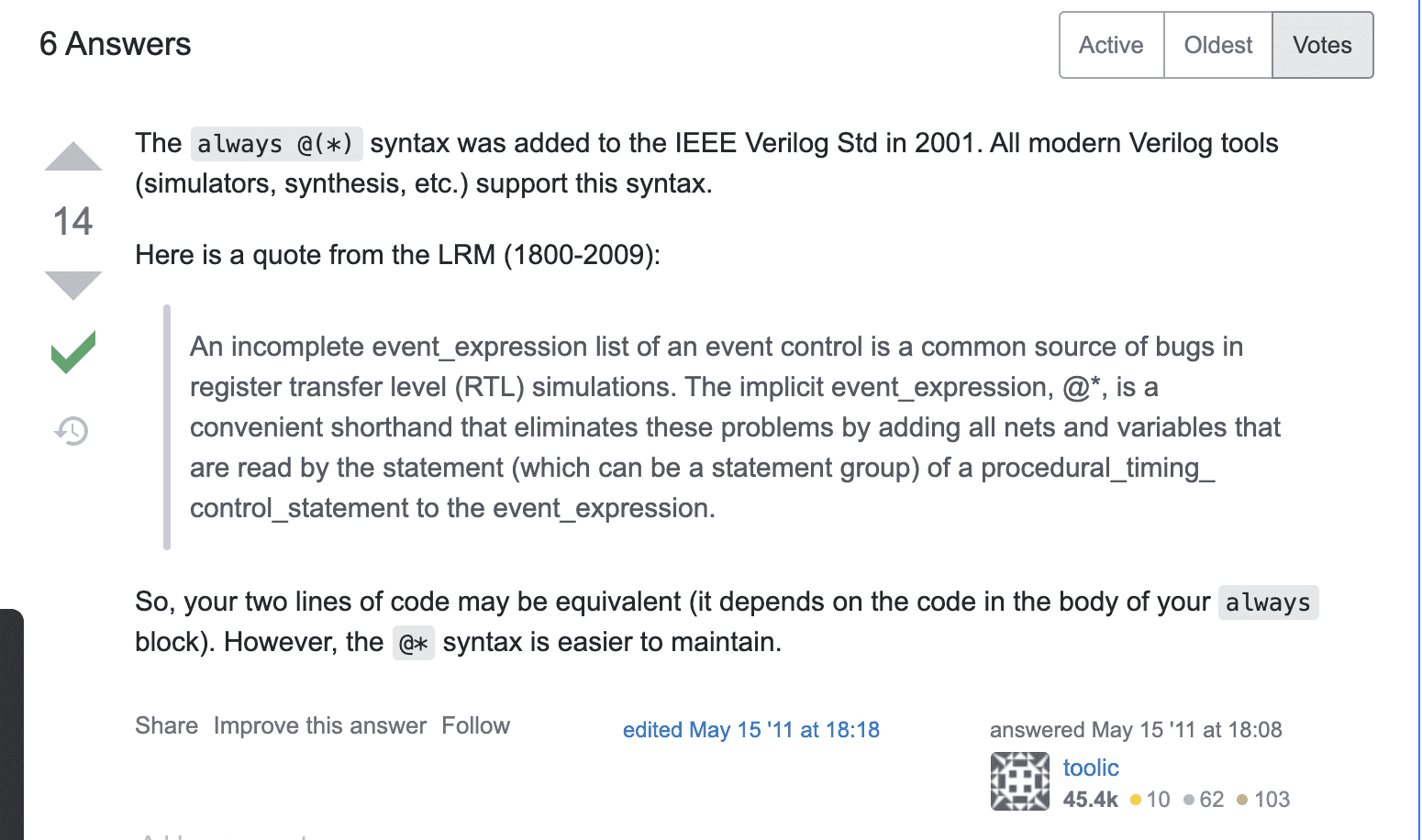

https://stackoverflow.com/questions/6009998/verilog-always-block-using-symbol

여기의 답변이 저의 생각하고 일치합니다.

댓글을 작성해보세요.