-

질문 & 답변

카테고리

-

세부 분야

반도체

-

해결 여부

미해결

안녕하세요 맛비님 simple_bram_ctrl.v 모듈에 질문이 있습니다!

24.03.28 16:23 작성 조회수 68

1

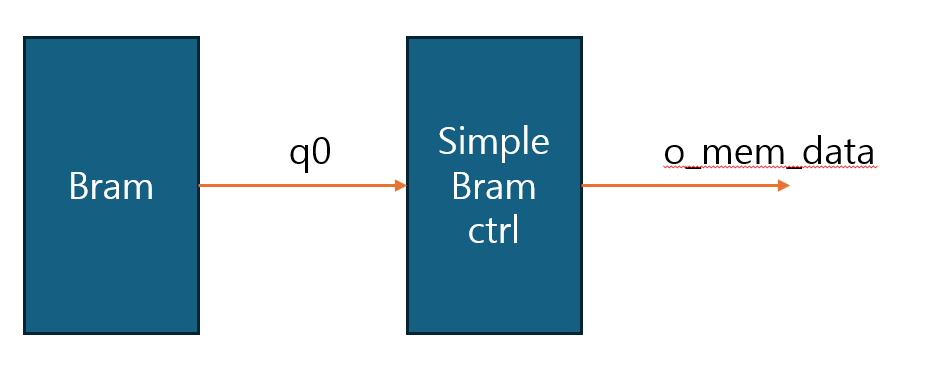

안녕하세요 맛비님 simple_bram_ctrl.v 모듈에 질문이 있습니다! memory I/F input/output port 정의하는 부분에서 q0를 input으로 두셨는데 마지막 줄에 보니까 output port o_mem_data 에 input port q0를 할당하셨더라고요. 이렇게 해도 코드 상 문제가 없을까요?

=================

현업자인지라 업무때문에 답변이 늦을 수 있습니다. (길어도 만 3일 안에는 꼭 답변드리려고 노력중입니다 ㅠㅠ)

강의에서 다룬 내용들의 질문들을 부탁드립니다!! (설치과정, 강의내용을 듣고 이해가 안되었던 부분들, 강의의 오류 등등)

이런 질문은 부담스러워요.. (답변거부해도 양해 부탁드려요)

개인 과제, 강의에서 다루지 않은 내용들의 궁금증 해소, 영상과 다른 접근방법 후 디버깅 요청, 고민 상담 등..

글쓰기 에티튜드를 지켜주세요 (저 포함, 다른 수강생 분들이 함께보는 공간입니다.)

서로 예의를 지키며 존중하는 문화를 만들어가요.

질문글을 보고 내용을 이해할 수 있도록 남겨주시면 답변에 큰 도움이 될 것 같아요. (상세히 작성하면 더 좋아요! )

먼저 유사한 질문이 있었는지 검색해보세요.

잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

==================

설계독학맛비's 실전 Verilog HDL Season 1 (Clock부터 Internal Memory까지)

[HDL 20장] Internal Memory Interface 에 대해 이해해보자 (FPGA 의 BRAM 을 이해하기 - 실습편)

강의실 바로가기

답변을 작성해보세요.

0

설계독학맛비

지식공유자2024.03.28

안녕하세요 🙂

위 그림과 같습니다.

위 그림과 같습니다.

현업에 가시면 모듈의 input 을 바로 output 에 assign 하는 행위를 "lint" 관련 tool 을 이용해서 잡을 수 있고요.

이 부분은 우려하시는 대로 문제가 될 여지가 있어요.

하지만 설계자가 보장한다면, 사용가능합니다.

실제로 FPGA 에 올려서 동작시켜본 코드에요. (zynq 에서 100 MHz 정도 까지 합성되는 것으로 기억나요)

해당 예제 코드는 Timing 이슈를 제가 보장했고요. 그래서 사용하셔도 됩니다.

하지만 현업에서 문제를 삼는다고 하시면, 직접 판단하시어 수정하셔도 되겠습니다.

즉 따라서 이 문제는 상황에 따른 선택이 있을 뿐 정답은 없습니다.

즐공하세요 🙂

====================

어떤 문제가 있는지는 제가 GPT4 에 물어보았고요. (GPT 는 현업을 모르지만, 기본적인 이론은 답변을 잘해줍니다. 제 생각도 같아요. )

참고 부탁드립니다.

모듈의 입력(input)을 바로 출력(output)에 할당(assign)하는 행위는 간단해 보일 수 있지만, 디지털 회로 설계에서는 몇 가지 고려해야 할 문제가 있습니다. 이러한 행위가 문제를 일으킬 수 있는 주요 이유는 다음과 같습니다:

1. 신호 지연(Delay)

지연 문제: 모든 디지털 회로 요소는 신호를 전달하는 데 있어 일정한 지연을 가집니다. 입력 신호를 바로 출력 신호에 연결하면, 이 지연이 명시적으로 관리되지 않습니다. 실제 하드웨어에서는 이러한 지연이 예측하지 못한 타이밍 문제를 일으킬 수 있습니다.

동기화 문제: 특히 클럭 동기화 디자인에서 입력 신호를 직접 출력에 연결하면, 클럭 도메인 간의 올바른 동기화 없이 신호가 전달되어 메타스테이블 상태(metastable state)를 유발할 수 있습니다. 이는 시스템의 안정성과 신뢰성을 저하시킬 수 있습니다.

2. 신호 무결성(Signal Integrity)

무결성 문제: 입력 신호를 바로 출력에 연결하는 것은 신호의 무결성을 저하시킬 수 있습니다. 예를 들어, 긴 전선이나 고속 신호의 경우, 신호 반사(reflection)나 감쇠(attenuation)와 같은 현상이 발생할 수 있으며, 이러한 현상은 설계에서 고려되어야 합니다.

3. 설계 의도의 명확성

의도의 불명확성: 입력을 바로 출력에 연결하는 행위는 때때로 설계 의도를 명확하게 전달하지 못할 수 있습니다. 설계자는 왜 이러한 연결이 필요한지, 이 연결이 어떤 기능을 하는지 명확히 문서화해야 할 필요가 있습니다.

4. 합성과 최적화

합성 도구의 최적화: 합성 도구는 회로를 최적화하는 과정에서 입력과 직접 연결된 출력을 제거하거나 변경할 수 있습니다. 이러한 최적화는 때로 예기치 않은 결과를 초래할 수 있으며, 설계 의도와 다르게 작동할 수 있습니다.

해결책과 고려 사항

버퍼링과 레지스터 사용: 문제를 해결하기 위해, 입력 신호를 출력에 직접 연결하는 대신 적절한 버퍼링 또는 레지스터링을 고려할 수 있습니다. 이러한 방법은 신호 지연을 관리하고, 신호 무결성을 보장하는 데 도움이 됩니다.

신호 경로 분석: 신호의 전파 경로를 면밀히 분석하여, 타이밍 문제나 신호 무결성 문제를 사전에 예측하고 대응할 수 있습니다.

설계 의도 명확화: 설계 문서에는 모든 신호 연결의 목적과 이유가 명확하게 기술되어야 합니다. 이는 추후 분석이나 최적화 과정에서 중요한 참고 자료가 됩니다.

결론적으로, 입력을 바로 출력에 연결하는 것이 단순해 보일 수 있지만, 디지털 회로 설계에서는 여러 복잡한 요소를 고려해야 합니다. 설계 의도를 명확히 하고, 신호 지연과 신호 무결성 문제를 해결하기 위한 적절한 기법을 적용하는 것이 중요합니다.

답변 1