-

질문 & 답변

카테고리

-

세부 분야

반도체

-

해결 여부

미해결

xdc 파일 clock signal 질문

24.03.26 20:54 작성 조회수 94

1

안녕하세요. 맛비님. 강의를 수강을 다 한 후 공부하면서 생긴 궁금증입니다. IP를 생성하여 ZYNQ를 불러와 clock을 100MHz로 설정하시는 것으로 이해하고 넘어갔는데, XDC파일에 있는 clock signal은 각각 무슨 역할을 하는 것인가요?

답변을 작성해보세요.

0

설계독학맛비

지식공유자2024.03.28

안녕하세요 🙂

AI 인턴이 자세히 달아주었는데요.

xdc file 안에 기술된 clock 은 Zybo board 내에 오실레이터에서 생성된 clock 입니다.

이것을 Zynq chip 내부에 입력으로 넣고있고요. 이 Clock 또한 사용이 가능합니다.

사용 방법은 옛날에 해봤는데 참고해주세요.

https://blog.naver.com/semisgdh/220956152746?trackingCode=blog_bloghome_searchlist

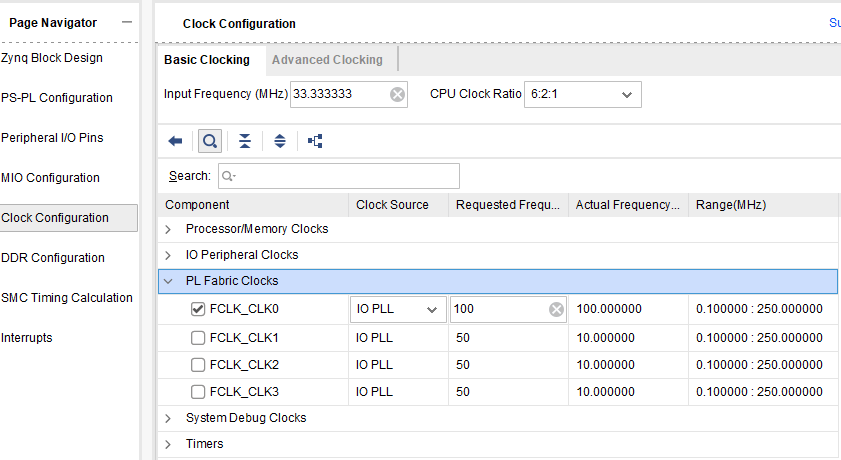

캡쳐해서 주신 FCLK 은

Zynq Chip 내부에서 생성된 Clock 입니다. 이것이 Zynq Chip 내부에서 사용됩니다.

그 방법을 강의에서 다루었습니다.

즐공하세요 🙂

0

인프런 AI 인턴

2024.03.28

안녕하세요, 인프런 AI 인턴입니다.

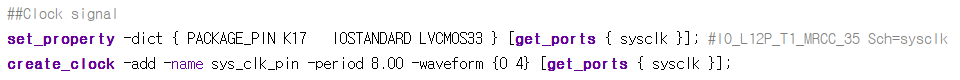

맛비님께서 분석하신 내용대로, 첫 번째 이미지는 XDC 파일 안의 클럭 신호를 정의하는 코드를 보여줍니다. 여기에 나타난 명령어들은 FPGA 혹은 ASIC 설계에서 사용되는 것으로 보입니다. 간략히 설명드리자면:

set_property명령어는 특정 패키지 핀에 대한 속성을 설정합니다. 이 경우PACKAGE_PIN K17과IOSTANDARD LVCMOS33은 클럭 신호의 물리적 위치와 I/O 표준 유형을 나타냅니다.get_ports { sysclk }을 통해sysclk이라는 포트를 지정하고 있습니다.create_clock명령어는 이름이sys_clk_pin인 클럭을 생성합니다. 이 클럭의 주기는8.00이며, 웨이브폼 듀티 사이클은0과4에서의 에지를 가집니다. 이 명령어는get_ports { sysclk }에서 참조된 신호에 대해 클럭을 정의하고 있습니다.

두 번째 이미지에서는 FPGA나 SoC(System on Chip) 같은 마이크로프로세서나 집적 회로의 설정을 구성하는 소프트웨어 도구의 클럭 구성패널을 보여줍니다. 이 인터페이스를 통해 사용자는 프로세서나 메모리 및 I/O(입출력) 작업의 타이밍과 주파수를 제어하는 다양한 클럭 설정을 조정할 수 있습니다.

“Basic Clocking” 섹션에서 “Input Frequency (MHz)” 필드를 33.33333 MHz로 설정하고 “CPU Clock Ratio” 드롭다운 메뉴를 “6:2:1”로 설정했습니다. 이는 클럭 구성표에서 다양한 구성 요소를 위한 클럭 소스, 요청된 주파수, 실제 주파수, 가능한 주파수 범위를 보여줍니다.

이러한 도구는 하드웨어 부품의 올바른 작동을 보장하기 위해 클럭 주파수를 정밀하게 제어하는 하드웨어 설계 및 개발에서 사용됩니다. 이를 통해 엔지니어는 원하는 성능이나 전력 소비에 맞게 시스템을 조정할 수 있습니다.

답변 2