Basic Design Synthesis Training (デジタル回路設計の実装)

MetaEncore

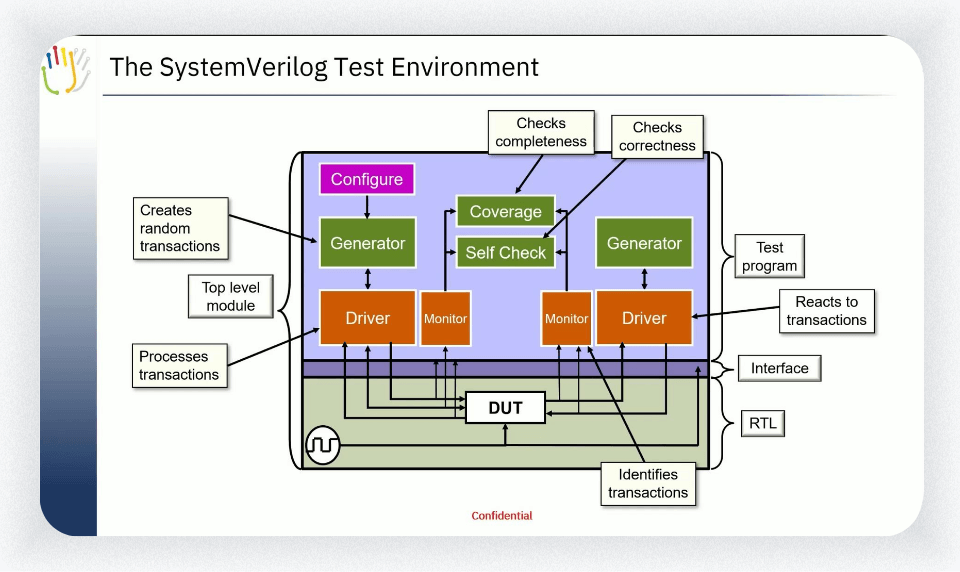

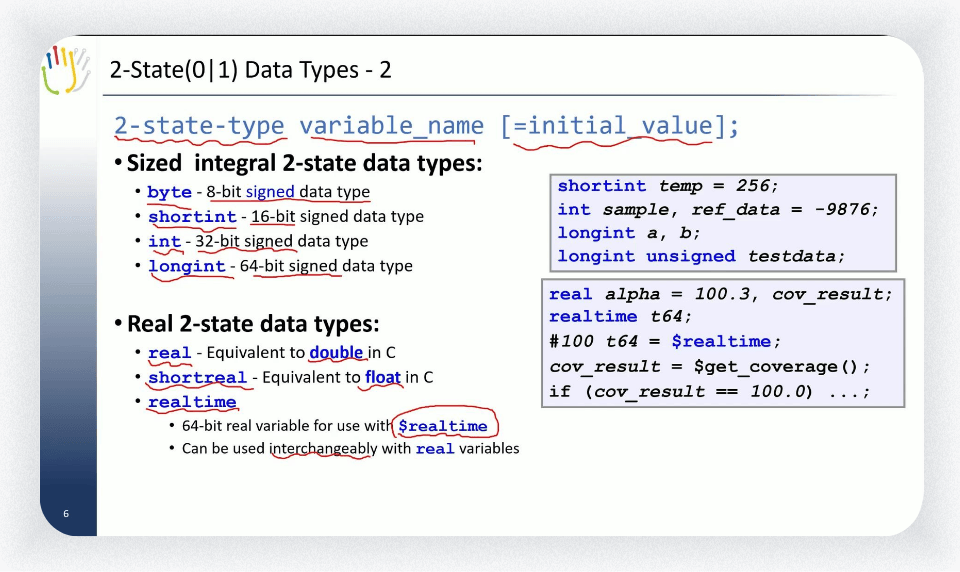

半導体チップはどのような段階を経て設計・製造されるのでしょうか。 PI(Physical Implementation) / PD(Physical Design)職務で必要とされる論理回路の基本概念と、チップ設計フロー(Chip Design Flow)について一歩ずつ確認し、現場でデジタルチップ回路設計に使用されるツールを基に、合成プロセスの主要な概念について見ていきます。

入門

EDA, digital-logic, vlsi