I'm learning SystemVerilog for the first time and it's really like a university lecture, which is great!!

I've been doing only Verilog so far, but someone suggested I try SystemVerilog this time, so I looked around and ended up taking this course - it's so good!

I've tried a few other courses, but they just briefly cover things like interface and class in a light way, but this one covers all the details thoroughly, so if I have questions later, I think it'll be great to look it up in the table of contents and re-watch just that part. It feels more like a real university textbook rather than a cram school lecture?? You cover everything and also highlight the important parts among them, so it seems good for both looking up things I don't know later and immediately applying what I've learned.

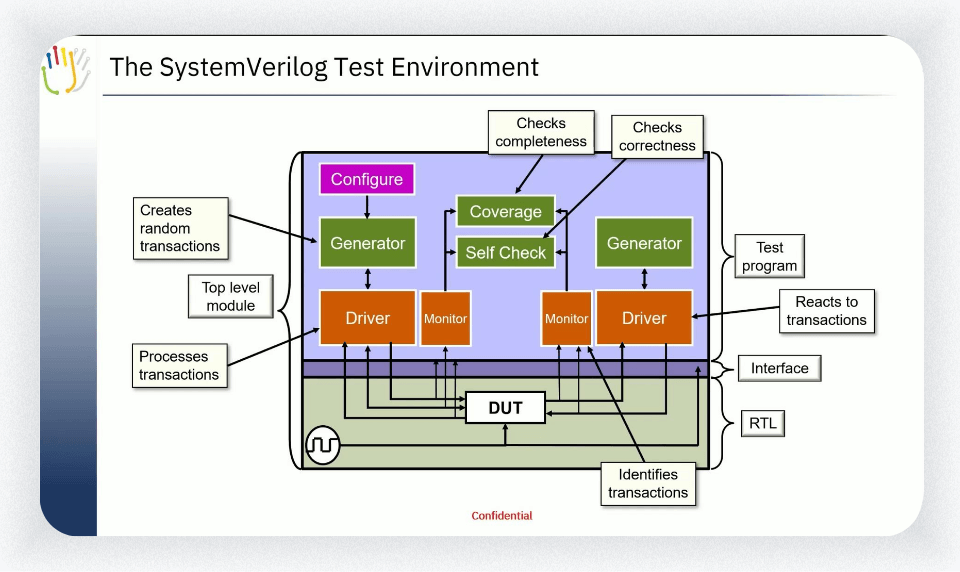

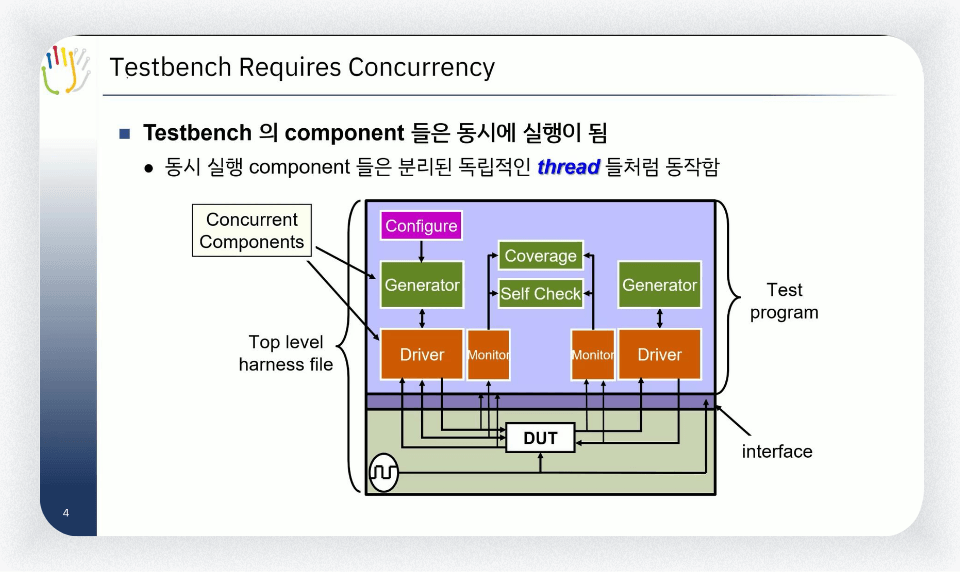

It's not just listing concepts one after another, but at the beginning you explain the structure and role, so while listening to the concepts, I could guess "ah, this is roughly what it's about" and "this is what this function does," which made it better to listen to.

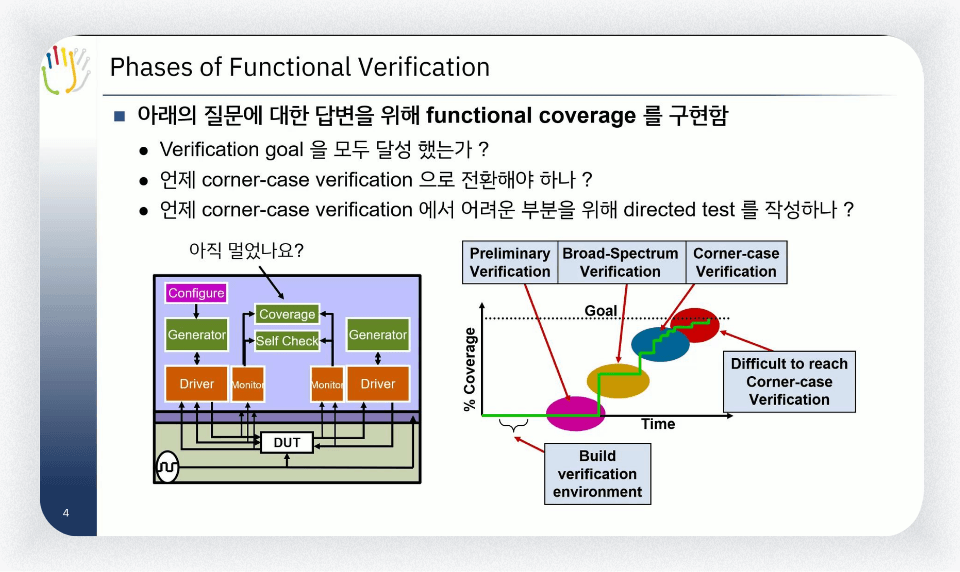

You call it basic, but it doesn't really seem basic 😆😆😆 The examples are explained in detail too, so I was able to write a testbench on my own and run it, and you explained the simulation methods in detail too, which was great, and having the scripts was so good!! Later, if I add other functions or sequences?? BFM??? and run them, and increase coverage, I think I'll graduate from basic 😊😊

I thought you'd immediately give me a design and have me write a testbench, but there were explanations of what the design is, what APB is, what completer is, etc., so I could roughly understand "ah, this is what I need to verify," which was really good. Also, when I had questions during the lecture, you explained in great detail, so thank you!

I totally recommend this course!! I'm satisfied 😊😊 I've introduced it to people around me a bit too!!!!

Especially for electronics majors who have studied Verilog, even if you don't necessarily do SystemVerilog, I think it would be good for studying Verilog too since there's Verilog code in the practice materials!!