Basic Design Synthesis Training (Digital Circuit Design Implementation)

MetaEncore

$254.10

Beginner / EDA, digital-logic, vlsi, soc, asic

5.0

(6)

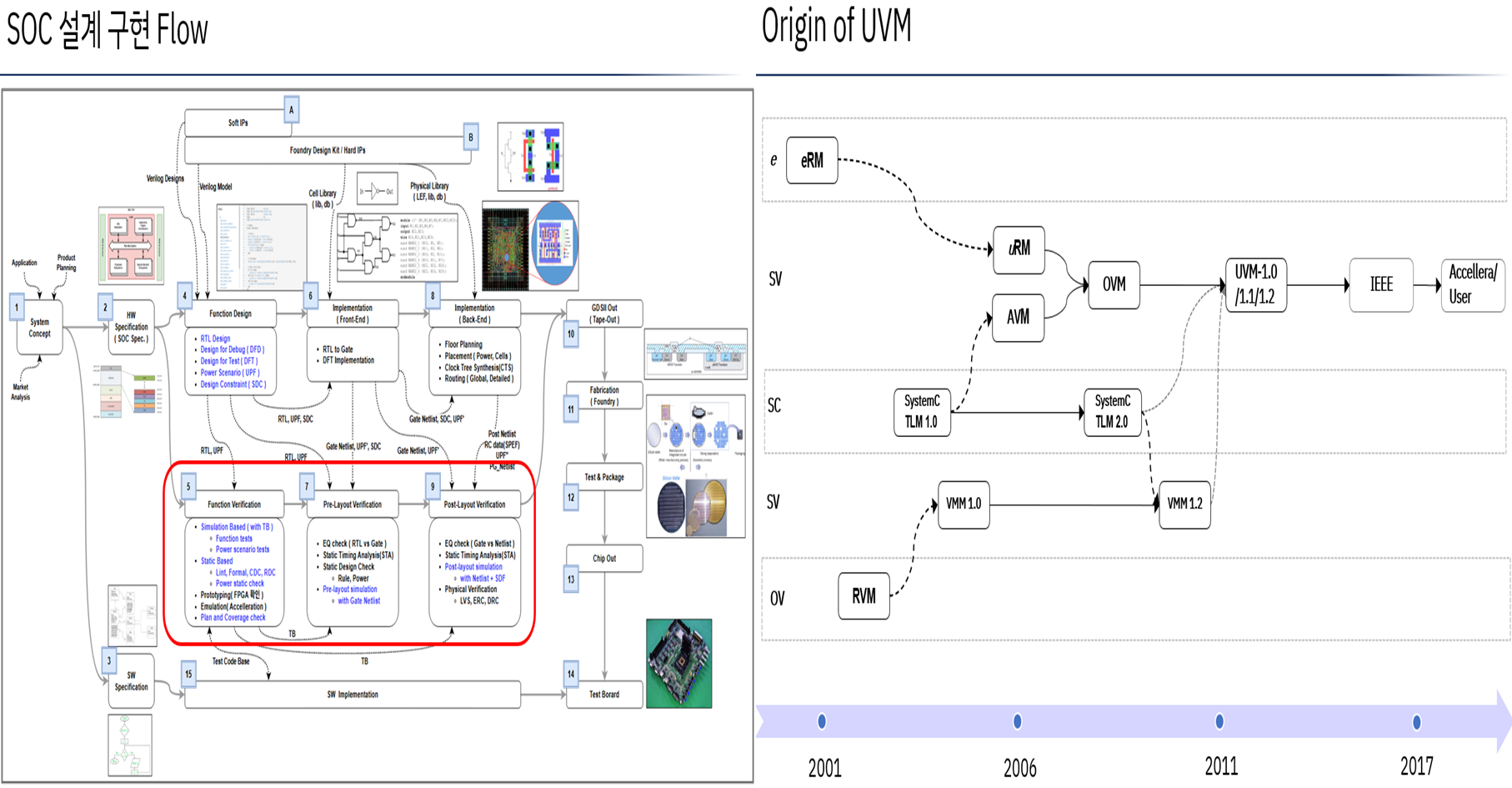

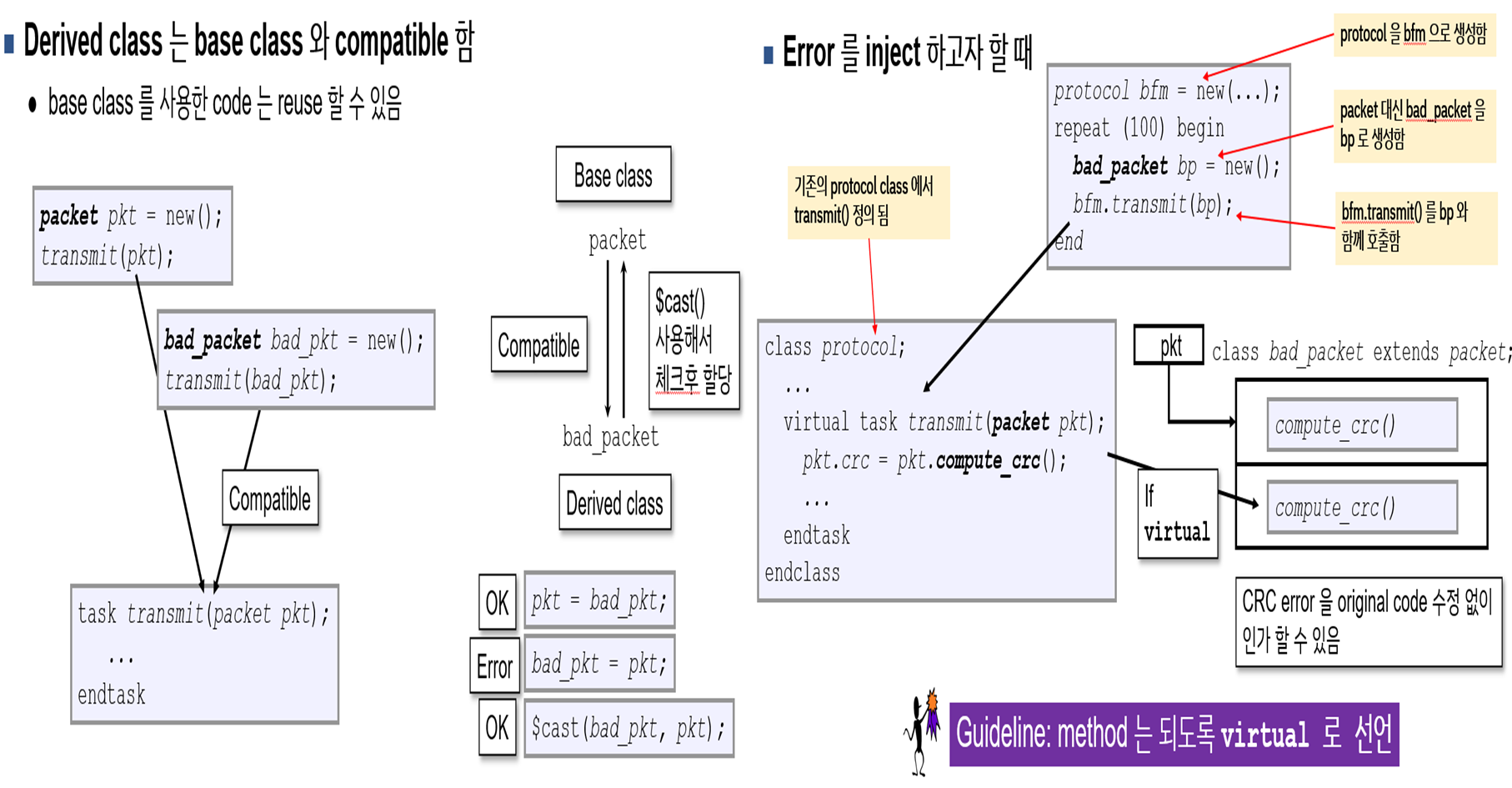

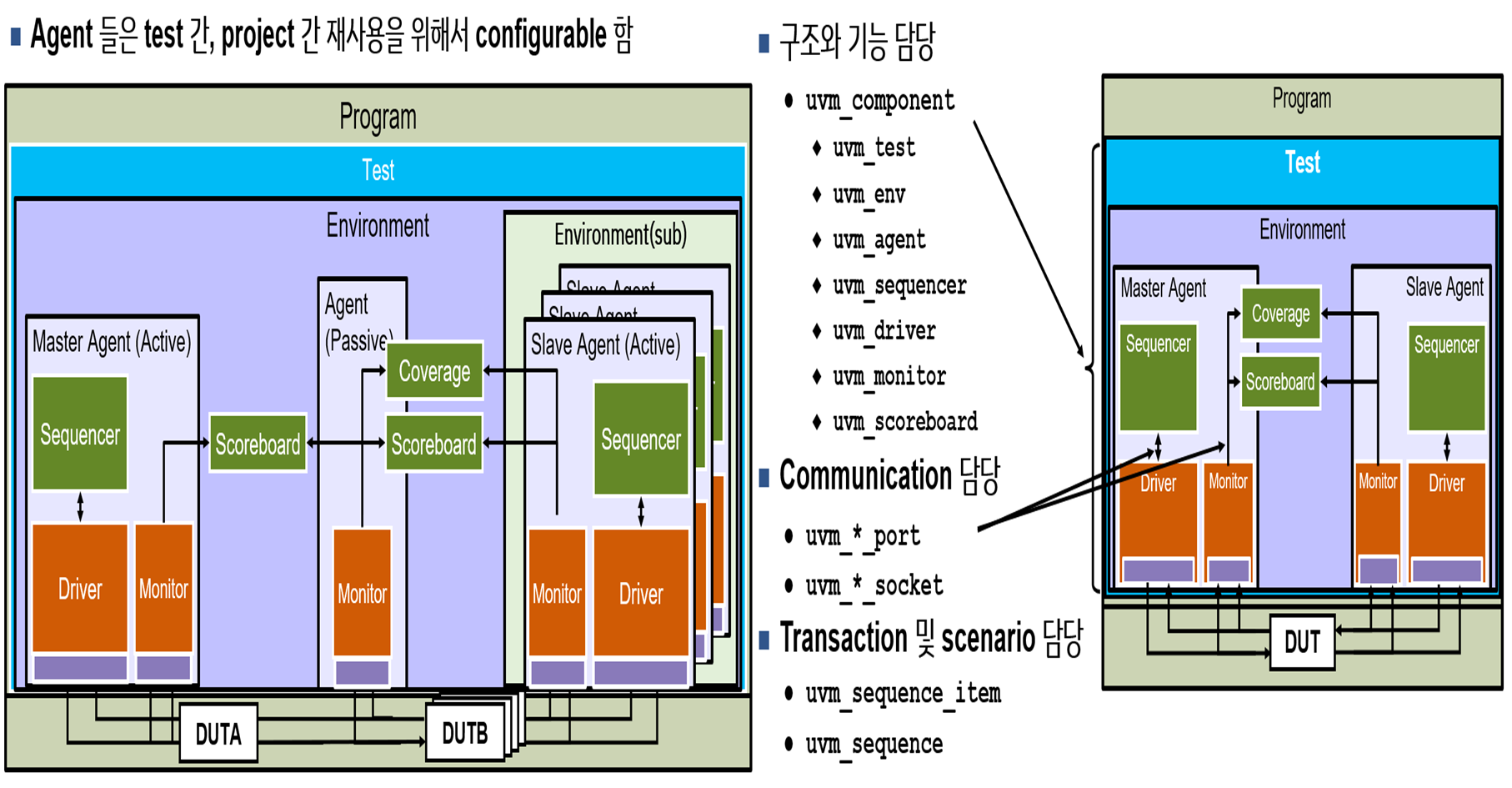

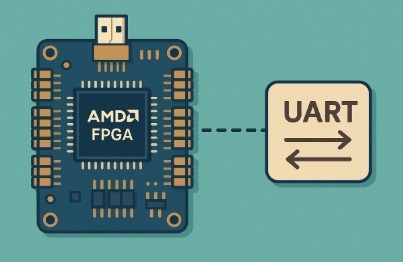

Through what stages are semiconductor chips designed and manufactured? We will examine the basic concepts of logic circuits and the Chip Design Flow required for PI (Physical Implementation) / PD (Physical Design) roles step-by-step, and explore the key concepts of the synthesis process based on the tools used for digital chip circuit design in the industry.

Beginner

EDA, digital-logic, vlsi