BGR TEMP Sweep

삼코치님 안녕하세요. 현재 BGR을 수강하고 있는 학생입니다.

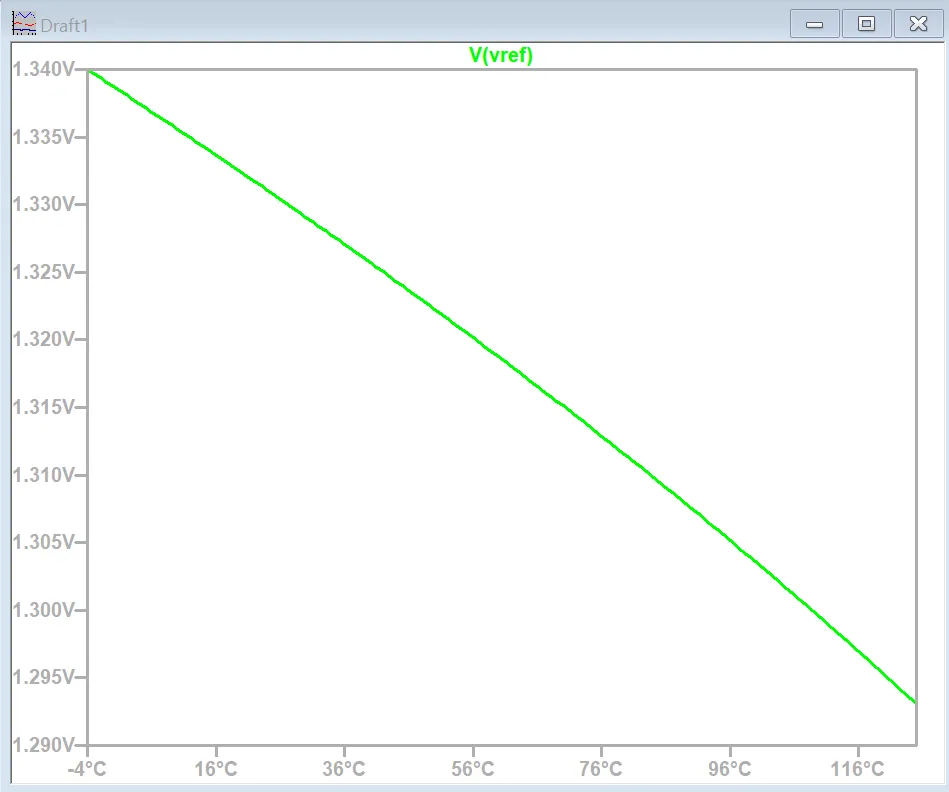

BGR 개선하기에서 Temp Sweep을 하는데 '2차함수'형태가 아닌 '음의 기울기를 가진 직선'의 형태로 나와서 질문을 하게 되었습니다.

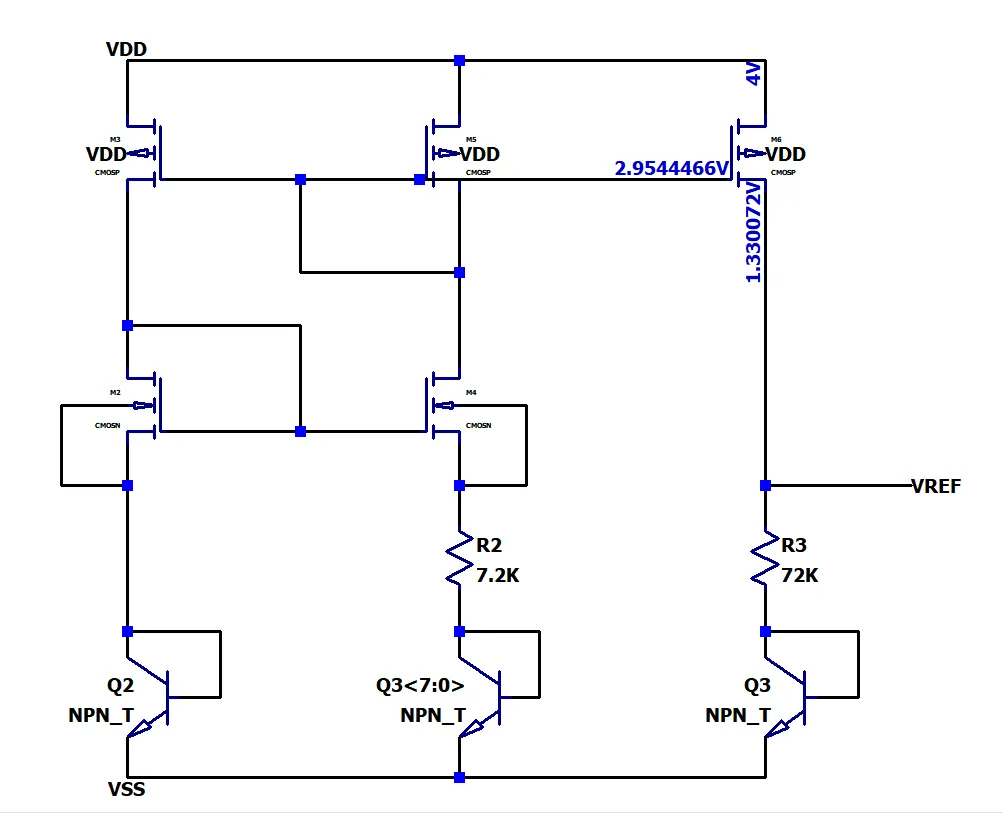

제 기준에서 V_ref도 1.2~1.4V 범위고 I도 전부 10uA 정도로 맞춘 것도 확인이 되어서 R2와 R3의 값을 사진과 같이 했습니다만...Temp Sweep에서 막혔습니다.

그래서 그래프 개형을 보았을 때 CTAT의 영향이 PTAT보다 강해서 나온 결과라고 판단이 들었는데요...

문제의 원인만 추측하게 되고...그에 대한 해결책은 잘 모르겠습니다..ㅠㅠ

일단 PMOS의 W/L 비율이나 R3의 수치도 바꾸고 그랬지만...개형 자체는 변화가 없었습니다. 게다가 R2까지 바꾸자니...I_R2 = 10uA도 깨질 것 같아 R2는 건드리지는 않았습니다...

제 그래프의 개형이 문제가 발생한 원인과 그에 대한 해결책이 궁금합니다...

(TR은 W와 L은 전부 1u로 한 회로입니다.)

답변 2

0

안녕하세요, 답변 남겨드립니다.

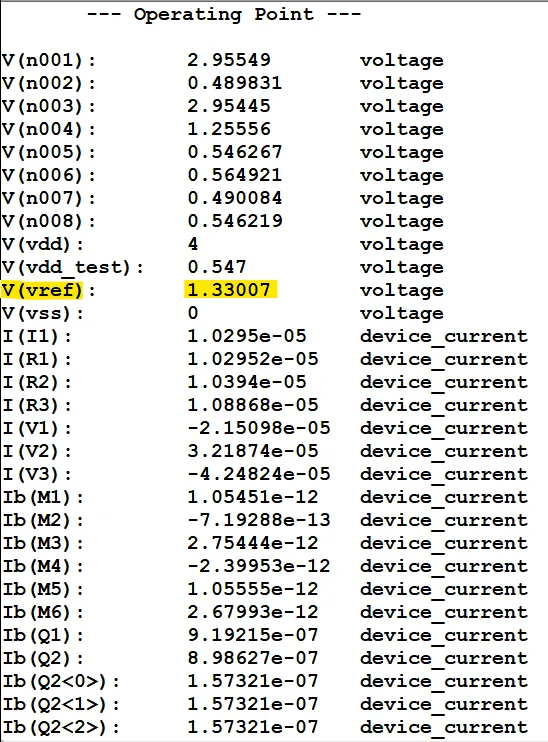

지금 그래프는 회로가 완전히 잘못 동작한다기보다, BGR의 1차 온도 보상이 아직 덜 맞아서 Vbe의 CTAT 성분이 남아 있는 상태로 보는 게 맞습니다. 화면상으로 Vref가 약 -4도에서 1.340V, 126도 근처에서 1.293V 정도라서 기울기는 대략 (1.293 - 1.340) / 130 = -0.36mV/C 정도입니다. 이 정도면 발산이나 바이어스 붕괴가 아니라, PTAT 가중치가 약간 부족해서 전체가 음의 직선처럼 보이는 상황입니다. BGR에서 우리가 기대하는 2차 곡선 형태는 CTAT와 PTAT의 1차 기울기가 거의 상쇄된 뒤에야 눈에 보입니다. 1차 기울기가 -0.3mV/C 이상 남아 있으면 Vbe의 거의 직선적인 온도 변화가 지배적이라서, 잔류 curvature는 그래프에서 묻혀버립니다.

이 회로를 이상적인 bandgap 식으로 보면 Vref = Vbe + (R3/R2)DeltaVbe 형태입니다. 여기서 DeltaVbe = VTln(N)이고, N = 8이면 d(DeltaVbe)/dT = 86uV/C*ln(8) = 약 179uV/C입니다. 현재 R3/R2 = 72k/7.2k = 10이므로 PTAT 쪽 기울기는 이상적으로 약 +1.79mV/C입니다. 그런데 실제 BJT의 Vbe 기울기는 바이어스 전류, 모델, 전류밀도에 따라 보통 -1.7~-2.3mV/C 정도로 움직입니다. 지금 결과가 -0.36mV/C로 나온다는 건, 현재 PTAT 가중치가 Vbe의 음의 기울기를 다 못 이기고 있다는 뜻입니다. 그래서 “CTAT 영향이 PTAT보다 강하다”는 판단은 방향이 맞습니다.

R3를 바꿨는데 개형이 크게 안 바뀐 것처럼 느껴진 이유는, 2차 곡선 모양 자체가 먼저 나오는 게 아니라 평균 기울기가 먼저 이동하기 때문입니다. 예를 들어 R3를 72k에서 75k 정도로 조금만 올리면 R3/R2가 10에서 10.4로 바뀌는데, N = 8 기준 추가되는 PTAT 기울기는 0.4*179uV/C = 0.072mV/C 정도밖에 안 됩니다. 지금 필요한 보정량이 약 0.36mV/C이므로, R3를 몇 k 정도 바꾸는 수준으로는 그래프가 여전히 음의 직선처럼 보입니다. 실무적으로는 R3/R2를 10에서 바로 11.5~12 정도까지 올려서 확인하는 게 빠릅니다. R2를 7.2k로 유지한다면 R3는 82k~86k 근처가 1차 확인 범위입니다. 현재 그래프 기울기만 놓고 보면 82k 부근부터 확인하고, 이상적인 N = 8 식 기준으로는 86k 부근까지 보는 게 자연스럽습니다.

다만 R3를 올리면 Vref DC 값도 같이 올라갑니다. 지금 Vref가 1.33V인데 R3/R2를 10에서 12로 올리면 PTAT 항이 대략 10~15% 이상 커져서 Vref가 1.42V 근처까지 올라갈 수 있습니다. 그래서 BGR 튜닝은 R3 하나만 만져서 끝나는 문제가 아니라, 온도 기울기는 R3/R2로 맞추고, Vref 절대값과 전류는 R2의 절대값, BJT 면적비, 바이어스 전류밀도로 다시 맞추는 식으로 접근해야 합니다. R2를 건드리면 I_R2 = 10uA가 깨질까 봐 멈추신 판단은 이해되지만, 실제 설계에서는 R2도 조정 대상입니다. R2는 “무조건 10uA를 유지하는 부품”이라기보다 DeltaVbe/R2로 PTAT 전류를 정하는 부품이고, R3/R2 비율이 온도 기울기를 정합니다.

현재 operating point에서 더 눈여겨볼 부분은 I(R2) = 10.394uA, I(R3) = 10.886uA로 약 4.7% 차이가 난다는 점입니다. 10uA 근처라서 비슷해 보이지만, R3가 72k라서 0.5uA 차이만 나도 Vref에서는 72k*0.5uA = 36mV 정도의 오차가 됩니다. 이 정도면 온도 sweep에서 보이는 전체 변화량 47mV와 같은 급입니다. 즉, 전류가 “대략 10uA”인 것과 “bandgap 식이 성립할 만큼 전류 미러가 온도 전 범위에서 잘 맞는 것”은 다른 이야기입니다. 양산 IP에서는 이런 전류 미러 오차가 온도, 공정, VDD에 따라 같이 움직이기 때문에 Vref TC와 line regulation을 동시에 흔듭니다.

MOS를 전부 W/L = 1u/1u로 둔 것도 현재 결과에 영향을 줄 가능성이 큽니다. 10uA에서 W = 1u는 모델에 따라 Vov가 200~400mV까지 올라갈 수 있고, L = 1u는 학습용 회로에서는 동작하지만 정밀 전류 미러 관점에서는 ro가 충분하지 않을 수 있습니다. 특히 M5와 M6의 VDS가 서로 다르면 channel length modulation 때문에 복사 전류가 몇 %씩 달라집니다. 지금처럼 R3 전류가 R2 전류보다 4~5% 큰 상황은 그런 비이상성이 이미 보인다고 봐도 됩니다. 전류 미러 쪽은 L을 2u~5u 정도로 늘리고, W는 목표 Vov가 150~250mV 정도가 되도록 다시 잡는 편이 좋습니다. 4V supply라면 headroom이 넉넉하니 속도보다 정확도와 ro를 우선하는 쪽이 맞습니다.

BJT 쪽 base current도 무시하기 어렵습니다. 캡처에서 Q2의 Ib가 약 0.9uA이고, Q3<7:0>의 base current 합이 대략 1.26uA 수준으로 보입니다. Branch current가 10uA라면 base current가 9~12%나 되는 셈입니다. 교과서식 계산은 보통 IC가 branch current와 거의 같고 beta가 충분히 크다는 전제에서 출발하는데, 지금 모델에서는 그 전제가 꽤 깨져 있습니다. beta가 온도에 따라 변하면 DeltaVbe와 R2 전류의 온도 의존성도 같이 변해서, R3/R2만 바꿨을 때 예상과 다르게 움직일 수 있습니다. 실제 BGR에서도 parasitic BJT beta가 낮은 공정에서는 base current 보상이나 구조 선택이 꽤 중요한 항목입니다.

디버깅은 Vref만 보지 말고 Vbe_out, I(R3)*R3, I(R2), DeltaVbe를 따로 나눠서 보셔야 합니다. Vref = Vbe_out + I(R3)*R3로 분해해서 plot하면, Vbe_out은 온도에 따라 내려가고 I(R3)*R3는 올라가야 정상입니다. 이때 I(R3)*R3의 증가 기울기가 Vbe_out의 감소 기울기보다 작으면 지금처럼 음의 직선이 나옵니다. 반대로 너무 크면 양의 기울기가 나옵니다. 두 기울기가 25도 기준으로 거의 같아질 때, 그때부터 익숙한 2차 곡선 또는 완만한 bow 형태가 보입니다.

현 상태에서 가장 현실적인 수정 순서는 R3를 72k에서 바로 82k, 86k, 90k 정도로 sweep해서 평균 기울기가 어떻게 움직이는지 확인하는 것입니다. 그다음 Vref 절대값이 너무 높아지면 R2와 R3를 같은 비율로 키우거나 줄이는 방식으로 전류를 다시 잡고, 필요하면 BJT 면적비 N을 8에서 16 정도로 바꿔서 설계 자유도를 확보합니다. 예를 들어 N을 16으로 올리면 d(DeltaVbe)/dT = 86uV/C*ln(16) = 약 239uV/C가 되어 같은 R3/R2에서도 PTAT 기울기가 더 커집니다. 다만 DeltaVbe 절대값도 같이 커지기 때문에 Vref DC와 headroom도 같이 확인해야 합니다.

실무 기준으로는 먼저 TT, 27도에서 예쁜 1.3V가 나오는 것보다 -40도~125도에서 평균 TC가 몇 ppm/C인지 보는 게 우선입니다. 지금은 1.33V 기준으로 -0.36mV/C이므로 TC로 환산하면 약 -270ppm/C입니다. BGR 과제 수준에서는 ±50ppm/C 안쪽이면 꽤 잘 맞춘 편이고, 양산 IP에서는 trim 없이 ±30~100ppm/C, trim 후 ±10~30ppm/C 정도를 목표로 잡는 경우가 많습니다. 지금 회로는 출발점으로는 괜찮지만, R3/R2 튜닝, 전류 미러 ro 개선, base current 영향 확인까지 해야 “왜 2차 곡선이 안 보이는지”가 정리됩니다.

0

안녕하세요, 인프런 AI 인턴입니다. 성규님.

BGR(Bandgap Reference) 회로의 온도 스윕 결과 Vref의 변화가 기대했던 곡률이 아닌 직선적인 형태로 나타난 것 때문에 어려움을 겪고 계시네요. 전압 스윕 결과로 CTAT의 영향이 PTAT보다 강하게 나타난 점에서 원인을 찾으려 하신 것 같습니다.

문제의 원인과 해결책

CTAT 및 PTAT 균형 조정:

- CTAT(전류/전압이 온도 증가와 반비례적으로 감소하는 성질) 성분이 강하다면, PTAT(온도 증가와 비례적으로 증가하는 성질) 성분을 증가시킬 필요가 있습니다. BGR 회로에서 CTAT 성분은 주로 V_BE에 의해, PTAT는 ΔV_BE에 의해 결정되므로, ΔV_BE를 더 크게 조정해보세요. 이를 위해서는 저항값, 특히 R2와 R3의 비율을 조율하거나 전류를 적정하게 재분배해야 합니다.

- CTAT(전류/전압이 온도 증가와 반비례적으로 감소하는 성질) 성분이 강하다면, PTAT(온도 증가와 비례적으로 증가하는 성질) 성분을 증가시킬 필요가 있습니다. BGR 회로에서 CTAT 성분은 주로 V_BE에 의해, PTAT는 ΔV_BE에 의해 결정되므로, ΔV_BE를 더 크게 조정해보세요. 이를 위해서는 저항값, 특히 R2와 R3의 비율을 조율하거나 전류를 적정하게 재분배해야 합니다.

저항 및 W/L 비율 조정:

- R2와 R3의 저항값이 PTAT/CTAT 효과를 조정하는 중요한 요소입니다. R3의 값만 변경하고 R2는 그대로 두면, 전체적인 PTAT/CTAT 비율이 달라질 수 있습니다. 또한, PMOS의 W/L 조정도 전류 밀도에 영향을 미쳐 BGR의 온도 특성에 변화를 줄 수 있습니다.

- R2와 R3의 저항값이 PTAT/CTAT 효과를 조정하는 중요한 요소입니다. R3의 값만 변경하고 R2는 그대로 두면, 전체적인 PTAT/CTAT 비율이 달라질 수 있습니다. 또한, PMOS의 W/L 조정도 전류 밀도에 영향을 미쳐 BGR의 온도 특성에 변화를 줄 수 있습니다.

온도 계수 보상 확인:

- BGR의 주요 목적은 온도에 따라 전압이 안정적으로 유지되도록 하는 것입니다. 따라서 ΔV_BE의 비율 설정이 잘못되었다면 온도에 따른 전압 곡선이 일정하지 않을 수 있습니다. R2/R3의 조정과 트랜지스터의 W/L의 조정을 다시 시도해보세요.

- BGR의 주요 목적은 온도에 따라 전압이 안정적으로 유지되도록 하는 것입니다. 따라서 ΔV_BE의 비율 설정이 잘못되었다면 온도에 따른 전압 곡선이 일정하지 않을 수 있습니다. R2/R3의 조정과 트랜지스터의 W/L의 조정을 다시 시도해보세요.

공정 및 시뮬레이션 세부 조건 재검토:

- 특정 공정의 세부 조건 또는 SPICE 모델의 설정이 잘못되거나 누락된 부분이 있을 수 있습니다. 사용 중인 시뮬레이션 모델 파일과 관련 설정을 확인하여 모델 파라미터가 의도한 대로 작동하는지 점검할 필요가 있습니다.

- 특정 공정의 세부 조건 또는 SPICE 모델의 설정이 잘못되거나 누락된 부분이 있을 수 있습니다. 사용 중인 시뮬레이션 모델 파일과 관련 설정을 확인하여 모델 파라미터가 의도한 대로 작동하는지 점검할 필요가 있습니다.

BGR 설계 확인:

- BGR 구조에서 ΔV_BE와 V_BE를 통한 가중합이 올바른지 확인하세요. 공용 설정으로는 다이오드 차수가 제대로 혼합되지 않을 수 있습니다.

- BGR 구조에서 ΔV_BE와 V_BE를 통한 가중합이 올바른지 확인하세요. 공용 설정으로는 다이오드 차수가 제대로 혼합되지 않을 수 있습니다.

아래 링크는 유사한 BGR 온도 보상 관련 질문에 대한 해결책을 제시한 답변입니다. 참고하시면 도움이 될 것입니다:

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다. 현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏 추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

[LTspice 질문] PSRR 측정 방법 질문드립니다.

0

41

2

BGR설계, BJT CTAT 성분

0

49

2

BGR 설계 질문

0

74

2

VINP,VINN 값

0

43

2

bgr 설계시 opamp

0

71

2

LTSpice log값에서 gm 안나옴. (해결하였습니다)

0

60

2

BGR 과제 관련 BJT model 질문 드립니다.

0

74

2

강의 pdf 자료

0

67

2

BGR 회로 질문 드립니다.

0

167

2

AC 분석 결과가 이상하게 나옵니다.

0

83

3

수강 연장 문의

0

69

2

LDO의 common source buffer와 관련해서 질문이 있습니다.

0

100

2

LDO 버퍼 관련해서 질문이 있습니다.

0

106

2

오실레이터 질문드립니다.

0

84

1

BGR 수업질문

0

139

2

Light/Heavy Load

0

138

2

LDO 설계시, AMP의 설계 스펙

0

338

2

과제6 주어진 조건에 맞춰서 oscillator 설계해보기 - Comparator하나 뺀 버전에서 더 큰 overall current에 대해서

0

118

1

Light/Heavy Load

0

114

1

수강 기간 연장 가능할까요?

0

80

2

챕터 4 강의안 62페이지. AC simulation돌릴때 SINE(1.2 10m 1k 0.5m) 파라미터 삭제해도 차이가 없는지에 대해서

0

100

2

PSRR

0

230

2

VDD 질문

0

153

2

[추가질문]13강,14강 PSRR 시뮬레이션 질문

0

246

1