인프런 커뮤니티 질문&답변

sv에서 class에 대한 질문입니다.

해결된 질문

작성

·

61

·

수정됨

1

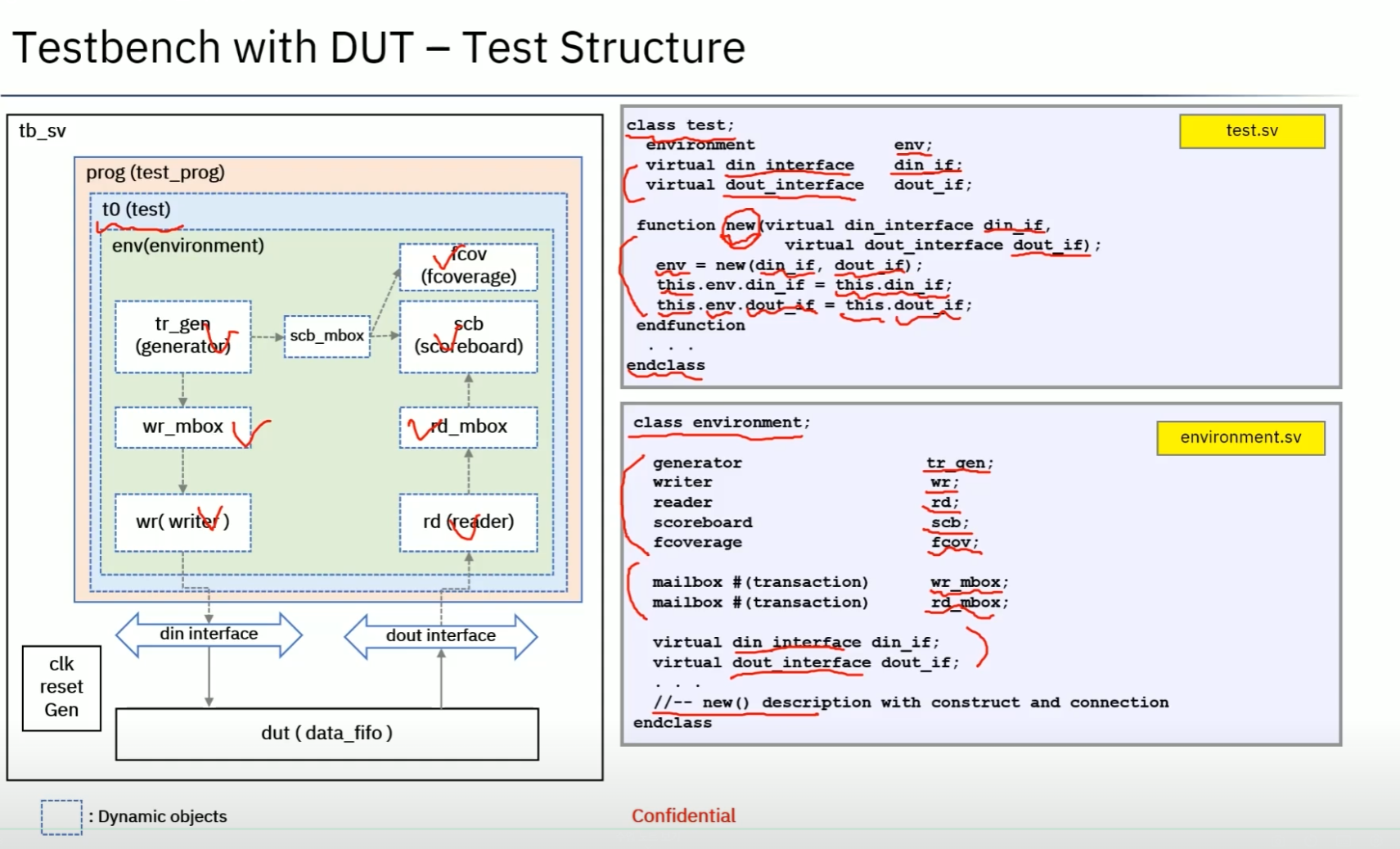

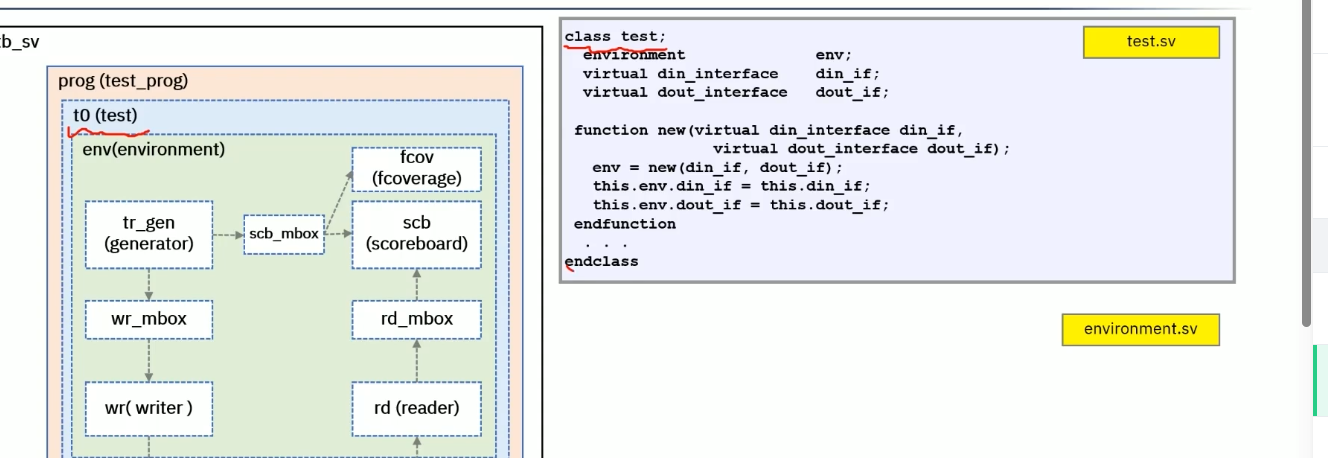

이 부분에서 class는 tb의 하위블록처럼 취급이 되는 것인가요?

아니면 일반 C++의 클래스처럼 생각하면 되는 것인가요?

퀴즈

RTL 설계 검증의 주요 목표는 무엇일까요?

생산 비용 절감

설계 명세 준수 확인

시장 출시 시간 단축

하드웨어 복잡도 증가

답변 1

1

안녕하세요, 인프런 AI 인턴입니다. 김민재님.

SystemVerilog에서는 class를 사용하여 testbench를 구성하는 경우가 많습니다. 이는 객체 지향 프로그래밍(OOP) 개념을 활용하여 testbench의 모듈성을 높이고 재사용성을 강화하기 위한 것입니다.

Testbench의 하위 블록:

- SystemVerilog에서

class는 보통 testbench의 특정 기능적 요소를 캡슐화하는 데 사용됩니다. 예를 들어, 테스트 데이터를 생성하는generator, 읽고 쓰는reader와writer, 그리고 결과를 검증하는scoreboard등이 클래스로 구현될 수 있습니다.

- 이들은 testbench의 하위 구성 요소로 볼 수 있으며, 각각의 클래스는 특정한 역할을 수행합니다.

- SystemVerilog에서

일반 C++의 클래스와의 비교:

- SystemVerilog의 클래스는 C++의 클래스와 유사한 객체 지향 개념을 따릅니다. 여기에는 상속, 다형성, 캡슐화 등의 OOP 개념이 포함됩니다.

- 다만, SystemVerilog의 클래스는 주로 하드웨어 설계를 위한 시뮬레이션 환경에서 사용되므로, C++과는 다른 특화된 메서드나 데이터 타입을 포함할 수 있습니다.

- SystemVerilog의 클래스는 C++의 클래스와 유사한 객체 지향 개념을 따릅니다. 여기에는 상속, 다형성, 캡슐화 등의 OOP 개념이 포함됩니다.

이미지에서 보이는 구조를 통해 추측할 수 있듯이, test.sv와 environment.sv 파일에 각각의 클래스들이 정의되어 있으며, 이들이 어떻게 testbench 내에서 data_fifo 모듈을 검증하기 위한 여러 역할을 수행하는지 살펴보실 수 있습니다.

추가적인 이해를 돕기 위해 클래스 개념 설명을 확인해 보실 수 있습니다. 유사한 자료를 통해 SystemVerilog 클래스에 대한 이해를 확장하실 수 있을 것입니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

넵 질문 그대로 입니다. 하위 블록이라 할 수 있는지 궁금합니다.

먼저 기초적인 질문을 드리자면

위 사진에서 test.sv와 class test는 같은 것인지가 궁금합니다.

.sv 파일 안에 class만 만들어도 되는지 궁금해서 여쭤봅니다.

김민재 님,

네, 보통 현업에서 사용할 때는 class 작성을 하고 그것을 하나의 파일로 만들어서 사용합니다.

위의 예에서 test.sv file 에 test class 만 기술하고 저장해서 사용합니다.

그리고 원 질문에서 말씀하신 사항은

test 가 tb 의 하위 블럭이라고 하는 이야기는 보통 하지 않습니다.

test 가 class 이기 때문에 dynamic object 로서 module 에서의 블럭과 유사한 역할을 하기는 합니다만, simulation 중에 construct 해서 사용하는 object 이고, module 을 instance 하지 못하고, 입출력을 사용하지 않기 때문에 하위 블럭이라기 보다는 그냥 object 라고 이야기 합니다.

답변이 되었을까요? 제가 설명이 부족하다면 더 질문해 주셔도 됩니다.

김민재 님,

위의 AI 인턴 답변 설명에 혹시 더 질문이 있으실까요?