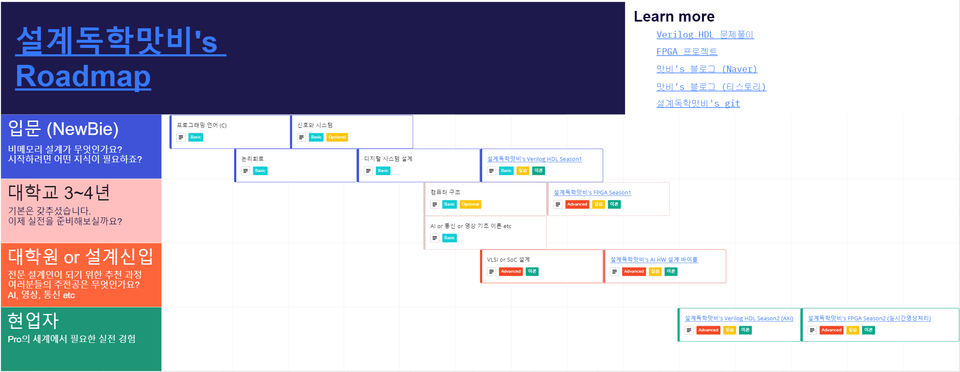

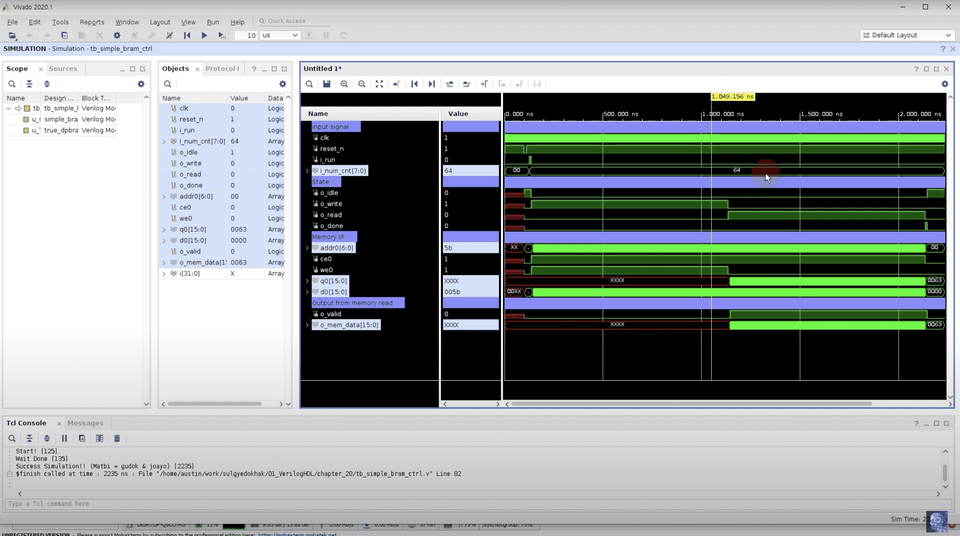

Design Self-Study Tastebi's Practical FPGA-Based HW Accelerator Design (From LED Control to Fully Connected Layer Accelerator Design)

semisgdh

With the help of the design self-study taste-maker! Let's gain basic knowledge of FPGA and HW accelerator design experience.

Intermediate

FPGA, Embedded

![[AUTOSAR] Mastering Basic AUTOSAR Concepts for New EmployeesCourse Thumbnail](https://cdn.inflearn.com/public/courses/335114/cover/00356529-b9f9-4cc8-9b6b-9bddfd8d730d/335114.png?w=420)