Clock Period 설정방법

안녕하세요

Artix7 FPGA의 Clock period 설정 방법에 대해 문의드립니다.

16페이지에 Arty A7보드는 기본으로 100MHz를 사용한다고 나와있는데 Artix 7 Datasheet의 어느 부분을 확인해야 알 수 있는 걸까요?

더불어 PLL의 M,N 값은 0~15,0~31로 범위가 한정되어 있다고 하셨는데 FPGA의 특성마다 M,N값의 범위가 있는 걸까요? 이 또한 데이터 시트에 나와있는 걸까요?

Artix-7 FPGAs Data Sheet: DC and AC Switching Characteristics (DS181) 의 어느 부분을 확인하면 되는지 문의드립니다.

답변 1

0

안녕하세요.

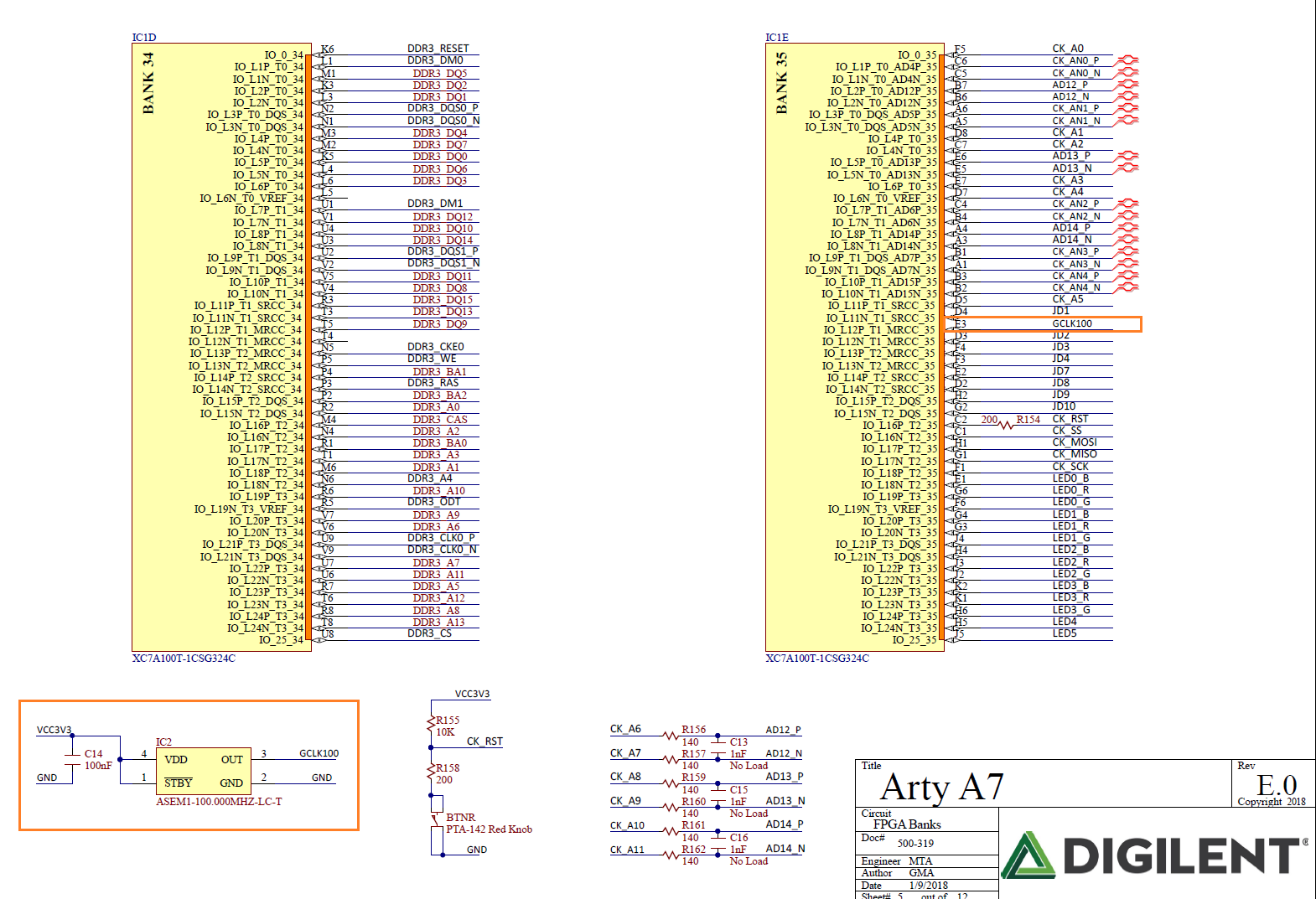

회로도의 아래 부분 확인하시면 됩니다.

자료실에 회로(arty_a7_sch.pdf)도 올려두었습니다.

Xilinx 문서는 모듈별로 user manual 이 별도로 되어 있습니다. 자료실에 Clock에 관한 user manual 올려두었습니다. (ug472_7Series_Clocking.pdf)

Ch3. Clocking Management Tile 확인하시면 됩니다. 72, 77 page에 자세한 설명이 있으니 참조하시길 바랍니다.

감사합니다 ~!!

[HDL 32장-2부] 참고 링크 관련

1

35

2

강의 만료일 연장 신청

0

32

2

기초예제 파일 불러오기 문의

0

25

2

Zybo 환경에서 PL RTL UART 보드 검증 방법

0

30

2

혹시 별도의 자료가 있나요?

0

33

2

Zynq z7 FPGA single-ended 관련

0

40

1

Differential Amp의 4가지 종류

0

41

1

[HDL 22장] F/F CE 관련 질문

1

45

2

UART0, 1 중 선택

1

50

2

fpga 개발보드

0

29

2

vivado 2022.1 version memory IP 구조

0

38

1

datamoverbram모듈질문

1

63

2

latency 개념 구현

1

84

3

13강에 언급된 강의 내용 질문

1

61

2

비바도 all os버전

1

67

2

초기화를 reset_n 이 '1'일 때가 아닌 '0' 일 때 실행시키는 이유 질문

1

68

2

다운로드용량

1

68

2

mig7_write8 수정 부분 질문있습니다

0

48

2

Address 증가에 대해 의문이 있습니다.

0

371

1

Memory Address 구현 질문

0

283

1

ui_clk값을 낮출수 있을까요?

0

327

1

DDR Controller 핀 맵핑

0

644

2

HW Bitstream 다운로드 시 에러 문의

1

543

2

Memory controller 설계 관련 질문

0

1440

1