과제6 주어진 조건에 맞춰서 oscillator 설계해보기 - Comparator하나 뺀 버전에서 더 큰 overall current에 대해서

안녕하세요 삼코치님,

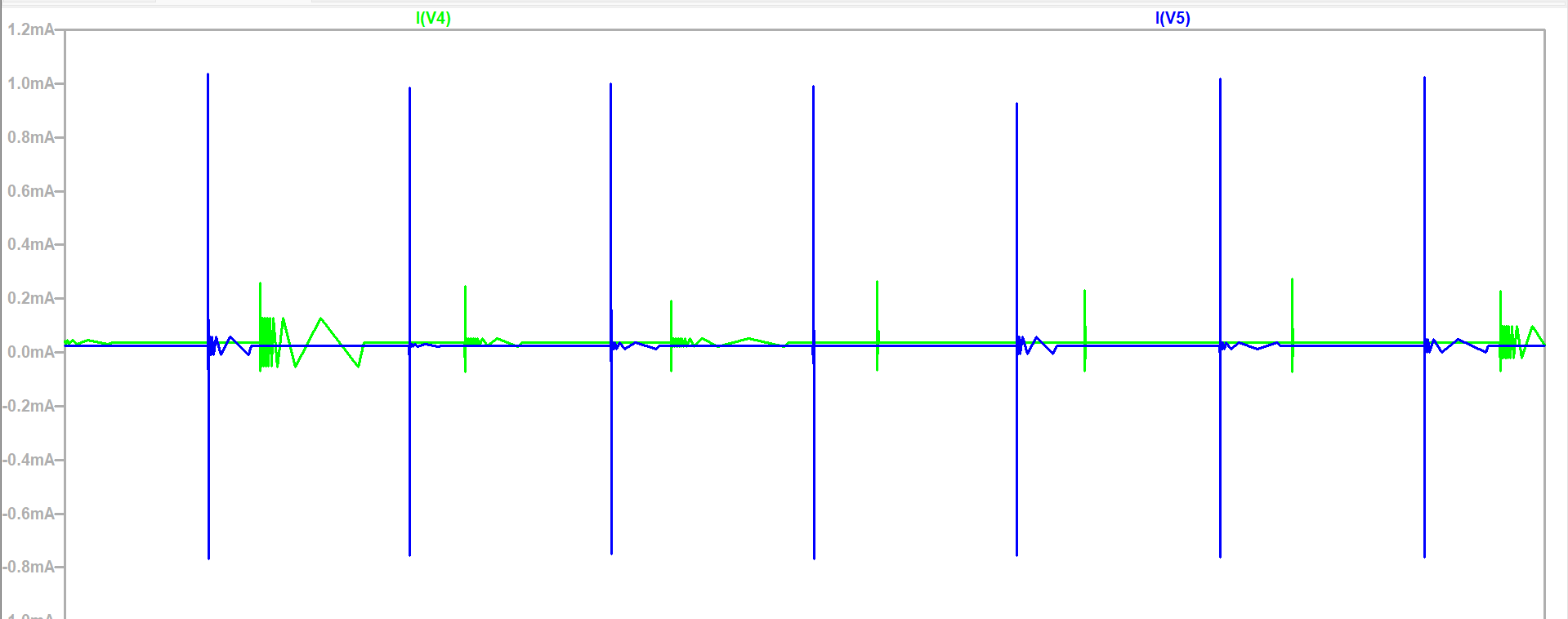

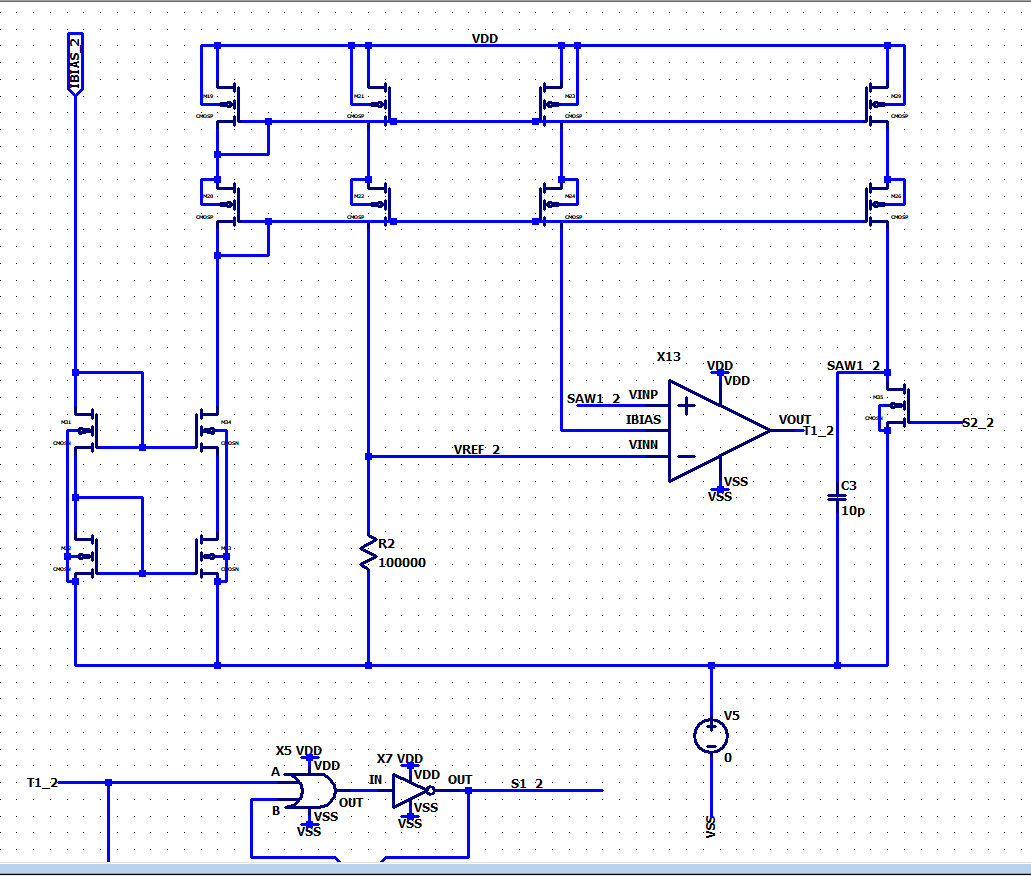

과제6 삼코치님이 이미 설계해두신거 에서 Jitter성분하고 Power(current)확인을 해봤는데요. Comparator한개 쓴 버전에서 확실히 Jitter는 확실히 100kHz에서 더 뾰족해졌음을 확인했지만 전류는 다음 사진과 같이 I(V5)(comparator1개)가 I(V4)(comparator2개) 짜리보다 더 크게 나와서 제가 측정을 잘못한건지 아니면 다른 원인이 있는지 궁금하여서 여쭈어봅니다.

삼코치님의 말씀대로 전류를 측정하기위해 0V voltage source를 달아놓고 전류를 측정해보았습니다.

항상 친절한 답변 감사드립니다.

답변 1

0

안녕하세요, 답변 남겨드립니다.

Comparator를 하나만 사용하는 oscillator 구조와 두 개 사용하는 구조에서 전류 소비 측정을 하셨을 때, comparator 1개 버전이 오히려 더 큰 전류를 소비한 것으로 관측되었다는 부분에 대해 설명드리겠습니다.

일단 기본적으로 comparator의 개수가 적다는 것은 comparator 자체의 정적인 소비전류(static current) 혹은 동적 소비전류(dynamic current switching activity)에 있어서는 감소를 의미할 수 있지만, oscillator 전체 동작에서의 평균 전류 소비는 단순히 comparator 수에만 의존하지 않습니다. 중요한 요소는 oscillator의 동작 속도(frequency), switching activity, output stage의 capacitive load, bias current 설정 등에 따라 크게 달라질 수 있습니다.

특히, comparator를 하나만 쓴 버전에서 전체적인 동작 주기가 더 짧아졌거나 또는 comparator가 더 빠르게 switching하도록 강한 bias current를 사용한 경우, comparator 내부에서의 dynamic power 소비가 증가할 수 있습니다. Dynamic power는 다음과 같은 수식으로 표현됩니다.

P_dynamic = α × C × V² × f

여기서 α는 switching activity, C는 load capacitance, V는 공급 전압, f는 switching frequency입니다. 예를 들어 comparator 1개짜리 구조에서 주파수가 상대적으로 높아졌다면 f 증가에 의해 dynamic power가 더 커질 수 있습니다.

또한, 내부적으로 feedback이나 charge/discharge 경로에 대한 구조가 변경되면서, comparator 외의 경로에서도 더 큰 전류 소모가 발생할 수 있습니다. 예를 들어 하나의 comparator에 더 많은 전류를 흘려서 빠른 비교를 유도했거나 또는 comparator 출력단에 연결된 buffer 혹은 level shifter의 동작 속도를 높이기 위해 전류 경로를 강화했을 수도 있습니다.

사용하신 I(V4), I(V5) 측정 방법은 정확하게 V=0 source를 comparator 입력 전류 경로에 직렬 연결했고, 이 방식은 매우 일반적인 DC/Transient current 측정 방법입니다. 이 방식 자체는 문제가 없습니다만, 동작 조건이 완전히 동일하지 않다면 단순 비교로는 부족할 수 있습니다. 예를 들어 comparator1개 버전에서 공급된 바이어스 전류 혹은 내부 bias source 설정이 다를 수 있고, 특히 PULSE source나 Vctrl 등 시간 함수 기반 전원에서의 차이로 전류 평균이 달라질 수도 있습니다.

보다 정확한 비교를 위해서는 아래 사항들을 통일한 뒤 비교해보시기를 추천드립니다:

두 구조 모두 동일한 주파수 동작 조건에서 측정할 것.

comparator에 흐르는 바이어스 전류 혹은 load condition을 동일하게 설정할 것.

시뮬레이션 시간(Transient analysis의 stop time)과 측정 시간 윈도우를 동일하게 설정할 것.

실제 실무에서도 이런 이슈는 빈번하게 발생하며, 특히 oscillator와 같이 feedback 구조가 있고 comparator 동작이 critical path인 회로에서는 layout parasitic이나 current mirror mismatch 등에 의해서도 이러한 결과가 달라질 수 있습니다.

결론적으로, comparator 수가 적다고 해서 무조건 전류가 적게 소모되지는 않으며, oscillator 전체의 주파수 증가, switching activity 상승 등이 결합되면 오히려 전체 전류는 더 증가할 수 있습니다. 따라서 구조에 대한 동작 주파수와 전류 소비 간의 상관관계를 분석한 후 이를 기반으로 최적화를 진행하는 것이 바람직합니다.

BGR TEMP Sweep

0

28

2

[LTspice 질문] PSRR 측정 방법 질문드립니다.

0

45

2

BGR설계, BJT CTAT 성분

0

53

2

BGR 설계 질문

0

79

2

VINP,VINN 값

0

46

2

bgr 설계시 opamp

0

73

2

LTSpice log값에서 gm 안나옴. (해결하였습니다)

0

62

2

BGR 과제 관련 BJT model 질문 드립니다.

0

76

2

강의 pdf 자료

0

68

2

BGR 회로 질문 드립니다.

0

171

2

AC 분석 결과가 이상하게 나옵니다.

0

84

3

수강 연장 문의

0

69

2

LDO의 common source buffer와 관련해서 질문이 있습니다.

0

103

2

LDO 버퍼 관련해서 질문이 있습니다.

0

106

2

오실레이터 질문드립니다.

0

84

1

BGR 수업질문

0

141

2

Light/Heavy Load

0

140

2

LDO 설계시, AMP의 설계 스펙

0

340

2

Light/Heavy Load

0

114

1

수강 기간 연장 가능할까요?

0

80

2

챕터 4 강의안 62페이지. AC simulation돌릴때 SINE(1.2 10m 1k 0.5m) 파라미터 삭제해도 차이가 없는지에 대해서

0

101

2

PSRR

0

233

2

VDD 질문

0

153

2

[추가질문]13강,14강 PSRR 시뮬레이션 질문

0

248

1