SPI Master Waveform 질문입니다.

waveform을 보며 분석하고 공부중입니다.

waveform을 보며 분석하고 공부중입니다.

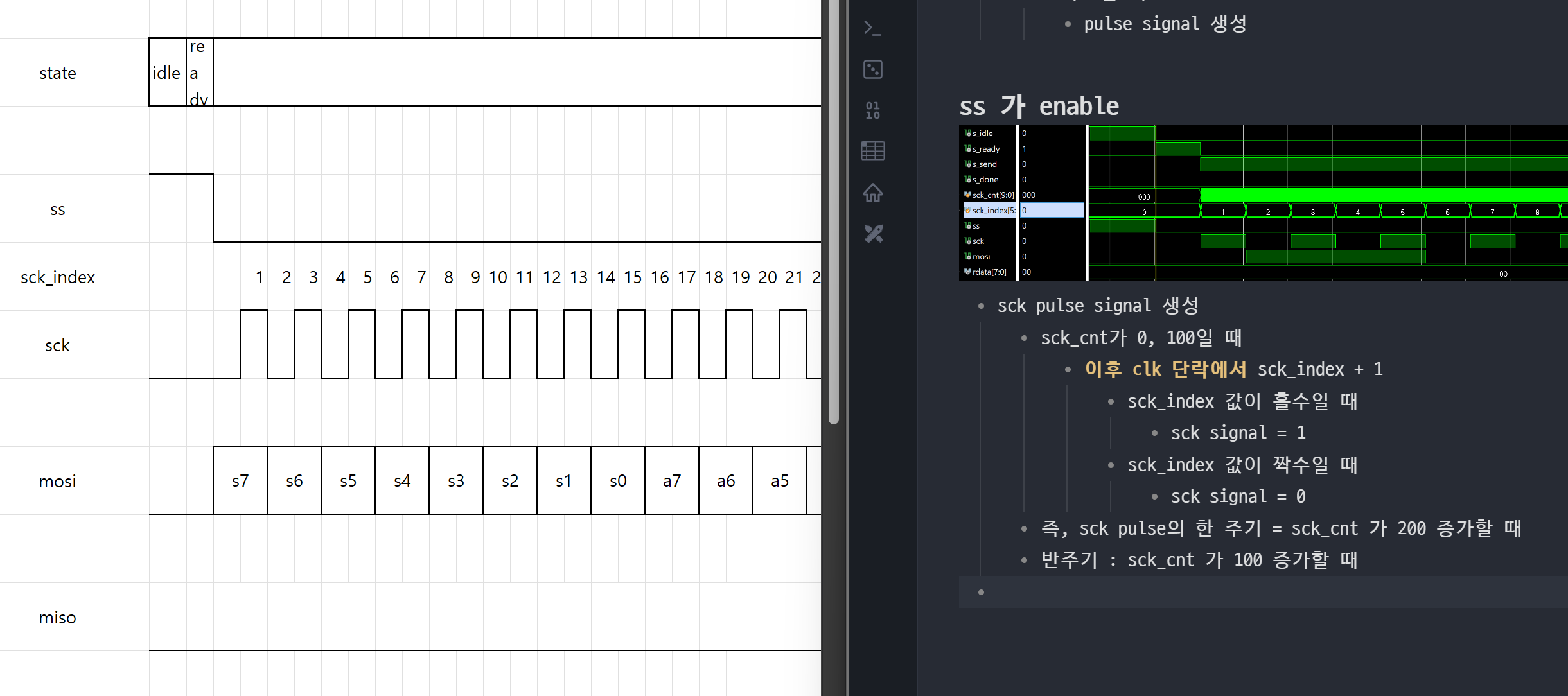

제공해주신 Timing Diagram 상에서는 sck pulse는 s_ready가 r_send 로 변환된 다음 단락에서 positive edge가 발생합니다.

그러나 제가 시뮬레이션해본 waveform에서는 s_send가 enable됨과 동시에 sck pulse에 positive edge가 발생합니다.

이부분이 헷갈려서 질문드립니다.

코드를 다시 들여다보면서 답을 찾는게 좋을까요??

답변 1

0

spi 는 4가지 모드가 있습니다. (구글에서 spi mode 로 검색하면 알 수 있습니다)

각각의 모드에 맞게 프로그램 해야 합니다. s_send가 enable 됨과 동시에 sck가 발생한다면, slave쪽에서 오류가 발생할 가능성이 높습니다. 따라서 어디가 원인 인지를 찾아서 프로그램을 수정하고 다시 simulation해 보시길 바랍니다. 이러한 과정이 기술을 익히는데 많은 도움이 됩니다. fpga, verilog를 배우려면 코팅하고 파형 확인하고 수정하고 파형 확인하고 이러한 과정을 수도 없이 거쳐야 합니다. 저도 현업에서 진행 중일 때, 마찬가지로 코딩하고 simulation으로 파형 확인하고 이러한 과정을 수 없이 반복합니다.

감사합니다 ~

[HDL 32장-2부] 참고 링크 관련

1

35

2

강의 만료일 연장 신청

0

32

2

기초예제 파일 불러오기 문의

0

25

2

Zybo 환경에서 PL RTL UART 보드 검증 방법

0

30

2

혹시 별도의 자료가 있나요?

0

32

2

queue assignment pattern 문의 건

0

32

1

Mission 5 문의 건

0

45

2

Zynq z7 FPGA single-ended 관련

0

39

1

강의자료 PDF 어떻게받나요?

0

42

2

Differential Amp의 4가지 종류

0

41

1

[HDL 22장] F/F CE 관련 질문

1

45

2

UART0, 1 중 선택

1

50

2

fpga 개발보드

0

28

2

vivado 2022.1 version memory IP 구조

0

38

1

강의 ppt 자료 요청건

0

56

2

datamoverbram모듈질문

1

63

2

latency 개념 구현

1

84

3

미션tree

0

40

3

강의7 질문

0

47

2

mission1 질문

0

60

3

Verilog Testbench DB 원본

0

50

1

13강에 언급된 강의 내용 질문

1

61

2

SPI MASTER 모듈에 관한 질문입니다.

0

208

1

Text Editor에 관한 질문입니다.

0

296

1