Đào tạo Tổng hợp Thiết kế Cơ bản (Triển khai thiết kế mạch kỹ thuật số)

MetaEncore

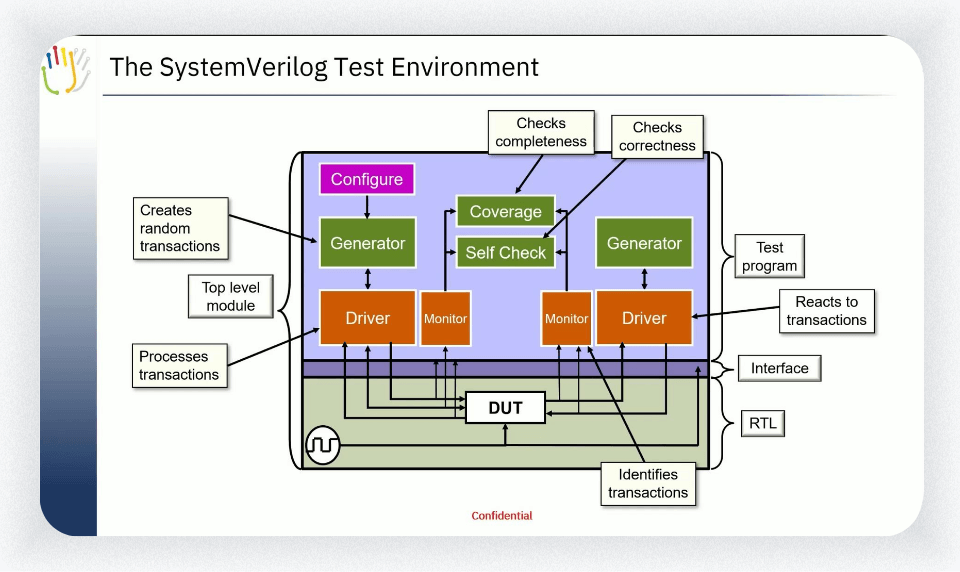

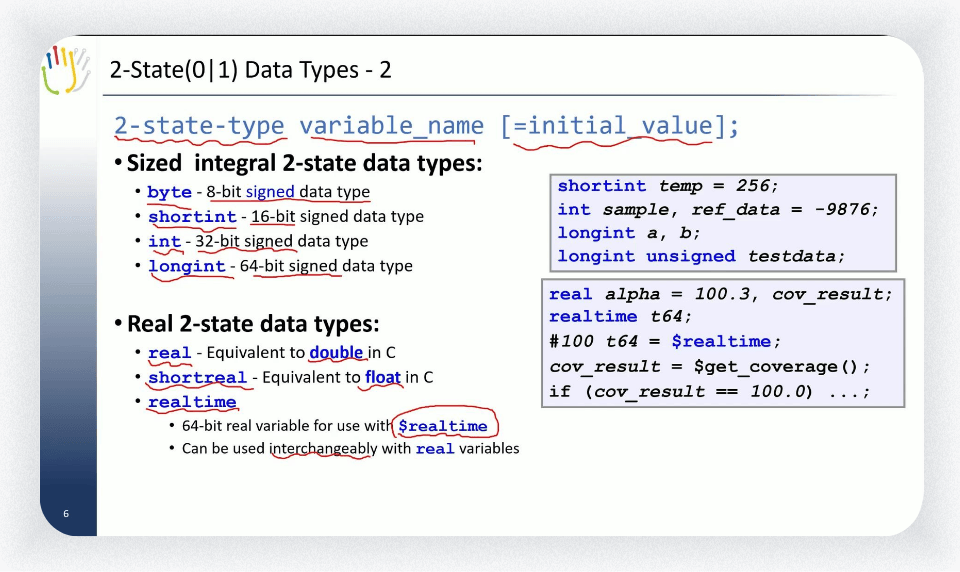

Chip bán dẫn được thiết kế và sản xuất qua những giai đoạn nào? Chúng ta sẽ tìm hiểu từng bước về các khái niệm cơ bản của mạch logic cần thiết trong công việc PI (Physical Implementation) / PD (Physical Design) và quy trình thiết kế chip (Chip Design Flow), đồng thời xem xét các khái niệm chính của quá trình tổng hợp (synthesis) dựa trên các công cụ được sử dụng trong thiết kế mạch chip kỹ thuật số thực tế.

Nhập môn

EDA, digital-logic, vlsi