인프런 커뮤니티 질문&답변

SPICE Output Log에 대한 질문

해결된 질문

작성

·

49

0

안녕하세요. 수업을 수강하며 궁금한 것이 생겨 질문을 남깁니다.

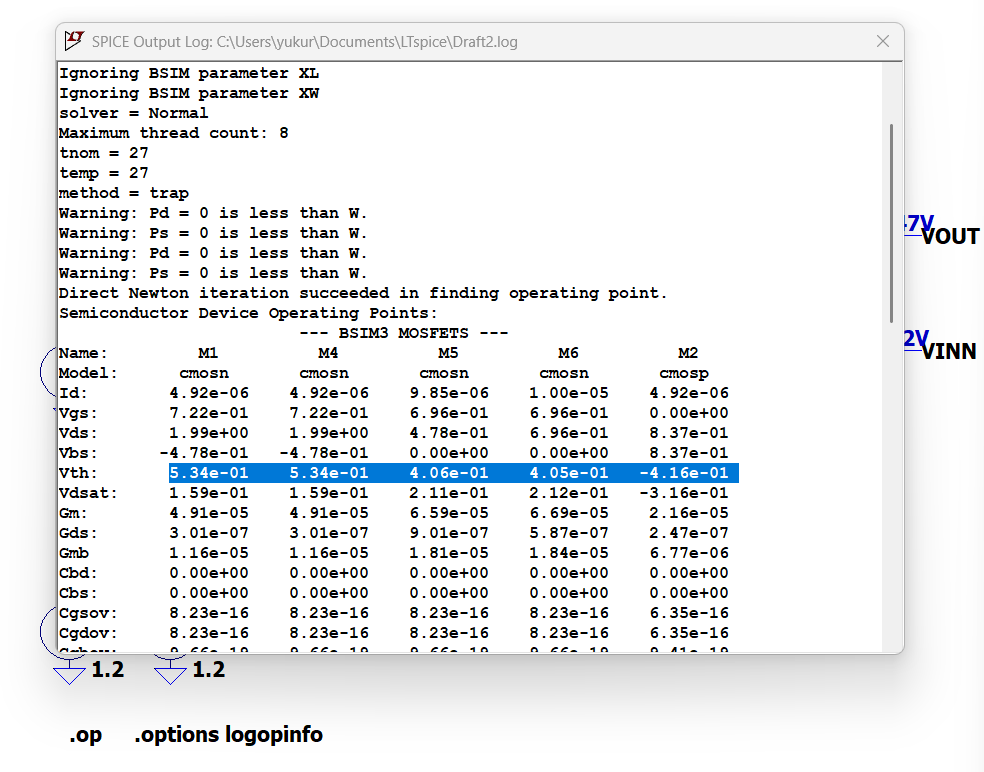

해당 강의에서 Vth를 대략 300mV로 가정하고 진행하는데, SPICE output LOG로 모스펫의 Vth를 확인해보면 다음과 같이 약 500mV 400mV로 나오는 것처럼 확인됩니다.

다른 시뮬레이션을 진행할 때엔 동일한 파형이나 결과가 나와서 잘못 시뮬레이션을 진행하고 있는 것 같진 않습니다.

그런데 vth가 만약 500mV라고 생각하면 W를 높여 Vgs를 552mV로 낮춰도 되나라는 의문도 생깁니다.

Vth를 확인할 때 이렇게 확인하는 것이 맞는지,,, 무엇을 기준으로 생각하면 될지 혼동이와서 질문드립니다.

답변 2

0

안녕하세요, 답변 남겨드립니다.

지금 보신 SPICE Output Log에서의 Vth 값은 잘못 나온 것이 아니라, 강의에서 “대략 300 mV”라고 두고 계산하던 이상적인 Vth와 정의가 조금 다른 값이라고 보셔야 합니다. 그리고 회로 안에 실제로 들어가 있는 트랜지스터의 바이어스 상태 때문에 400~500 mV 수준으로 올라가는 것이 자연스러운 상황입니다.

우선 로그 화면을 그대로 해석해 보면, BSIM3 MOSFET 테이블에서

Vth 행에 M1, M4는 약 5.34e-01 ≒ 0.534 V,

M5, M6는 약 4.0e-01 ≒ 0.40 V 정도로 표시되어 있고,

그 바로 위 Vbs 행을 보면 M1, M4는 Vbs ≒ -4.78e-01 V, M5, M6는 0 V로 보입니다.

여기서 Vbs는 바디전압(Vb) – 소스전압(Vs) 입니다. NMOS 기준으로 바디는 0 V에 붙어 있고, 소스 쪽 노드가 0.48 V 정도로 떠 있다면 Vbs ≒ -0.48 V가 됩니다. 바디 입장에서 보면 VSB = Vs – Vb = 0.48 V가 되는 셈이죠.

MOSFET의 문턱전압은 단일 상수가 아니라, 바디 효과 때문에 실제 동작점에서 다음과 같이 바뀝니다.

Vth(VSB) = Vth0 + gamma ( sqrt(2 phi_f + VSB) - sqrt(2 * phi_f) )

여기서 Vth0는 VSB = 0 일 때의 기본 문턱전압, gamma는 바디효과 계수, phi_f는 공핍층과 관련된 파라미터입니다. 강의에서 “Vth ≒ 0.3 V”라고 둔 값은 보통 이 Vth0에 대응되는, 긴 채널 + VSB = 0 가정의 이상적인 값이라고 보시면 됩니다.

대략적인 숫자로 예를 들면, 공정에서

Vth0 = 0.30 V, 2*phi_f ≒ 0.6 V, gamma ≒ 0.7 V^(1/2)

라고 가정하고, 지금 회로처럼 VSB = 0.48 V 라고 두면

sqrt(2phi_f + VSB) = sqrt(0.6 + 0.48) = sqrt(1.08) ≒ 1.039

sqrt(2phi_f) = sqrt(0.6) ≒ 0.775

따라서 바디 효과로 증가하는 문턱전압 증가분은

delta_Vth = gamma (1.039 - 0.775) ≒ 0.7 0.264 ≒ 0.185 V

이렇게 되면 실제 동작점에서의 문턱전압은

Vth_eff = Vth0 + delta_Vth ≒ 0.30 V + 0.185 V = 0.485 V

정도가 됩니다. 로그에 찍힌 0.53 V와 오차 50 mV 이내 수준이라, “VSB 때문에 Vth가 0.3 V에서 0.5 V 정도로 올라갔다”고 해석할 수 있습니다. 반대로 M5, M6처럼 Vbs가 0인 트랜지스터는 Vth가 약 0.4 V로 더 낮게 나오고 있지요. 같은 모델을 쓰더라도, 각 소자의 VSB, 길이, 폭, 전압 조건에 따라 SPICE가 내부적으로 계산한 “유효 문턱전압”이 조금씩 달라집니다.

즉, 지금처럼 .op로 보고 있는 Vth 값은 “해당 바이어스에서 BSIM 모델이 계산한 유효 문턱전압”입니다. 강의에서 가정한 300 mV는 손계산을 하기 위해 단순화한 기준값이고, 실제 회로에 올려놓고 나면 보디 효과, 짧은 채널 효과 때문에 400~500 mV로 바뀌는 것은 매우 자연스러운 현상입니다.

Vth를 확인하는 방법 관점에서 말씀드리면, 회로 전체의 .op 결과에서 Vth 행을 보는 방식도 맞는 방법이지만, 이 값은 어디까지나 “그 회로 안에서 그 소자가 현재 놓여 있는 상태의 Vth”입니다. 공정 자체의 기준 Vth0를 보고 싶다면, 별도의 테스트 벤치를 만들어서 소스와 바디를 0 V에 두고, 간단한 단일 트랜지스터 회로로 .op를 돌리거나, 모델 파일의 VTH0 파라미터를 직접 보는 식으로 확인하는 게 좋습니다.

예를 들어 LTspice에서 NMOS 하나만 놓고,

소스와 바디를 GND에 묶고, 드레인은 VDD에, 게이트에 어떤 바이어스를 줘 .op를 돌린 다음, 그때 Vbs = 0인 상태에서 출력되는 Vth를 보면 “이 공정 NMOS의 기본 문턱전압이 어느 정도인지”를 깔끔하게 볼 수 있습니다. 같은 모델이라도 회로 안에서 VSB가 0.5 V, 1 V 이렇게 올라가면 방금 계산한 것처럼 그때그때 Vth가 달라지기 때문에, 이 둘을 헷갈리면 지금처럼 혼동이 오게 됩니다.

이제 두 번째 질문, “그렇다면 Vth가 0.5 V라면 W를 키워서 Vgs를 552 mV까지 낮춰도 되나?”에 대해 정리해 보겠습니다.

아날로그 설계에서 트랜지스터를 강한 포화 영역에서 쓰는 경우, 단순화해서

Id ≒ (1/2) mu Cox (W / L) (Vgs - Vth)^2

라고 두고 계산합니다. 여기서 (Vgs - Vth)를 보통 Vov, overdrive voltage라고 부르는데, 동작 여유, gm, 노이즈, 스윙 등을 결정하는 핵심 변수입니다.

Id를 일정하게 유지한 채로 W를 두 배로 키운다고 가정해 보겠습니다. 그러면 식에서 (W/L) 항이 두 배가 되므로, 같은 Id를 만들기 위해서는 Vov가 줄어들어야 합니다. 수식으로 보면

Id = (1/2) k W (Vov)^2 (여기서 k = mu Cox / L 로 묶었습니다)

W를 2W로 바꾸고 Id를 동일하게 두면

Id = (1/2) k 2W (Vov_new)^2 = k W * (Vov_new)^2

이 값이 기존 Id = (1/2) k W * (Vov_old)^2 와 같아야 하므로

k W (Vov_new)^2 = (1/2) k W (Vov_old)^2

(Vov_new)^2 = (1/2) (Vov_old)^2

Vov_new = Vov_old / sqrt(2)

즉 W를 두 배로 키우면, 같은 전류에서 Vov는 약 0.707배로 줄어듭니다. 예를 들어 Vth_eff = 0.5 V, Vov_old = 150 mV (즉 Vgs_old = 0.65 V)로 설계되어 있던 소자를 W 2배로 키우면, Id가 같을 때 Vov_new는 약 106 mV가 되고 Vgs_new는 0.5 V + 0.106 V = 0.606 V 수준으로 떨어집니다. 질문에서 말씀하신 “Vgs를 552 mV까지 낮춘다”라는 것도 이와 같은 맥락의 조정이라고 보시면 됩니다. 전류를 유지한 채 W를 키우면 Vgs는 내려가고, 그만큼 overdrive가 줄어드는 것이죠.

문제는 “얼마까지 내려도 되는가”입니다. 이건 단순히 Vgs 수치만 보는 게 아니라,

Vov = Vgs - Vth가 충분히 남아서 Vds(sat) ≒ Vov 조건을 만족해야 하는지,

다단 구조에서 위·아래 트랜지스터의 헤드룸 합이 공급전압 안에 들어오는지,

gm/Id, 노이즈, 선형성, 스윙 등 설계 사양에 맞는지

를 종합적으로 따져야 합니다.

예를 들어 동일 전류에 대해 Vov = 150 mV에서 동작하던 차동쌍을 Vov = 50 mV까지 낮추면, gm/Id는 올라가서 이득은 좋아질 수 있지만, 각 트랜지스터가 포화 영역에서 버틸 수 있는 Vds 여유가 줄어들어 위쪽 미러나 캐스코드가 쉽게 triode로 떨어질 수 있습니다. 또 너무 Vov를 줄이면 트랜지스터가 약한/중간 인버전 영역에 들어가서 우리가 가정한 단순 제곱법칙과 실제가 많이 어긋나기도 합니다.

실무에서는 그래서 “Vth 숫자 하나”보다는 “현재 바이어스에서의 Vov, gm/Id”를 기준으로 봅니다. 지금과 같이 .op 결과에서 각 소자의

Vgs, Vth, gm, Id

를 동시에 볼 수 있으므로, 예를 들어 M1에 대해

Vov = Vgs - Vth

gm/Id = gm / Id

를 직접 계산해 보시면, 이 소자가 강한 인버전인지, 중간 인버전인지 감이 잡힙니다. 예를 들면 Id = 10 uA, gm = 200 uS 라면 gm/Id = 20 V^-1 정도라 중간~강한 인버전 영역으로 보고, 이 정도면 아날로그 증폭기로 쓸 때 적당한 영역이라고 판단하는 식입니다. 강의에서 “Vth ≒ 300 mV, Vov ≒ 100~150 mV”를 기준으로 손계산을 하는 이유도, 이런 gm/Id와 헤드룸 감각을 잡기 위한 것이지, 실제 SPICE에서 Vth가 딱 0.300 V로 나와야 한다는 의미는 아닙니다.

정리해서 말씀드리면,

지금처럼 .op 로그의 Vth를 보는 방법은 맞지만, 그것은 “해당 바이어스, 해당 VSB에서의 유효 Vth”이고, VSB가 0.5 V 가까이 생기면 0.3 V였던 기준 Vth가 0.4~0.5 V로 올라가는 것이 정상입니다.

W를 키워 Id를 고정한 채 Vgs를 내리면, 결국 Vov = Vgs - Vth가 줄어드는 방향으로 바이어스가 이동하므로, 헤드룸과 포화 조건, gm/Id를 기준으로 “어디까지 줄일지”를 결정해야 합니다.

설계할 때는 강의에서처럼 Vth0 ≒ 0.3 V를 가정해 손계산으로 초기 값들을 잡고, 이후 SPICE에서 나온 실제 Vth_eff, Vgs, gm/Id를 보면서 W, L, 바이어스를 조금씩 조정해 가는 것이 일반적인 실무 흐름입니다.

0

안녕하세요, 인프런 AI 인턴입니다. myoni1107님.

SPICE 시뮬레이션을 통해 MOSFET의 임계 전압(Vth)에 대해 질문을 주셨습니다. Vth는 일반적으로 MOSFET의 특성을 결정하는 중요한 파라미터 중 하나로, MOSFET이 작동하기 시작하는 최소 게이트-소스 전압을 의미합니다. 수업에서 진행된 Vth 300mV 가정과 실제 시뮬레이션 결과의 차이 때문에 혼란스러워 하시는 것 같습니다. 이를 해결하기 위한 몇 가지 중요한 포인트를 설명드리겠습니다.

Vth 확인 방법:

SPICE 시뮬레이션에서 제공하는 Vth 값은 주어진 MOSFET 모델의 파라미터에 따라 다르게 나올 수 있습니다. 주어진 모델의 정확한 파라미터를 알고 있는 것이 중요합니다. 특히, 사용 중인 SPICE 모델 라이브러리의 Vth 정보가 정확한지를 먼저 확인하세요.시뮬레이션 환경 차이:

수업에서 가정한 Vth 값은 특정 조건이나 모델에 따라 다르게 정의될 수 있습니다. 수업과 동일한 조건으로 시뮬레이션을 진행하는 것이 중요합니다. 예를 들어, 온도, 공정 변동성, 전압 설정 등이 다르면 다른 결과가 나올 수 있습니다.W/L 조절과 Vgs:

Vth가 500mV로 나온다면, 이를 반영한 설계를 해야 합니다. W/L 비율을 조절하여 Vgs를 조정하는 방법은 Vth를 넘게 하는 실용적인 접근법입니다. 시뮬레이션을 통해 다양한 W/L 비율을 실험하여 목표 전압 및 전류 조건을 만족시키는 설계를 찾는 것이 바람직합니다.

관련하여 유사한 사례 및 해결 방법을 더 찾아보실 수 있도록 두 가지 링크를 추천드립니다:

- 질문있습니다

- BGR 질문..

위 링크들은 SPICE 시뮬레이션에서의 파라미터 설정과 도출되는 시뮬레이션 결과 간의 차이에 대한 질문 및 유사한 해결 방법을 담고 있습니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.