no data path질문

103

작성한 질문수 1

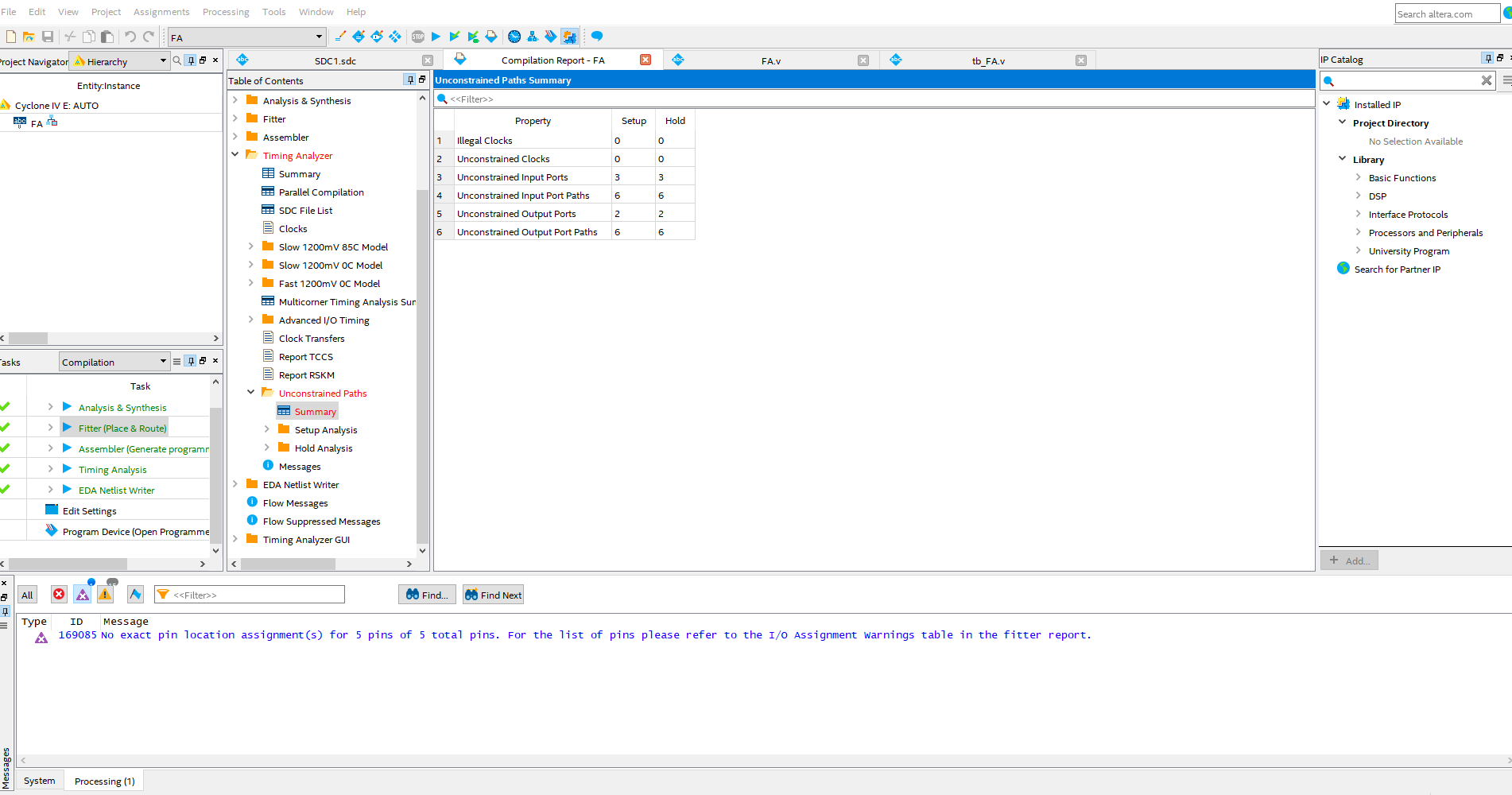

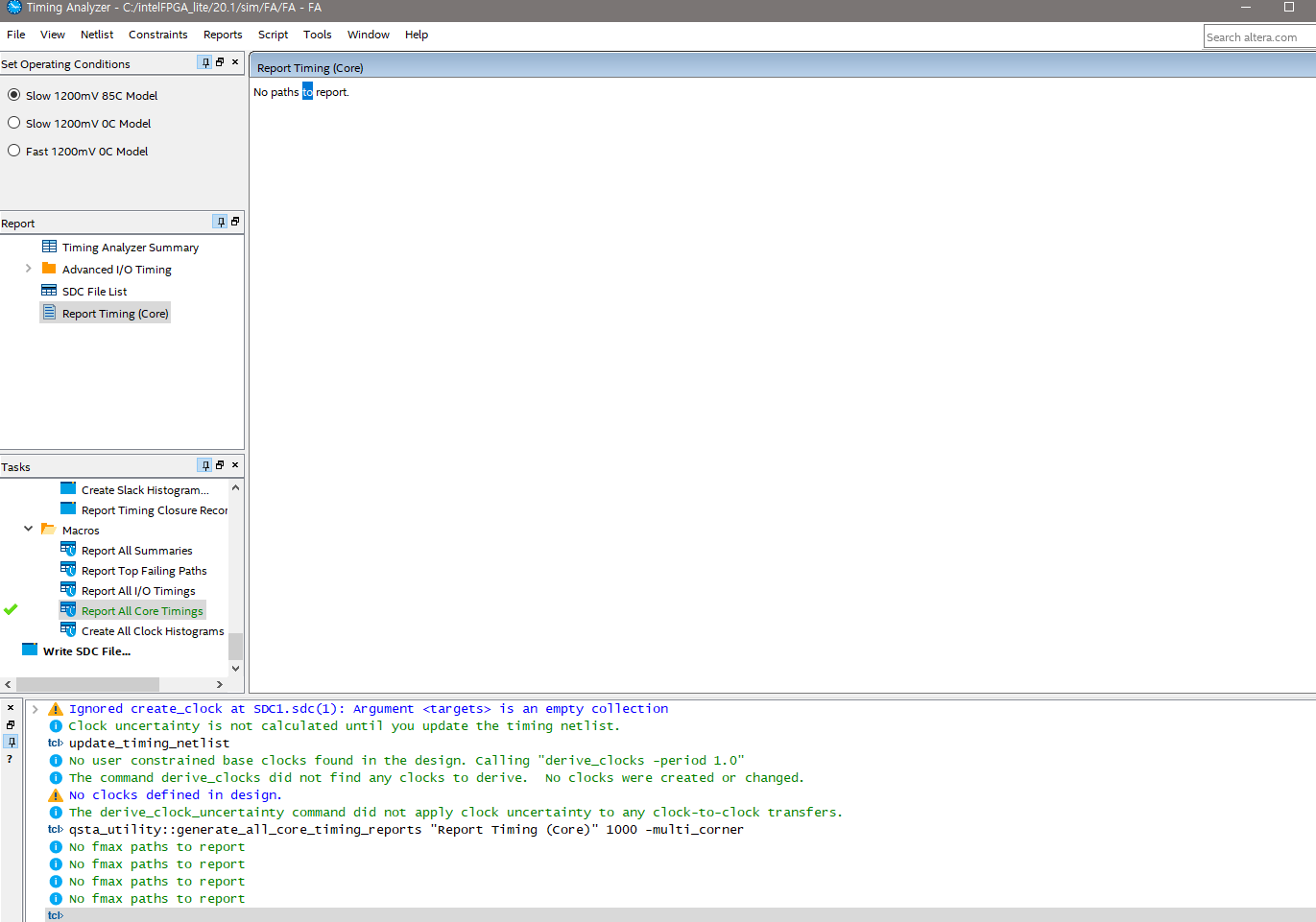

full_adder설계 테스트 벤치 설계, 시뮬레이션확인, sdc파일 입력 및 합성을하고 timing analyze를 확인해보는데 계속 no path라고 나옵니다.. 뭘 놓친건지 모르겠습니다. 강의 그대로했는데 뭐가 문제일까요 ㅠㅠ

답변 3

0

저도 똑같이 떴었는데 , 보니까 top module 설정을 잘못해서 합성하니까 FA_4bit이 아니라 FA만 합성되었더라구요.

top module을 FA_4bit으로 설정하시면 될거에요 !

0

안녕하세요, 답변 남겨드립니다.

강의 내용 그대로 따라했는데 “no path”가 나왔다면

합성된 Top module에 clk 포트가 실제 존재하는지,

create_clock 구문이 해당 포트명과 일치하는지,

Timing Analyzer 실행 시 SDC가 실제로 적용되었는지를 확인해보셔야 합니다.

Quartus나 Vivado에서는 흔히 SDC가 “unconstrained” 상태로 빠지는 경우가 있어, GUI 상에서 Constraint Assignment 창에서 파일을 수동으로 추가해야 정상 동작합니다.

즉, 강의의 절차는 맞더라도 현재 사용 중인 Tool의 버전 차이 또는 Clock 포트 미인식으로 인해 Analyzer가 Path를 탐색하지 못하는 것이 원인일 가능성이 높습니다.

0

안녕하세요, 인프런 AI 인턴입니다. 지창훈님.

디지털 회로설계에서 Timing Analysis를 진행할 때 “no path”라고 나오는 문제로 인해 어려움을 겪고 계신 것 같습니다. 이 문제는 일반적으로 설정된 타이밍 경로가 없거나 설정이 올바르지 않을 때 발생합니다. 다음은 이 문제를 해결하기 위한 몇 가지 점검 사항입니다:

점검 사항

SDC 파일 확인:

- SDC 파일에서 시계 생성(Create Clock) 구문이 정확하게 작성되었는지 확인하세요. 예를 들어, 아래와 같은 구문이 필요합니다:

create_clock -name clk -period 10.0 [get_ports {clk}]

- 타이밍 경로의 시작과 끝 지점을 명확히 설정했는지 확인하십시오. 경로가 정의되지 않으면 “no path” 메시지가 나타날 수 있습니다.

- SDC 파일에서 시계 생성(Create Clock) 구문이 정확하게 작성되었는지 확인하세요. 예를 들어, 아래와 같은 구문이 필요합니다:

핀 정렬(Pin Assignment):

- 모든 핀이 올바르게 할당되었는지 확인하세요. 정렬되지 않은 핀은 타이밍 분석에 영향을 미칠 수 있습니다.

- 모든 핀이 올바르게 할당되었는지 확인하세요. 정렬되지 않은 핀은 타이밍 분석에 영향을 미칠 수 있습니다.

Compile 및 Netlist:

- 전체 프로젝트의 컴파일이 제대로 완료되었는지 확인합니다. 중간에 에러가 발생하면 타이밍 분석이 정확히 실행되지 않을 수 있습니다.

- 전체 프로젝트의 컴파일이 제대로 완료되었는지 확인합니다. 중간에 에러가 발생하면 타이밍 분석이 정확히 실행되지 않을 수 있습니다.

Clock Domains:

- 여러 클럭 도메인이 존재할 경우, 각 도메인에 대한 타이밍 경로가 명확히 설정되어 있는지 확인합니다.

- 여러 클럭 도메인이 존재할 경우, 각 도메인에 대한 타이밍 경로가 명확히 설정되어 있는지 확인합니다.

추가 참고 자료

위의 점검 사항들을 한번 더 검토해보시고, 문제가 계속되면 구체적인 오류 메시지나 로그를 참고하여 더 자세한 원인을 분석하는 것이 좋습니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다. 현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏 추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

강의 만료일 연장 신청

0

34

2

강의자료 pdf파일

0

89

2

수강기간변경

0

75

2

프로그램 종류

0

90

1

안녕하세요 강의 도중 궁금한 점 있어서 질문드립니다!

0

87

1

수강기간 변경관련

0

65

2

수강기간 만료

0

72

2

수강 연장 문의

0

71

2

I2C SCL_Synched, SDA_Synched 질문

0

84

1

SRAM 강의 modelsim 시뮬레이션에서 inner 메모리를 Objects 리스트에서 찾으려고 하는데 안보입니다.

0

89

2

DataMem 스펙 질문

0

54

1

Hamming Code 질문

0

66

1

W_CRC 값 질문하기

0

60

1

Precharge에 대한 질문

0

167

1

tpsram spec 질문

0

65

2

학습 관련 질문 있습니다!

0

88

2

[과제7] AXI 통신 프로토콜 설계하기 문의드립니다

0

94

2

SRAM 강의 TB 작성 후 waveform 확인시에 dout이 모두 don't care 처리 관련 질문드립니다.

0

106

5

SRAM Interface Behavior(Diagram) 질문

0

133

3

vivado와 quartus 프로그램의 systhesis 결과 차이에 대해 궁금한 점 있습니다

0

185

2

tool 질문

0

93

2

CDC 메타스태빌리티 질문

0

67

1

SRAM module RTL viewer 이상

0

97

2

slave와 master 시뮬레이션

0

67

2