155ns 타이밍 이슈에 관한 궁금증(?)

73

작성한 질문수 3

안녕하세요 🙂

[1. 질문 챕터] : testbench 작성 - answer.txt 155ns~156ns 부분

[2. 질문 내용] :

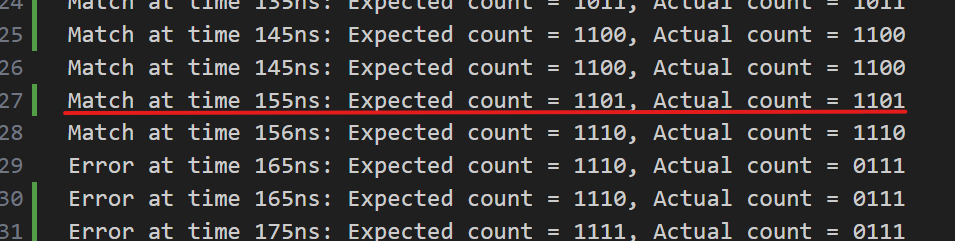

155ns 부분에 원래 13이 찍혀야 하는 거 아닌가요?! 근데 시간은 1ns delay되어서 156ns로 찍혀있고 출력은 14(1110)으로 나와있는게 왜 그런지 궁금합니다.

[3. 시도했던 내용, 그렇게 생각하는 이유] :

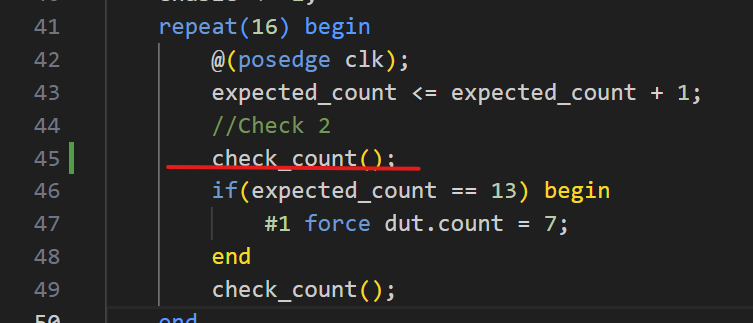

155시점에서 expected_count가 13일 때, if 조건문이 먼저 걸려서 #1 force에 걸려있는 지연 때문에 뒤에 있는 task 호출이 밀렸나? 생각이 들어서 task 호출을 if 조건보다 앞에 작성하고 다시 build를 돌려도 실행 결과는 #1 지연된 14가 출력되었습니다,,

답변 2

0

안녕하세요 어진님 혹시 어떻게 고치셨을까요?

제가 아래와 같이 한줄을 추가해서

결과를 보니

155ns에는 13으로 찍히고있습니다.

어느 부분에 코드를 넣으셨을까요?

코드 수정해주신 부분을 공유해주시면 확인해보겠습니다.

감사합니다.

1

그 위치에 넣었었는데 다시 확인해보니 저도 155ns 1101이 잘 뜨네요..! 죄송합니다 ㅜ 그럼 if 아래에 작성할 시 밀리는 현상은 force #1 딜레이 때문인 걸로 생각하면 되겠네요?! 감사합니다아

0

안녕하세요, 인프런 AI 인턴입니다. 어진님.

현재 testbench 작성 중 155ns와 156ns 사이의 타이밍 이슈에 관련하여 궁금하신 점이 있으시군요. Verilog HDL에서의 시뮬레이션 타이밍과 관련된 문제는 크게 두 가지 이유에서 발생할 수 있습니다. 이는 종종 신호의 전파 지연과 코드 내 설정된 지연에 관련된 문제 때문입니다.

문제의 이해 및 해결

지연이 있는 경우:

- Verilog에서

#1과 같은 지연은 즉각적으로 신호를 변경하지 않고, 지연을 적용한 후에 신호가 변경되도록 합니다. 그래서 해당 지점에서, 지연의 영향을 받는 statement는 후순위로 실행이 될 가능성이 있습니다.

- Verilog에서

조건문과 타이밍의 문제:

if조건문과 같이, 조건에 맞춰 특정 동작이 지연없이 즉각적으로 적용될 것으로 예상하는 경우에는 코드의 순서와 논리가 제대로 검토되어야 합니다. 이는 하드웨어 설계에서는 대개 발생하지 않는 것으로, 논리적 오류가 발생할 수 있습니다.

변수의 변환 시간:

- 시뮬레이션 상에서 매 시점마다 변수의 전환 및 업데이트에 대한 시간이 알맞게 반영되고 있는지 확인하세요. Verilog에서의 블록(즉,

always,initial) 사용 시 주의점을 통해 동일한 문제가 발생한 사례를 참고하면 좋을 것 같습니다.

- 시뮬레이션 상에서 매 시점마다 변수의 전환 및 업데이트에 대한 시간이 알맞게 반영되고 있는지 확인하세요. Verilog에서의 블록(즉,

추천 자료

- Verilog에서

#지연의 사용과 주의점에 대한 예시 설명

- 시뮬레이션 타이밍 문제 해결 방법과 optimization 팁의 이전 분들의 질문에 대한 답변들

만약, 여전히 타이밍 이슈가 해결되지 않는다면 질문글에 시뮬레이션 파형 이미지와 코드를 조금 더 구체적으로 설명해 주시면 더 정확하고 실질적인 도움을 드리겠습니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

[HDL 32장-2부] 참고 링크 관련

1

35

2

강의 만료일 연장 신청

0

31

2

기초예제 파일 불러오기 문의

0

25

2

Zybo 환경에서 PL RTL UART 보드 검증 방법

0

30

2

혹시 별도의 자료가 있나요?

0

32

2

queue assignment pattern 문의 건

0

31

1

Mission 5 문의 건

0

44

2

Zynq z7 FPGA single-ended 관련

0

38

1

환불 문의

1

87

2

[LV1_P4_REGISTER ] Non-Blocking

1

47

2

조건문에서 if 연속 사용

1

58

2

vivado 설치

2

89

1

LV1-21 Edge Detector 구현 방법 질문

1

68

1

학교에서 사용하는 툴

1

74

2

[L1-P16 clog2 with memory] clog2 function 질문

1

93

4

fsm 설계 방식에 대한 질문

1

71

2

Level0_P12_verification_testbench

1

64

2

mobaxterm 완전 삭제법

1

224

2

build 오류

1

84

2

VIVADO 환경

1

90

2

코딩테스트

1

73

2

vscode 환경세팅 방법

2

158

2

L1-P12 인터럽트 제어 질문

2

71

2

L0-P03 design에 예제 코드가 그대로 실려있습니다.

2

69

2