[L1-P16 clog2 with memory] clog2 function 질문

93

작성한 질문수 17

안녕하세요 ETA님 추운 날씨 고생 많으십니다.

clog2 function과 관련하여, 질문 사항이 있습니다.

문제 풀 당시 모범 답안과 다르게, function 안에서 DEPTH에 따라 나누어 출력(clog2) 값을 뽑아 내도록 설계 했습니다.

function integer clog2(input DEPTH);

begin

if(DEPTH == 1) begin

clog2 = 0;

end

else if(DEPTH >= 2 && DEPTH < 4) begin

clog2 = 1;

end

end

endfunction

위와 같이 설계한 결과, 아래 사진과 같이 write하지 않은 address에 대해 read할 경우 address = 5번지에 쓴 값이 읽히게 됩니다.

이에 대해 가이드 주시면 감사하겠습니다. (모범 답안이 올바른 설계 방법인 것을 알지만, 현재 저의 설계의 잘못점을 찾고 싶습니다.)

안녕하세요 🙂

[1. 질문 챕터] : eg) 몇 장, 몇 분 몇 초 쯤. or 수강생 분들이 봤을 때 어디구나?! 할 수 있게 표기 부탁 드려요.

[2. 질문 내용] : eg) 질문 내용을 자유롭게 작성해주시면 되겠습니다 🙂

[3. 시도했던 내용, 그렇게 생각하는 이유] : eg) 설치영상은 이렇게 시도했는데 안되더라 or 본인의 생각을 적어주세요. (실습 내용 중에 이해가 안되거나 잘못된 내용이 있는데, 이러 이러한 근거로 나는 이렇게 생각합니다.)

================ 다음 내용은 읽어보시고 지우시면 됩니다.=================

질문 내용을 작성해주실 때, 위의 3단계로 제가 이해할 수 있게 작성해주시면 정확한 답변을 드릴 수 있을 것 같아요!!

현업자인지라 업무때문에 답변이 늦을 수 있습니다. (길어도 만 3일 안에는 꼭 답변드리려고 노력중입니다 ㅠㅠ)

강의에서 다룬 내용들의 질문들을 부탁드립니다!! (설치과정, 강의내용을 듣고 이해가 안되었던 부분들, 강의의 오류 등등)

이런 질문은 부담스러워요.. (답변거부해도 양해 부탁드려요)

개인 과제, 강의에서 다루지 않은 내용들의 궁금증 해소, 영상과 다른 접근방법 후 디버깅 요청, 고민 상담 등..

글쓰기 에티튜드를 지켜주세요 (저 포함, 다른 수강생 분들이 함께보는 공간입니다.)

서로 예의를 지키며 존중하는 문화를 만들어가요.

질문글을 보고 내용을 이해할 수 있도록 남겨주시면 답변에 큰 도움이 될 것 같아요. (상세히 작성하면 더 좋아요! )

먼저 유사한 질문이 있었는지 검색해보세요.

잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

==================

답변 4

1

안녕하세요 ETA님 바쁘신데 답변 감사드립니다.

아래는 전체 저의 코드입니다. 모범 답안에서 차이점은 clog2 function 부분 밖에 없습니다.

`timescale 1ns / 1ps

// Design a module according to the following requirements

// Memory size: Width: 8 bits, Depth: DEPTH(parameter)

// Design a clog2 function (calculate log base 2 and round up). The clog2 is used for the address width.

// The memory interface operation should follow the timing diagram shown below.

module clog2 #(

parameter DEPTH = 256

)(

input wire clk,

input wire rst,

input wire we,

input wire [clog2(DEPTH)-1:0] addr,

input wire [7:0] din,

output reg [7:0] dout

);

//TODO

function integer clog2(input DEPTH);

begin

if(DEPTH == 1) begin

clog2 = 0;

end

else if(DEPTH >= 2 && DEPTH < 4) begin

clog2 = 1;

end

else if(DEPTH >= 4 && DEPTH < 8) begin

clog2 = 2;

end

else if(DEPTH >= 8 && DEPTH < 16) begin

clog2 = 3;

end

else if(DEPTH >= 16 && DEPTH < 32) begin

clog2 = 4;

end

else if(DEPTH >= 32 && DEPTH < 64) begin

clog2 = 5;

end

else if(DEPTH >= 64 && DEPTH < 128) begin

clog2 = 6;

end

else if(DEPTH >= 128 && DEPTH < 256) begin

clog2 = 7;

end

else if(DEPTH >= 256 && DEPTH < 512) begin

clog2 = 8;

end

else if(DEPTH >= 512 && DEPTH <1024) begin

clog2 = 9;

end

else begin

clog2 = 1;

end

end

endfunction

reg [7:0] mem[0:DEPTH-1];

integer i;

always @(posedge clk or posedge rst) begin

if (rst) begin

dout <= 8'b0;

for (i = 0; i < DEPTH; i = i + 1) begin

mem[i] <= 8'b0;

end

end else if (we) begin

mem[addr] <= din;

end

dout <= mem[addr];

end

endmodule해당 코드 컴파일 시 컴파일 에러는 발생하지 않습니다. 혹시 컴파일 에러를 공유해주실 수 있을지 질문 드리고 싶습니다..

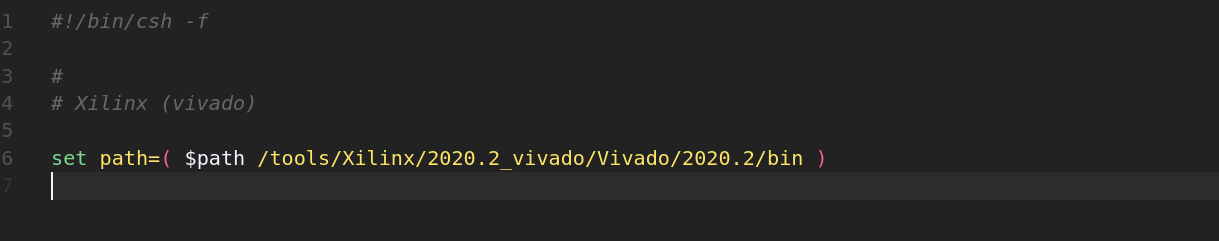

추가로 현재 제가 사용하고 있는 xilinx version은 2020.2입니다. 하지만 xilinx version에 따라 컴파일 에러가 달라질 거라고 생각은 하지 않지만, 일단 공유 드립니다.

감사합니다.

0

안녕하세요 항상 감사하면 살기님,

우선 컴파일 에러에 대해서 말씀드리겠습니다.

위에서 주어진 코드는 아래 와같은데요 이경우 에러가 납니다. 아마 그대로 복사하시면 에러가 발생 하실겁니다. 그래서 전체코드를 요청드린겁니다.

function integer clog2(input DEPTH);

begin

if(DEPTH == 1) begin

clog2 = 0;

end

else if(DEPTH >= 2 && DEPTH < 4) begin

clog2 = 1;

end

end

endfunction답글로주신 전체 코드로는 에러가 발생되지 않습니다.

Error 부분에 대해 말씀드리면

잘못된 부분에 대해서 말씀드리면function integer clog2(input DEPTH);

이 부분 입니다. 입력에 integer 라는 부분이 빠져있어서 function의 입력은 1bit으로 인식됩니다.그래서 addr 이 1bit 으로 선언이 되었습니다.

따라서 아래처럼 수정하시면 정상동작 하실거라 생각이듭니다.

function integer clog2(input integer DEPTH);하나 추가로 말씀드리고싶은것은 아래코드인데요. 아래코드의

dout <= mem[addr]; 위치가 rst의 else 조건 외부에 있습니다. 리셋이 1인 경우 두 군데에서 값을 할당하게되면서 unknown 혹은 0이 아닌 값이 dout에 할당될 수 있습니다. 실제 합성이나 디자인 룰체크 시에 문제가 될수있는 부분이라서 rst의 else 조건에 해당 코드를 옮겨주시기 바랍니다.

always @(posedge clk or posedge rst) begin

if (rst) begin

dout <= 8'b0;

for (i = 0; i < DEPTH; i = i + 1) begin

mem[i] <= 8'b0;

end

end else if (we) begin

mem[addr] <= din;

end

dout <= mem[addr];

end

좋은 시도에 다시한번 따봉 드립니다!

혹시 더 궁금하신점이 있다면 말씀부탁드립니다.

0

안녕하세요 항상 감사하면 살기님,

다른 방법(모범답안이 아닌 본인의 것)으로 접근하시는 것은 정말 좋은 시도입니다.

음 제가 모범답안에서 function 부분만 위에 언급 주신걸로 변경했을땐 컴파일 에러가발생하는데요.

function말고 수정하신 포인트들이 더 있으신가요(DEPTH 값을 변경하셨다던가)?

전체 코드를 공유해주시면 좀 더 명확하게 말씀드릴수있을것 같아요.

0

안녕하세요, 인프런 AI 인턴입니다. 항상 감사하면 살기님.

clog2 함수의 설계 문제에 대해 설명해 드리겠습니다.

질문 요약 및 분석

현재 코드의 문제점:

- DEPTH값을 직접 비교해서 clog2 값을 지정하는 방식은 유연성이 떨어집니다. 현재 함수는 DEPTH의 값을 특정한 경우만 다루고 있으며, 그 외의 경우는 기본값을 주지 않아 문제가 발생할 수 있습니다.

- 특히나 read operation에서 write하지 않은 주소에 대한 데이터가 잘못 읽히는 문제로 이어질 수 있으며, 이 문제는 설계된 메모리의 주소 길이가 잘못 계산돼 Addressing이 틀리게 설정됐기 때문일 수 있습니다.

- DEPTH값을 직접 비교해서 clog2 값을 지정하는 방식은 유연성이 떨어집니다. 현재 함수는 DEPTH의 값을 특정한 경우만 다루고 있으며, 그 외의 경우는 기본값을 주지 않아 문제가 발생할 수 있습니다.

함수 설계의 개선:

- DEPTH 값에 대한 직접 비교 대신, clog2 함수를 통해 DEPTH에 따라 필요한 clog2(N) 값을 자동 계산하는 것이 더 효율적입니다. 이는 다양한 DEPTH 값에서도 정확한 주소 길이를 보장해 줍니다.

- DEPTH 값에 대한 직접 비교 대신, clog2 함수를 통해 DEPTH에 따라 필요한 clog2(N) 값을 자동 계산하는 것이 더 효율적입니다. 이는 다양한 DEPTH 값에서도 정확한 주소 길이를 보장해 줍니다.

함수 설계 예시

아래 코드처럼 일반적인 clog2 함수를 사용하면 다양한 DEPTH에 맞추어 정확한 clog2 값을 얻을 수 있습니다.

function integer clog2;

input integer value;

integer i;

begin

clog2 = 0;

for (i = 0; value > 1; i = i + 1) begin

value = value >> 1;

clog2 = i + 1;

end

end

endfunction

위 함수는 주어진 전체 DEPTH에 대해 필요한 address bit width를 정확히 계산하여 반환합니다.

추가적인 도움이 될 수 있는 링크

유사한 상황에서 문제를 해결한 사례가 논의된 링크를 확인하시면 도움이 될 수 있습니다.

- Can Someone Explain How Clog2 Function Works? - Edaboard

- Determine Address Width in Verilog HDL with Clog2 - Intel Community

이해를 돕기 위한 간단한 설명과 구조를 제공하여, clog2의 설계 및 사용 방법에 관한 문제를 분석해 보았습니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다. 현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏 추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

[HDL 32장-2부] 참고 링크 관련

1

35

2

강의 만료일 연장 신청

0

33

2

기초예제 파일 불러오기 문의

0

25

2

Zybo 환경에서 PL RTL UART 보드 검증 방법

0

30

2

혹시 별도의 자료가 있나요?

0

33

2

queue assignment pattern 문의 건

0

33

1

Mission 5 문의 건

0

46

2

Zynq z7 FPGA single-ended 관련

0

40

1

환불 문의

1

87

2

[LV1_P4_REGISTER ] Non-Blocking

1

47

2

조건문에서 if 연속 사용

1

58

2

vivado 설치

2

89

1

LV1-21 Edge Detector 구현 방법 질문

1

68

1

학교에서 사용하는 툴

1

74

2

fsm 설계 방식에 대한 질문

1

71

2

Level0_P12_verification_testbench

1

64

2

mobaxterm 완전 삭제법

1

225

2

155ns 타이밍 이슈에 관한 궁금증(?)

1

73

2

build 오류

1

84

2

VIVADO 환경

1

90

2

코딩테스트

1

74

2

vscode 환경세팅 방법

2

158

2

L1-P12 인터럽트 제어 질문

2

71

2

L0-P03 design에 예제 코드가 그대로 실려있습니다.

2

69

2