TPSRAM 구조 관련하여 질문 있습니다!

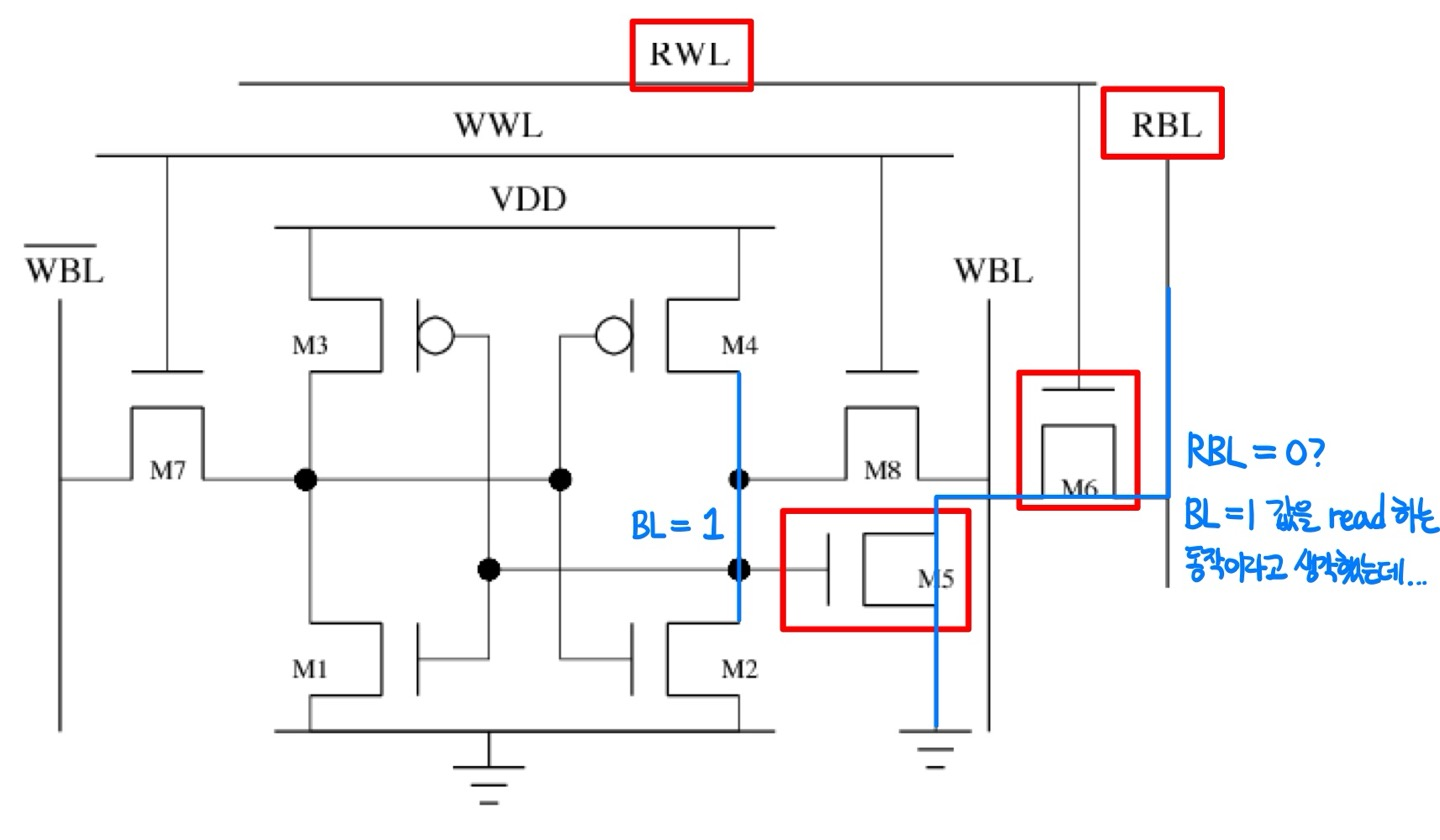

8T TPSRAM 구조를 설명하는 부분에서, BL와 BLB 방향 관련하여 질문이 있습니다.

RWL = 1 RBL = 1이 되어 BL값을 볼 수 있는 상태에서, 해당 구조에서는 BL = 1이 되면 M5가 켜져서 0을 읽는 부분이 제가 생각하는 동작과 반대로 된다고 생각했습니다.

만약 BL = 1인 상황에서 1의 값을 읽으려면 반대 방향의 인버터(M3, M1) 출력값인 BLB을 M5와 연결돼야 한다고 생각했는데, 이것이 맞는 생각인지 궁금합니다.

질문 읽어주셔서 감사합니다!

답변 1

0

네 안녕하세요, 답변 남겨드립니다.

말씀하신 상황을 생각해보면

M5가 열려있는 상태에서 M6가 열려있고, RBL = High인 경우를 말씀해주시는 걸까요?

만약 그렇게 되면 M5와 M6의 Ron 저항이 매우 작아서 leakage가 VDD to GND로 세는 상황이긴합니다!

1

네 맞습니다.

SRAM의 BL=1을 read하는 과정에서, BL=1에 의해 M5이 열리고, RWL=1에 의해 M6가 열리게 되면 결국 RBL=0이 되어 원하는 동작을 하지 못하는 걸로 이해했습니다.

TPSRAM의 read 동작에 대해 제가 이해한 것과 반대로 동작하는 것 같아서 질문 드립니다. 질문 읽어주셔서 감사합니다!

0

질문 이해했습니다.

실제 동작은 RBL에 0.4V 정도로 전압을 먼저 밀어준 다음에

M5와 M6가 열리면 RBL이 0이 되고, 이를 인버터를 태워서 1로 확인하게 됩니다.

역의 과정으로 BL 이 0이라면 0.4V가 센스엠프에 의해 1로 처리되어 인버팅된 0이라는 신호를 얻을 수 있습니다.

핵심은 인버터를 통과시킨다는 것입니다!

강의 만료일 연장 신청

0

33

2

강의자료 pdf파일

0

89

2

수강기간변경

0

75

2

프로그램 종류

0

90

1

안녕하세요 강의 도중 궁금한 점 있어서 질문드립니다!

0

87

1

수강기간 변경관련

0

65

2

수강기간 만료

0

72

2

수강 연장 문의

0

71

2

I2C SCL_Synched, SDA_Synched 질문

0

84

1

no data path질문

0

102

3

SRAM 강의 modelsim 시뮬레이션에서 inner 메모리를 Objects 리스트에서 찾으려고 하는데 안보입니다.

0

89

2

DataMem 스펙 질문

0

54

1

Hamming Code 질문

0

66

1

W_CRC 값 질문하기

0

60

1

Precharge에 대한 질문

0

167

1

tpsram spec 질문

0

64

2

학습 관련 질문 있습니다!

0

88

2

[과제7] AXI 통신 프로토콜 설계하기 문의드립니다

0

94

2

SRAM 강의 TB 작성 후 waveform 확인시에 dout이 모두 don't care 처리 관련 질문드립니다.

0

105

5

SRAM Interface Behavior(Diagram) 질문

0

133

3

vivado와 quartus 프로그램의 systhesis 결과 차이에 대해 궁금한 점 있습니다

0

185

2

tool 질문

0

92

2

CDC 메타스태빌리티 질문

0

66

1

SRAM module RTL viewer 이상

0

97

2