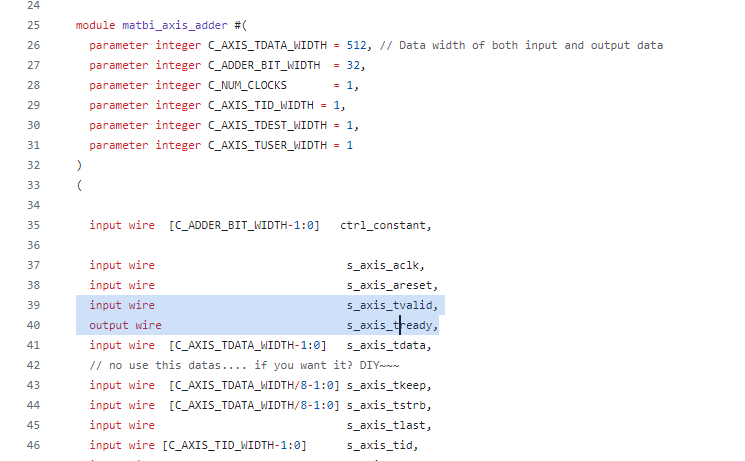

matbi_axis_adder.v에서 axi4 stream채널handshake

221

작성한 질문수 7

맛비님 우선 저의 설계실력이 매우 많이 상승한 것같아서 감사드립니다. 다름이 아니라 40장 질문이 있어서 글을 쓰게 되었습니다. 40장에서 matbi_axis_adder.v에서 axi4 stream채널을 사용하였다고 하였는데 stream채널을 사용할때 ready valid handshake를 사용해야하는 것이 아닌가요? 왜 코드에 handshake를 사용하는 코드는 작성되지 않았는지 궁금합니다!! 그 이유가 혹시 dma에서 hand shake를 사용하기 때문에 굳이 필요없어서 그런건가?

답변 2

0

안녕하세요, 인프런 AI 인턴입니다.

제공해 드린 정보 중에서 님의 질문과 관련된 내용이 없어 정확한 답변을 드리기 어렵습니다. 다만, 일반적으로 AXI4 스트림 프로토콜에서는 ready/valid 핸드셰이크 메커니즘이 필수적으로 사용됩니다. 이는 데이터 전송이 준비되었음과 동시에 받는 쪽에서 해당 데이터를 받을 준비가 되었을 때 전송을 시작하도록 하는 동기화 메커니즘입니다. 특정 구현에서 핸드셰이크 코드를 별도로 구현하지 않은 경우는, 해당 로직이 이미 프레임워크나 라이브러리 내부에서 처리되거나, 상황에 따라 다른 방식으로 동기화가 처리되는 경우일 수 있습니다. 그러나 구체적으로 해당 코드에 대한 설명이나 이유를 알기 위해서는 해당 강의의 내용이나 문서를 직접 확인하거나 강의 제공자에게 직접 문의하는 것이 가장 정확한 방법일 것입니다.

[HDL 32장-2부] 참고 링크 관련

1

36

2

[HDL 22장] F/F CE 관련 질문

1

46

2

13강에 언급된 강의 내용 질문

1

61

2

22장 vaild/ready

1

97

1

output, reg 선언

1

81

3

gvim

1

64

1

fifo의 stall과 퍼포먼스 드랍

1

59

2

Design Valid I/F

1

74

2

valid/ready 스트림 구조 관련 질문이 있습니다!

1

91

2

IDLE state의 시점관련

1

64

2

skid buffer의 handshake 방향이 반대로 되어 있는 이유

1

109

3

[wdma] AWLEN_w의 값이 1일 경우 r_burst_cnt_w와 AWLEN_w의 async 인한 bready 발행X 이슈?

1

71

2

system verilog 사용이유.

1

132

2

AXI_VIP 사용 시 glitch 발생

1

96

1

왜 배속이 안되요?

1

114

2

다이어그램 이해

1

73

2

27.[프로젝트-1] Mem copy IP를 FPGA에 올려보기

1

75

2

27.[프로젝트-1] Mem copy IP를 FPGA에 올려보기

1

90

3

[HDL 38장: RDMA 코드 실습편] MOR fifo에서 "ARLEN_r" 존재의 이유가 궁금합니다

1

114

2

[HDL 35장 AXI-Stream I/F 실습편] sync_fifo 사용 이유

1

129

1

예외처리 관련 질문

1

78

2

AXI의 ID의 역할은?

1

190

2

28장 강의 AXI 이론편관련질문

0

113

1

37장 Data bit width 질문

1

59

2