alwayw구문의 작동 순서에 관해 문의드립니다.

279

작성한 질문수 1

Verilog를 이용한 FPGA 활용-기초 강의에서

첫번째 코드의 시뮬레이션의 결과가

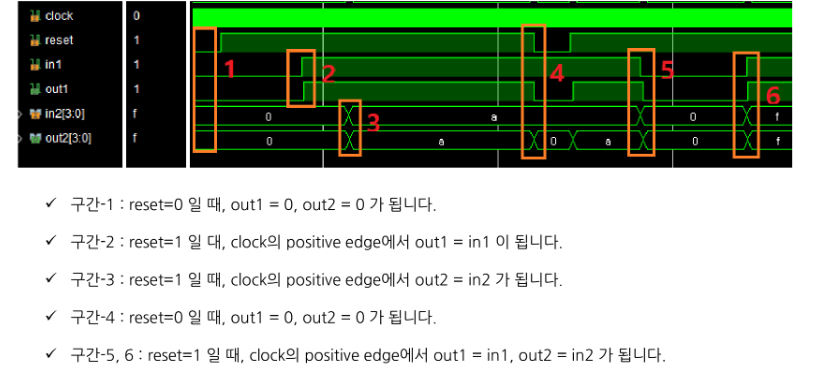

이렇게 나오는데 구간 2와 구간 3이 왜 같은 클락에서 발생하지 않고 2번 발생후에 3번이 발생하는지 모르겠습니다.

이렇게 나오는데 구간 2와 구간 3이 왜 같은 클락에서 발생하지 않고 2번 발생후에 3번이 발생하는지 모르겠습니다.

병렬적으로 코드 구현이 된다고 이해를 했는데 혹시 제가 놓친 코드가 있을까요

답변 2

0

24페이지의 소스코드를 보면, (라인 37) 강제로 딜레이 #133 (133ns)을 주었기 때문입니다.

in1을 1로 만들고, 133ns 딜레이 후에 in2의 값이 10으로 변경됩니다.

이는 simulation상에서는 delay를 사용자가 원하는 대로 줄 수 있습니다.

(실제로 코드를 합성할 때에는 이렇게 딜레이를 줄 수 없습니다)

[HDL 32장-2부] 참고 링크 관련

1

35

2

강의 만료일 연장 신청

0

32

2

기초예제 파일 불러오기 문의

0

25

2

Zybo 환경에서 PL RTL UART 보드 검증 방법

0

30

2

혹시 별도의 자료가 있나요?

0

32

2

Zynq z7 FPGA single-ended 관련

0

39

1

Differential Amp의 4가지 종류

0

41

1

[HDL 22장] F/F CE 관련 질문

1

45

2

UART0, 1 중 선택

1

50

2

fpga 개발보드

0

29

2

vivado 2022.1 version memory IP 구조

0

38

1

datamoverbram모듈질문

1

63

2

latency 개념 구현

1

84

3

13강에 언급된 강의 내용 질문

1

61

2

비바도 all os버전

1

67

2

초기화를 reset_n 이 '1'일 때가 아닌 '0' 일 때 실행시키는 이유 질문

1

68

2

Verilog를 이용한 FPGA 활용기초 37p 질문입니다.

0

74

2

10 bits * 10bits 연산 구현 질문

0

242

1

강의문의

0

287

1

오타 및 내용 수정이 필요합니다.

0

314

1

parts 선택 관련 문의드립니다 !

0

328

1

FPGA MCU Porting

0

547

1

reg 선언 후

0

402

2

행렬과 관련하여 문의드립니다.

1

374

1