FPGA uart 에러

744

작성한 질문수 5

안녕하세요. 항상 좋은 강의 잘 수강하고 있습니다.

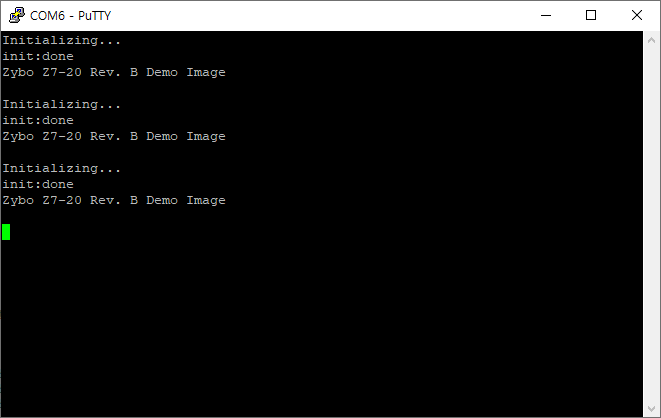

CNN을 fpga에 올리는 강의를 따라서 진행하고 있는데 아래와 같이 uart 통신 결과가 출력됩니다.

그래서 레퍼런스 문서들을 읽어보면서 이리저리 해보다 아래 사진의 파란색 부분을 qspi와 jtag를 연결하도록 하고나니 정상적으로 작동했습니다.

그 후에 몇가지 실험을 해보니 fpga 프로그래밍을 하기 위해서는 sd와 qspi가 연결되어 있어야했고 실제 동작할 때는 qspi와 jtag 연결한 상태이어야만 했습니다.

sd, sqpi, jtag에 대한 문서를 읽어봐도 제대로 이해가 가지 않아서 혹시 sd, qspi, jtag에 어떻게 연결하는지가 무엇을 의미하는지 알 수 있을까요??

감사합니다.

zybo z720을 사용하고 있고 강의 영상과 다른 점 없이 잘 진행되었는데 무엇이 문제인지 몰라 질문 드립니다.

감사합니다.

답변 2

0

참고로..

그래서 레퍼런스 문서들을 읽어보면서 이리저리 해보다 아래 사진의 파란색 부분을 qspi와 jtag를 연결하도록 하고나니 정상적으로 작동했습니다.

위의 내용은 FPGA 1 장에서 다룹니다... 하하...

0

안녕하세요 :)

구글링과 문서가 정확할 것 같은데요.

이해가 안된다고 하셨으니.. (뇌피셜로) 제가 적어보자면

sd, sqpi, jtag에 대한 문서를 읽어봐도 제대로 이해가 가지 않아서 혹시 sd, qspi, jtag에 어떻게 연결하는지가 무엇을 의미하는지 알 수 있을까요??

Zybo board 에는 3가지의 부팅방법을 선택할 수 있는데요.

sd card 의 부팅 data 를 read 한다.

qspi 라는 I/F 를 통해서 prom 에 있는 부팅 data 를 read 한다.

jtag I/F 를 통해서 직접 부팅 data 를 download 시킨다.

그중 저희는 3번 방법을 취하고 있습니다.

1,2 번은 강의에서 다루지 않았고요. 찾아보시면 될 것 같아요.

즐공하세요 :)

[AI HW Lab2] CNN Verilog HDL Practice 1 (Simulation) - 문제설명편 ppt

1

106

2

[AI HW Lab1] CNN Core C 코딩 (Golden Model 만들기)

1

93

2

spartan7 fgga484보드

1

78

1

soft reset관련 질문드립니다!!

1

62

2

예제 코드 환경설정

1

75

2

HW 언어 for loop 해석

1

57

3

수업자료 관련 질문드립니다.

1

76

2

FPGA 기반 ASIC 설계 검증 시 다차원 배열 처리 방식 및 강의 수강 순서 고민

1

105

2

Fpga에 ai 가속기를 사용하는 이유

2

421

2

AI HW 11장 관련 질문드립니다.

1

114

2

소프트 맥스 관련 질문드립니다.

1

204

1

Data형태에 따른 AI가속기 구현 질문

1

223

1

cnn_core simulaiton

2

282

3

zynq z7 10 parameter 크기

1

208

2

ip 패키징 질문

1

287

1

Image 인식 가속 모델을 설계하려면

1

308

2

이 강의 수강을 위해 fpga 구입이 필요할까요?

2

368

2

혹시 AI 관련 강의도 Zybo Board가 필요한가요?

1

292

2

cnn_kernel.v 코드질문입니다.

1

198

1

6장2부 15분 12초 왜 feature map size가 변경되지 않나요?

1

256

2

zybo z7 케이블 관련 질문

1

363

1

CNN layer별 연산

1

274

2

CNN Core에 weight 와 input feature map 관련해서 질문있습니다!

1

261

1

Linux 및 외장 하드 사용에 관한 질문

1

270

2