設計独学味比の実戦 AI HW設計のためのバイブル、CNN演算完全征服

semisgdh

味と一緒にAIハードウェアの基本を勉強します。非メモリ設計の専門家として、優れたAI HWを設計するための必須知識が含まれています。

中級以上

Verilog HDL, FPGA, CNN

実務者と一緒に Verilog HDL を使用して、非メモリ半導体の設計の基本的な知識と経験を積んでみましょう。

学習した受講者のレビュー

5.0

한진규

"学生の場合、最初は価格が負担される可能性がありますが、聞くほど支払った価格以上の価値がある講義" Pipelineまで受講完了しました。早く良い受講評を残したい気持ちに耐えられなくてあらかじめ作成します。 卒業予定者なのに下半期大企業予備合格でメンタルが出た状態でした。 "職務で優遇するFPGA/Verilogでも勉強して次の支援の際にアピールしよう"という軽い心で受講を始めましたが、本当にこの分野に興味を持たせてくれた講義です。 (+耳にすっぽり詰まる説明と、難しいが粘り強くぶら下がって一つずつ理解していく過程は本当に興味深いです。) 早く頑強で疲れ練習して、スペックだけを見て自分で設計できるレベルに達したいと思います。その後、すぐにfpgaを使った様々な実習やプロジェクトも進めてみたいですね。良質の講義を提供していただきありがとうございます。

5.0

dos12345

5点あげるしかない講義でした。内容も詳しく説明してくれて、もしかしたら分からない部分があって質問すれば答えも早くしてくれてとても良かったです(もちろんグーグルや他の受講生たちの質問参考にすれば、何らかの問題はすべて解決されます。)。 特にお母さんのコンピュータ環境と私のコンピュータ環境が違ってvivadoをインストールするのは大変でしたが、速いフィードバックのおかげで無事にインストールできました。そして、新しいバージョンのvivadoのインストールビデオを再びアップロードしたようですが、この部分はとても良いです。これからも元気で長く講義してください!

5.0

움직이는YM

Verilogと非メモリ設計に興味がある方はぜひ一度 受講してみることをお勧めする講義です。 美味しさが些細な質問も本当によく受けてくれてフィードバックも早くて授業を聞くのに不便はありませんでした。 しかし、このような人にはお勧めできません。 Verilog文法のvも知らない方です。 私は最初にこのような状態で受講しましたが、verilog文法に の説明がほとんど出てこなかったので慌てた記憶があります。 お母さんもおおよそは説明していただきますが基本的なverilog文法程度は知って聞かなければ役に立ちます。 逆に学校でverilog授業を一度は聞いた方、 個人的にverilogを一度勉強したことがあった方は本当に役に立つと思います。 学校でも一人で勉強しながら学べなかった中核的な内容だけをよく扱っています。 総合的に推薦する講義です。

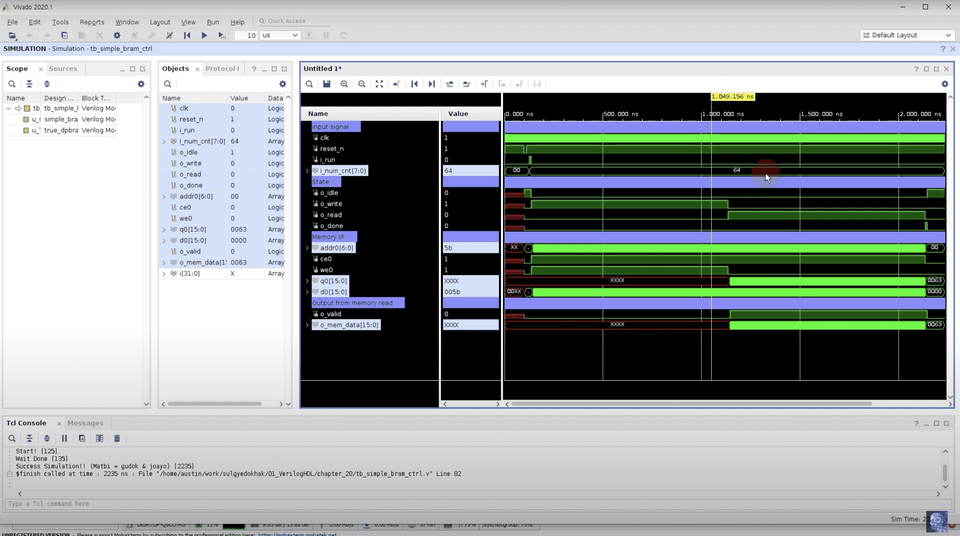

非メモリ半導体設計の基本知識

学校では学べない、実務者が設計した Verilog HDL 設計および検証方法

FPGA を始めるための設計基礎知識

現場で必要な設計知識! (ボーっとしないでください)

非メモリ設計エンジニアが教える

実戦 Verilog HDL: Clockから Internal Memoryまで!

インストールが最も困難です。

該当環境は皆様の設計人生に役立つことは間違いないので、インストールに成功された方は受講申請をお願いいたします。(インストール動画は無料公開中)

現業者のため、時間的にすべてのバージョンをサポートするのが困難で

講義で使用したインストール動画のバージョンに合わせてインストールをお願いいたします。vivado 2020.1 ~ vivado 2022.2 推奨

toolはtoolです。皆様にお伝えする設計知識とコードはtoolバージョンに影響されません。

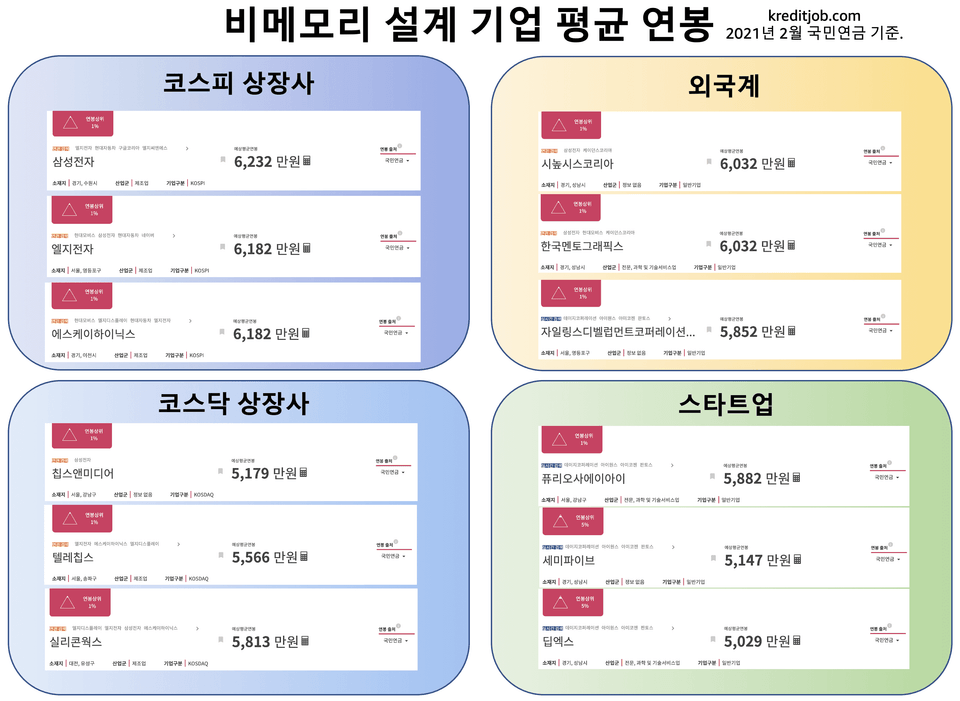

ご存知の通り韓国はメモリ半導体強国です。非メモリ半導体強国ではありません。

政府と企業が多くの投資を行っており、実際に国内には多くの設計会社があります。

就職サイトであるWanted、LinkedIn、サラムイン等で「Verilog HDL」キーワードを検索してみてください。

世界中の多くの会社が半導体設計エンジニアを探しています。

行きたい会社はありますか?その会社の年収を検索してみてください。

クレディットジョブで非メモリ設計関連会社を例に挙げると、国内企業平均年収上位1%です。

もらう分だけ勉強しなければならない職業で、簡単な道ではありません。

必読文書を読んでいただき、心より感謝いたします。

ここまで読まれた方は、私の講義を受講されなくても、

皆さんは素晴らしい設計エンジニアになられると確信しています。

選択は皆さん次第です。

皆さんと現場でお会いできることを楽しみにしています。

ありがとうございます。マッビより。

学習対象は

誰でしょう?

大学電子科2~4年生レベルの知識を備えた方。

Verilog HDL 言語を勉強したことがある方

設計実務を経験したい方

非メモリー設計分野で就職を希望される方

前提知識、

必要でしょうか?

C言語

Verilog HDL

4,313

受講生

373

受講レビュー

1,311

回答

5.0

講座評価

5

講座

現) Global Top5 Fabless企業でHW IP設計をしています。

世の中になかった、そして皆さんの実務に役立つ「本物の半導体設計実務講義」を作っています。

設計独学ロードマップと一緒に、皆さんの実力を高めていきましょう。

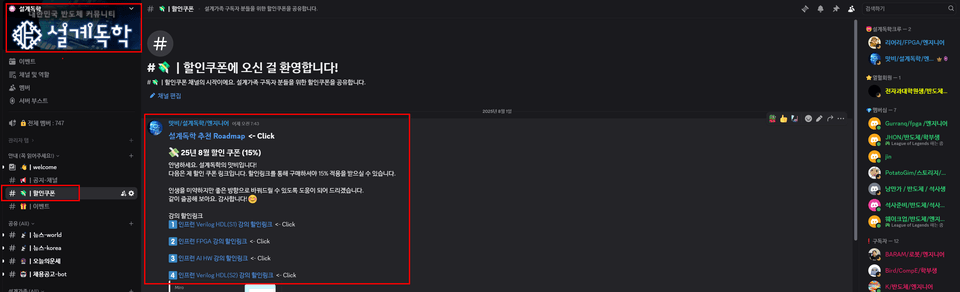

皆さんと交流するための設計独学コミュニティを運営しています。

(コミュニティに参加して、15%割引クーポンも受け取りましょう。)

一緒に楽しく勉強して成長しましょう!

全体

43件 ∙ (7時間 34分)

講座資料(こうぎしりょう):

全体

172件

5.0

172件の受講レビュー

受講レビュー 2

∙

平均評価 5.0

5

インストールするのに一日かかり、今受講申請して聞き始めましたが、こんなにいつでも聞くことができるverilog関連講義を上げてくれてありがとうございました。このような講義は2~30万ウォンが絶対惜しくないと思い、次の講義もぜひ聞く予定です。もしFPGAロードマップ講義を全部撮っていただいたら私も最後まで走るようにします。

受講評誠にありがとうございます! 現業と並行する予定のロードマップが出る過程が少し遅いですよㅠ それでも良いクオリティのために頑張っていますので、次の講義も楽しく聞いてください。 FPGAはすでに出てきた状態だと一緒に聞くと、能力に倍になると思われます。 楽しんでください!

受講レビュー 1

∙

平均評価 5.0

5

IDECやSW-SOCのような外部授業もあるが、IDECのような場合、教授の二人が多くの内容を暗示的に伝えようとし、理解しないことが多い。だからもう一度見ることはできないし。 SW-socのような場合はシーズン制ですか?講義の申請であるが(オンライン講義のような場合、以前にやったことを繰り返してくれるのに、なぜ受講申請のようなものを入れるのか分からない)恐れや就職連携講義か、恐れや簡単なことを率直に書くのがより役に立つ。イブン講義は現職者の立場で例コードに基づいて説明してくれてそれなり理解もされ、FPGA設計の際に役立つ本当の多くになったイチオシ!ありがとうございます

と.. 受講評 :) 足りない部分があったでしょうが(ないと言えません)よく見ていただいたのは幸いです。 今後も学校で教えてくれない内容を扱うようにします。 (学校の授業が重要ではないという意味ではありません) 楽しいです:)

受講レビュー 1

∙

平均評価 5.0

5

Verilog を使った H/W 設計の基本と勉強すべき方向を知りました。

ジョシュア様受講評ありがとうございます:) 基本中の基本を扱った講義だと思います。 まだ行くのが遠いですが(私を含む)学ぶことが多いということは、学んでおけば競争力ができるという肯定的なマインドで頑張ってみると良いことがあると信じています。 楽しいです!

知識共有者の他の講座を見てみましょう!

同じ分野の他の講座を見てみましょう!