Zynq 보드 다운로드 - 32~33 부분 실행이 안됩니다.

581

작성한 질문수 16

Zynq 보드 다운로드 - 32~33 부분을 진행 중 입니다.

그런데 아래와 같은 에러메시지가 나오면서 동작하질 않네요..

저는 현재 Zybo-z7-10 보드를 사용 중입니다.

답변 1

0

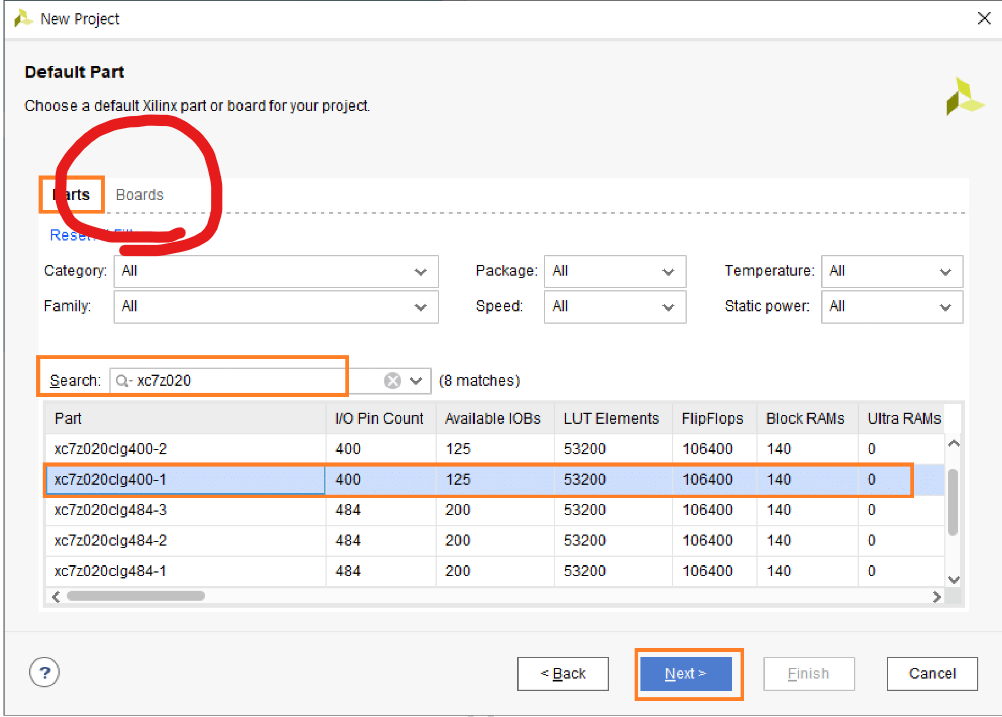

Zybo-z7-10 보드로 진행하시면, 프로젝트를 새로 생성해야 합니다.

프로젝트 생성시, 보드에 있는 fpga 파트넘버 (xc7z010-1clg400c)로 선택해서 프로젝트를 생성해야 합니다.

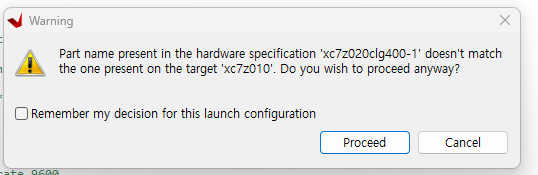

보드에 보면, fpga 파트넘버가 보입니다. 첨부하신 보드 사진에 xc7z010 으로 되어 있네요.

제공되는 소스 파일은 zynq mini 7020는 xc7z020 으로 되어 있습니다.

0

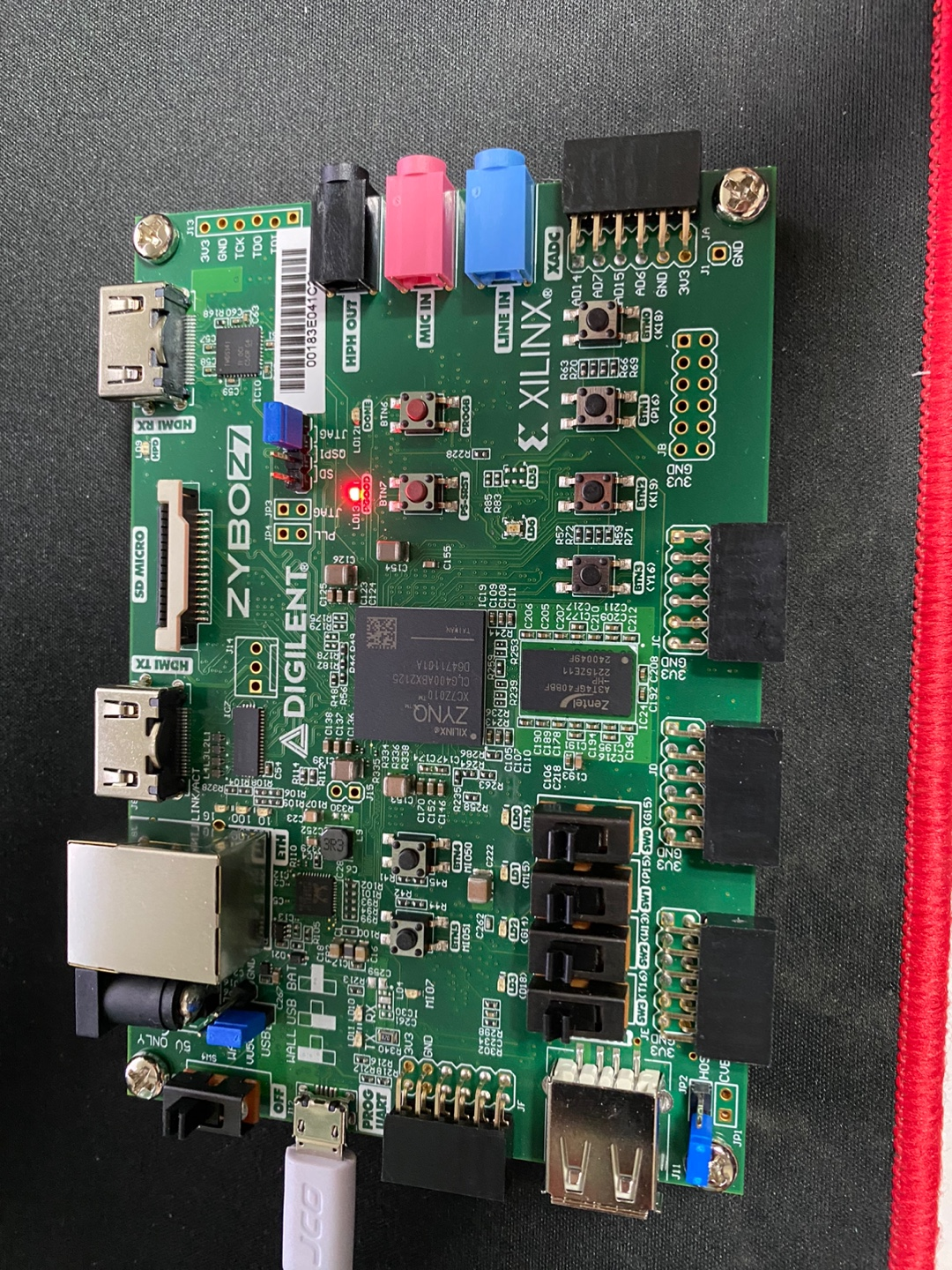

다시 시도해보았는데,

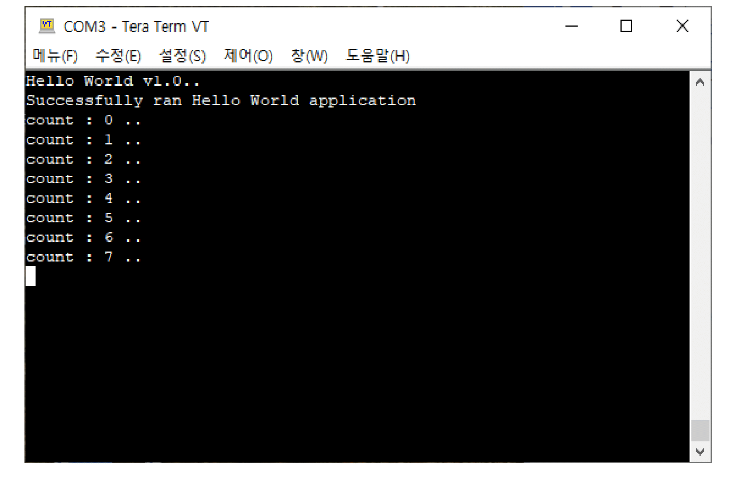

Zynq 보드 다운로드 - 32 부분의

Debug As 부분을 실행하면

위와 같은 메세지가 발생 하면서 동작이 되질 않습니다.

위와 같은 메세지가 발생 하면서 동작이 되질 않습니다.

그리고 강의노트에 나와있는

위와 같은 화면의 터미널을 열려면 어떻게 해야 하나요?

위와 같은 화면의 터미널을 열려면 어떻게 해야 하나요?

0

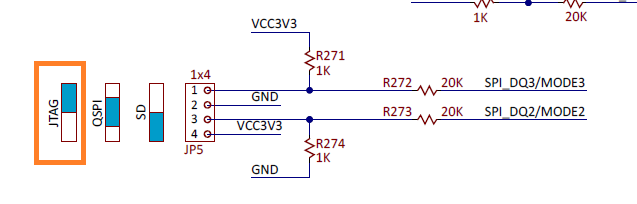

에러메시지 2번에 JTAG 모드 관련 메시지가 있네요.

아래 zybo 보드 회로도를 참조하시면, JTAG 모드로 설정하기 위해서는

JP5의 1,2번을 연결해야 합니다. (위의 사진을 보니, 1-2번 연결되어 있는 것 같긴 합니다)

제가 zybo 보드로 해보지 않아서 무엇이 문제인지 잘 모르겠네요.

Digilent 사에 JTAG 모드로 다운로드 하는 것에 대해서 문의해 보시는게 좋을 것 같습니다.

그리고 터미널 프로그램은 테라텀입니다.

자료실에 설치파일 올려두었으니 다운받아서 설치하시면 됩니다.

(tera-term-4.105-installer_Dzmf-H1.exe)

[HDL 32장-2부] 참고 링크 관련

1

35

2

강의 만료일 연장 신청

0

33

2

기초예제 파일 불러오기 문의

0

25

2

Zybo 환경에서 PL RTL UART 보드 검증 방법

0

30

2

혹시 별도의 자료가 있나요?

0

34

2

queue assignment pattern 문의 건

0

33

1

Mission 5 문의 건

0

46

2

Zynq z7 FPGA single-ended 관련

0

40

1

강의자료 PDF 어떻게받나요?

0

42

2

Differential Amp의 4가지 종류

0

41

1

[HDL 22장] F/F CE 관련 질문

1

46

2

UART0, 1 중 선택

1

51

2

fpga 개발보드

0

30

2

vivado 2022.1 version memory IP 구조

0

39

1

강의 ppt 자료 요청건

0

56

2

datamoverbram모듈질문

1

63

2

latency 개념 구현

1

84

3

미션tree

0

40

3

강의7 질문

0

47

2

mission1 질문

0

60

3

UART 구현 관련 질문

0

70

2

TOP 모듈 코딩 관련

0

139

1

Counter를 이용한 LED 제어 실습 부분 관련 문의 입니다

0

472

1

Counter를 이용한 LED 제어 실습 관련 문의

0

724

2