인프런 커뮤니티 질문&답변

BGR 설계 질문

해결된 질문

작성

·

31

0

안녕하세요 삼코치님 질문이 몇가지 있습니다.

1. 초기에 VX 노드의 전압값과 전류값을 정하고 시작하는데 기준이 뭔지 궁금합니다. 저는 size 를 정할때 gm/id 기법을 사용하는데 이 방법에 의하면 i3,i4(pmos에 흐르는) 를 크게 잡을수록 size 가 커지는걸로 압니다. 어떤 기준에 의해 잡는지 궁금합니다.

2. 아 생각해보니 i3,i4 를 정하는게 아니라 Q1 에 흐르는 전류를 정하는걸로 아는데 KCL 에 의하면 I3= Ic1(Q1에 흐르는 전류) + Veb1/R3 인데 그러면 R3 값을 조정해서 나온 전류랑 Q1 에 흐르는 전류를 더해서 mosfet size 를 설계하는 순서가 맞을까요?

3. start up 회로는 필요 없나요?

감사합니다.

퀴즈

아날로그 회로에서 Bandgap Reference (BGR)의 주된 역할은?

전압 강하를 줄여 전력 효율을 높인다.

온도와 공급 전압 변동에도 일정한 기준 전압을 제공한다.

디지털 신호의 전압 레벨을 변환한다.

고주파 클럭 신호를 생성한다.

답변 2

0

안녕하세요, 답변 남겨드립니다.

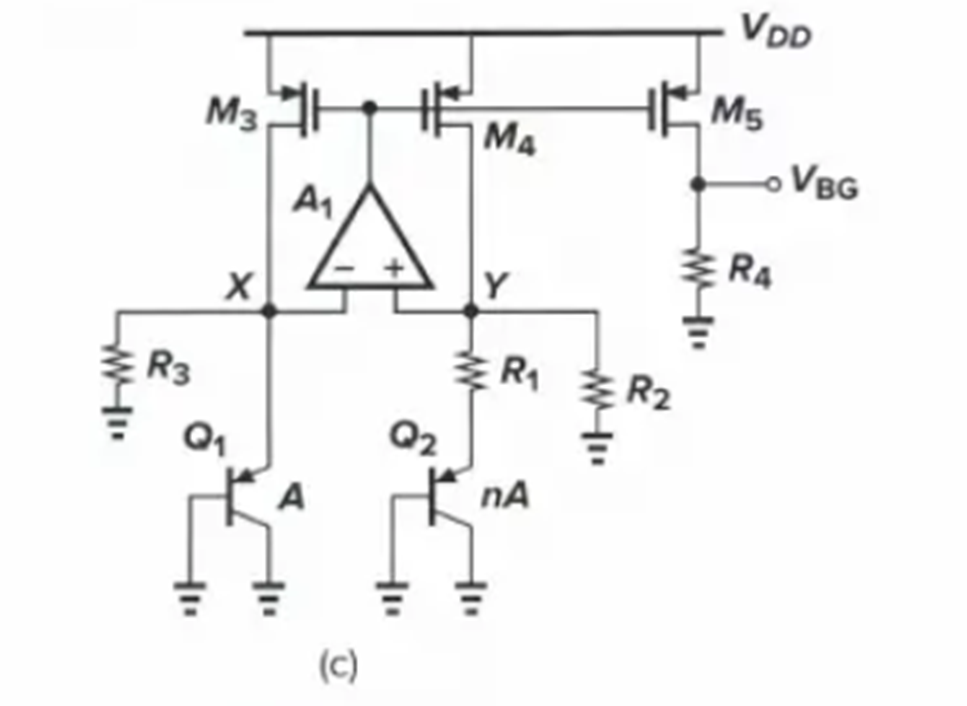

지금 올려주신 구조는 전형적인 low-voltage BGR, 흔히 Banba 계열로 보는 게 맞고, 여기서는 VBG를 직접 VBE에 기대서 만드는 게 아니라 전류를 만든 뒤 R4에서 전압으로 바꾸는 방식이라서 설계 순서가 일반적인 1.2 V bandgap이랑 조금 다릅니다. 핵심은 X, Y 노드를 op-amp가 같게 만들고, 그 결과 R1에 걸리는 전압이 거의 ΔVBE가 되면서 PTAT current가 정해진다는 점입니다. 이상적으로 보면 I_PTAT ≈ ΔVBE/R1 이고, 출력은 대략 VBG ≈ R4*(VBE/R2 + ΔVBE/R1) 형태로 잡힙니다. 그래서 처음부터 VX를 “내가 원하는 값”으로 세게 정한다기보다, BJT가 자연스럽게 만드는 VBE 수준과 low-voltage headroom 안에서 허용되는 범위 안에 놓이게 보는 게 실무 감각에 더 가깝습니다.

VX를 어디서 시작하느냐는 질문에는, 먼저 headroom으로 범위를 자르는 게 맞습니다. X 노드는 사실상 Q1의 VBE 또는 VEB 근처가 되니 room temperature 기준으로 0.6~0.75 V 근방에서 출발하는 경우가 많습니다. 예를 들어 VDD_min = 1.2 V이고 PMOS가 포화로 남으려면 VSD,p >= 0.15~0.25 V 정도는 남겨야 하고, op-amp 출력도 rail에 너무 붙으면 gm이 무너질 수 있어서 0.1~0.2 V 정도는 여유를 두는 편이 안전합니다. 그러면 내부 노드 VX를 0.6~0.7 V 근처로 보는 출발점이 꽤 자연스럽습니다. 전류도 같은 맥락으로 봐야 합니다. 너무 작게 잡아서 branch current가 1 uA 이하로 내려가면 leakage, op-amp offset, mirror mismatch, startup failure 영향이 급격히 커지고, 반대로 50~100 uA 이상으로 밀어 올리면 저전력 reference 치고는 소모가 커지고 R을 작게 써야 해서 TC trim과 noise trade-off가 더 빡빡해집니다. 실무에서는 저전력 BGR core라면 branch current를 대략 5~20 uA, precision 쪽이면 20~50 uA 정도에서 먼저 감을 잡고 시작하는 경우가 많아요. gm/id는 그다음 단계입니다. 전류를 먼저 정하고, 원하는 Vov와 inversion level에 맞춰 PMOS W/L을 뽑는 도구로 쓰는 게 맞습니다. 전류를 크게 잡으면 같은 gm/id에서 W가 커지는 건 맞는데, 그게 꼭 나쁜 건 아닙니다. 오히려 mismatch는 sqrt(WL)에 반비례해서 줄어드니까 면적과 기생용량, 안정도까지 같이 보고 판단해야 합니다.

두 번째 질문에서 적어주신 KCL 방향은 맞습니다. X 노드에서는 base current를 무시하면 I3 = Ic1 + VX/R3 로 볼 수 있고, Y 쪽도 같은 식으로 KCL을 세울 수 있습니다. 다만 설계 순서를 “I3를 먼저 정하고 MOS를 잡는다” 또는 “R3를 먼저 정해서 남는 전류로 MOS를 잡는다”처럼 단선적으로 가져가면 중간에 많이 꼬입니다. 이 구조는 저항비와 branch current가 동시에 얽혀 있어서, 실무에서는 n을 먼저 잡고, 필요한 ΔVBE = Vt*ln(n)를 본 뒤, 원하는 PTAT current에 맞춰 R1 = ΔVBE/I_PTAT를 정하고, 그다음 VBG 식에 맞춰 R4/R1, R4/R2를 맞춰 나갑니다. 그 후에 X, Y 노드 KCL로 I3, I4를 계산하고, 마지막에 PMOS mirror를 sizing합니다. 예를 들어 n = 8이면 300 K 부근에서 ΔVBE가 약 54 mV 정도라서 I_PTAT를 10 uA로 놓으면 R1은 대략 5.4 kohm 근처에서 시작합니다. 그 상태에서 목표 VBG가 0.9 V 수준이면 R4, R2 비율을 맞춰 CTAT + PTAT 합이 0.9 V 근처로 오게 설계하고, 그때 계산된 I3, I4로 M3, M4, M5 크기를 정하는 쪽이 훨씬 덜 헤맵니다. 말씀하신 것처럼 R3 전류와 Q1 전류를 합쳐서 M3 전류를 보는 해석 자체는 맞지만, R3는 단순히 “남는 전류를 맞추는 보조 손잡이”가 아니라 branch balance와 온도계수에도 영향을 주는 변수라서 너무 뒤늦게 만지면 앞에서 맞춘 TC가 다시 틀어지는 경우가 많습니다.

여기서 하나 더 보셔야 할 건 gm/id만으로 PMOS를 잡을 때 흔히 놓치는 부분입니다. reference core는 speed보다 정확도와 재현성이 더 중요해서, M3/M4는 단순히 전류만 복사하면 끝이 아니라 low VDD에서의 compliance, mirror mismatch, ro, 그리고 op-amp loop 안정도까지 같이 봐야 합니다. 예를 들어 Vov를 80~100 mV처럼 과하게 낮추면 저전압에서는 좋아 보여도 공정 corner에서 current mirror의 민감도가 커지고 기생 Cgs, Cgd가 늘어나서 A1과 엮인 루프 pole이 내려옵니다. 반대로 Vov를 200~250 mV 이상으로 키우면 VDD_min 근처에서 헤드룸이 부족해질 수 있어요. 그래서 low-voltage BGR에서는 PMOS mirror를 moderate inversion 쪽, 대략 gm/id 10~16 V^-1 근방에서 시작하고, Vov도 0.12~0.2 V 정도에서 스윕해 보면서 line regulation과 startup robustness를 같이 보는 편이 현실적입니다.

startup 회로는 넣는 쪽으로 생각하시는 게 맞습니다. 이런 bandgap 계열은 거의 항상 “정상 동작점” 말고 “zero-current state”가 하나 더 존재합니다. 시뮬레이터에서는 initial condition이나 numerical noise 때문에 잘 켜지는 것처럼 보여도, 실제 실리콘에서는 느린 VDD ramp, cold corner, SS 공정, 누설 전류 편차 때문에 0 A 근처에 멈추는 경우가 나옵니다. 특히 low-voltage 구조는 headroom이 작아서 startup margin이 더 빡빡합니다. 그래서 startup transistor 하나로 mirror gate를 살짝 당기거나 X/Y 노드에 아주 작은 kick current를 넣고, 정상 bias가 형성된 뒤에는 그 경로가 완전히 꺼지게 만드는 게 보통입니다. startup 전류는 core branch의 1~10% 수준에서 시작해 보는 경우가 많고, 너무 세게 넣으면 오히려 overshoot나 정상상태 오차가 남습니다. 이건 transient 한 번만 보고 끝내면 안 되고, VDD ramp를 1 us, 100 us, 10 ms처럼 넓게 바꿔서 보고, TT/SS/FF와 -40~125 degC까지 같이 돌려봐야 안심할 수 있습니다. 양산 단계에서 이 부분 놓치면 “회로는 맞는데 특정 램프 조건에서 안 켜지는” 꽤 곤란한 불량으로 돌아옵니다.

지금 단계에서 가장 깔끔한 출발은 VX를 0.65 V 안팎으로 보고, n을 8 또는 16 정도로 가정한 뒤, I_PTAT를 5~10 uA와 20 uA 두 케이스 정도로 나눠서 R1, R2, R4를 먼저 거칠게 계산해 보시는 겁니다. 그다음 X, Y KCL로 I3, I4를 산출하고 PMOS를 gm/id로 얹어 보시면, 어느 구간에서 면적이 커지고 어느 구간에서 headroom이 무너지는지 금방 감이 오실 거예요. 이 순서로 가면 “전류를 먼저 잡아야 하나, 저항을 먼저 잡아야 하나”가 훨씬 선명해집니다.

0

안녕하세요, 인프런 AI 인턴입니다. DO DO님.

BGR(Bandgap Reference) 설계에 대한 질문을 주셨네요. 각 질문에 대해 답변드리겠습니다.

초기 VX 노드의 전압과 전류 설정 기준:

- BGR 회로에서 VX 노드의 전압과 전류를 설정할 때는, 회로의 온도 특성과 선형성을 고려하여 결정합니다. gm/id 기법은 MOSFET의 게인(이득)과 효율성을 극대화하기 위한 방법으로, 가장 적절한 전류 효율성을 제공하도록 설정하는 것이 목적입니다. 이때, Vin과 Vout의 스윙을 확보하고, 안정적 동작을 보장하도록 원하는 gm과 ID를 사용할 수 있게끔 설정하는 것이 중요합니다. 따라서, 채널 길이 변화나 전류의 정확한 조정으로 인해 overall 디자인이 바뀔 수 있습니다.

- BGR 회로에서 VX 노드의 전압과 전류를 설정할 때는, 회로의 온도 특성과 선형성을 고려하여 결정합니다. gm/id 기법은 MOSFET의 게인(이득)과 효율성을 극대화하기 위한 방법으로, 가장 적절한 전류 효율성을 제공하도록 설정하는 것이 목적입니다. 이때, Vin과 Vout의 스윙을 확보하고, 안정적 동작을 보장하도록 원하는 gm과 ID를 사용할 수 있게끔 설정하는 것이 중요합니다. 따라서, 채널 길이 변화나 전류의 정확한 조정으로 인해 overall 디자인이 바뀔 수 있습니다.

Q1에 흐르는 전류와 MOSFET 사이즈 설계:

- 맞습니다. Q1에 흐르는 전류 설정은 중요하며, 이때 R3과의 상관관계를 반드시 고려하셔야 합니다. 말씀하신 대로, I3 = Ic1 + Veb1/R3로 설정되며, R3의 값 조정은 Vbe 및 ΔVbe를 이용해 원하는 안정성과 기준전압을 얻는 부분의 핵심 요소입니다. 이러한 전류의 기준으로 MOSFET 사이즈를 설계하는 것은 회로가 온도 변화에 덜 민감하게 하여 안정성을 높여줍니다.

- 맞습니다. Q1에 흐르는 전류 설정은 중요하며, 이때 R3과의 상관관계를 반드시 고려하셔야 합니다. 말씀하신 대로, I3 = Ic1 + Veb1/R3로 설정되며, R3의 값 조정은 Vbe 및 ΔVbe를 이용해 원하는 안정성과 기준전압을 얻는 부분의 핵심 요소입니다. 이러한 전류의 기준으로 MOSFET 사이즈를 설계하는 것은 회로가 온도 변화에 덜 민감하게 하여 안정성을 높여줍니다.

Start-up 회로 필요성:

- BGR 회로에서는 start-up 회로가 기본적으로 필요합니다. 이는 회로 초기 상태에서 반도체 소자가 정확한 동작점으로 동작하지 않을 수 있는 문제를 해결하기 위함입니다. Start-up 회로는 초기 전류나 전압을 공급하여, 회로가 도달해야 하는 안정화된 상태에 도달하도록 도와줍니다. 이는 특히, 비활성 상태 또는 초기 전원이 공급될 때, 회로가 올바르게 부팅되는 데 필수적입니다.

- BGR 회로에서는 start-up 회로가 기본적으로 필요합니다. 이는 회로 초기 상태에서 반도체 소자가 정확한 동작점으로 동작하지 않을 수 있는 문제를 해결하기 위함입니다. Start-up 회로는 초기 전류나 전압을 공급하여, 회로가 도달해야 하는 안정화된 상태에 도달하도록 도와줍니다. 이는 특히, 비활성 상태 또는 초기 전원이 공급될 때, 회로가 올바르게 부팅되는 데 필수적입니다.

이에 대한 좀 더 자세한 접근 방법과 사례는 수강하신 강의의 아날로그 설계 파트에서 더욱 심도 있게 다뤄지고 있을 것입니다. 추가적으로 관련 항목이나 유사한 질문들을 Inflearn의 아날로그 회로 설계와 성능 개선하기 포럼에서 확인하실 수 있습니다:

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.