Active load differential amp 질문

안녕하세요 삼코치님.

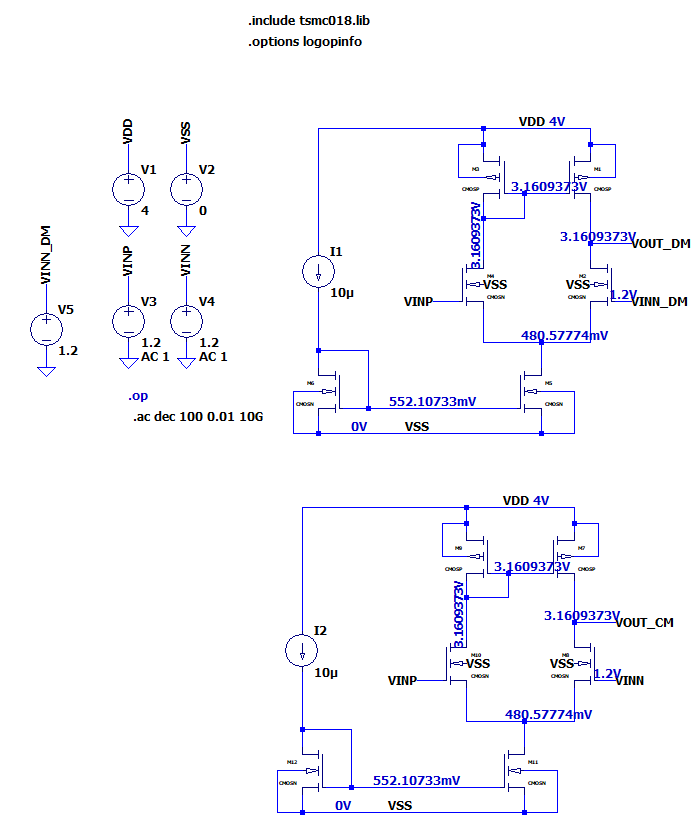

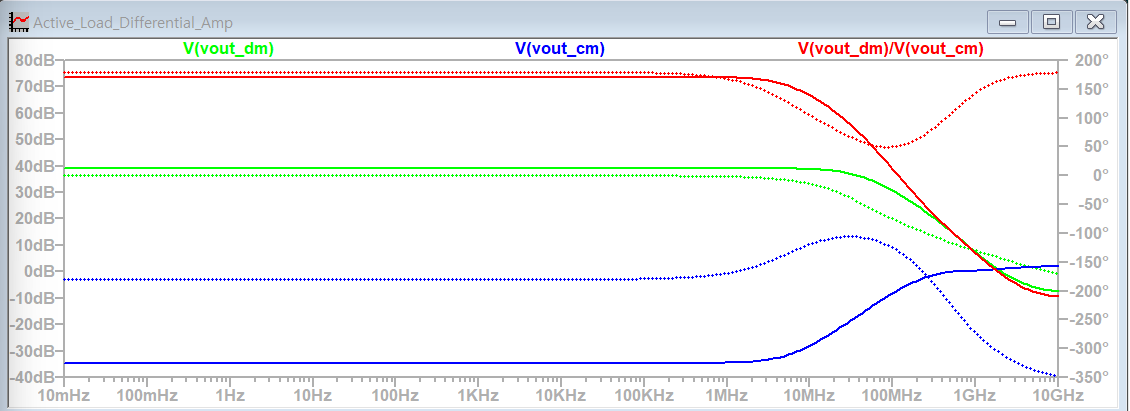

다름이 아니라 CMRR을 시뮬레이션 하는 과정에서 다음과 같이 동영상과는 Phase가 사뭇 다르게 나와서 질문드립니다.

DC operation은 모두 saturation에 있는 것 같습니다.

bias current잡는 밑의 두 트랜지스터만 L1u W4u로 하고 나머지는 L과 W모두 1u로 했습니다.

그리고 Vcm과 Vdm을 각각 따로 보면 저렇게 보이고 이걸 나누면 저렇게 되는데,

magnitude는 동일한데 phase가 다르게 나옵니다.

GPT한테 물어보면 phase는 별로 중요하지 않다고 나오는데 CMRR에서 phase는 별로 중요하지 않은 값이고 저렇게 나온 것도 정상적인 건지 여쭤보고 싶습니다.

또 CMRR을 구할 때 ADM/ACM으로 구하는데 gain이 아닌 voltage값으로 구해도 동일한 건지 여쭙고 싶습니다.

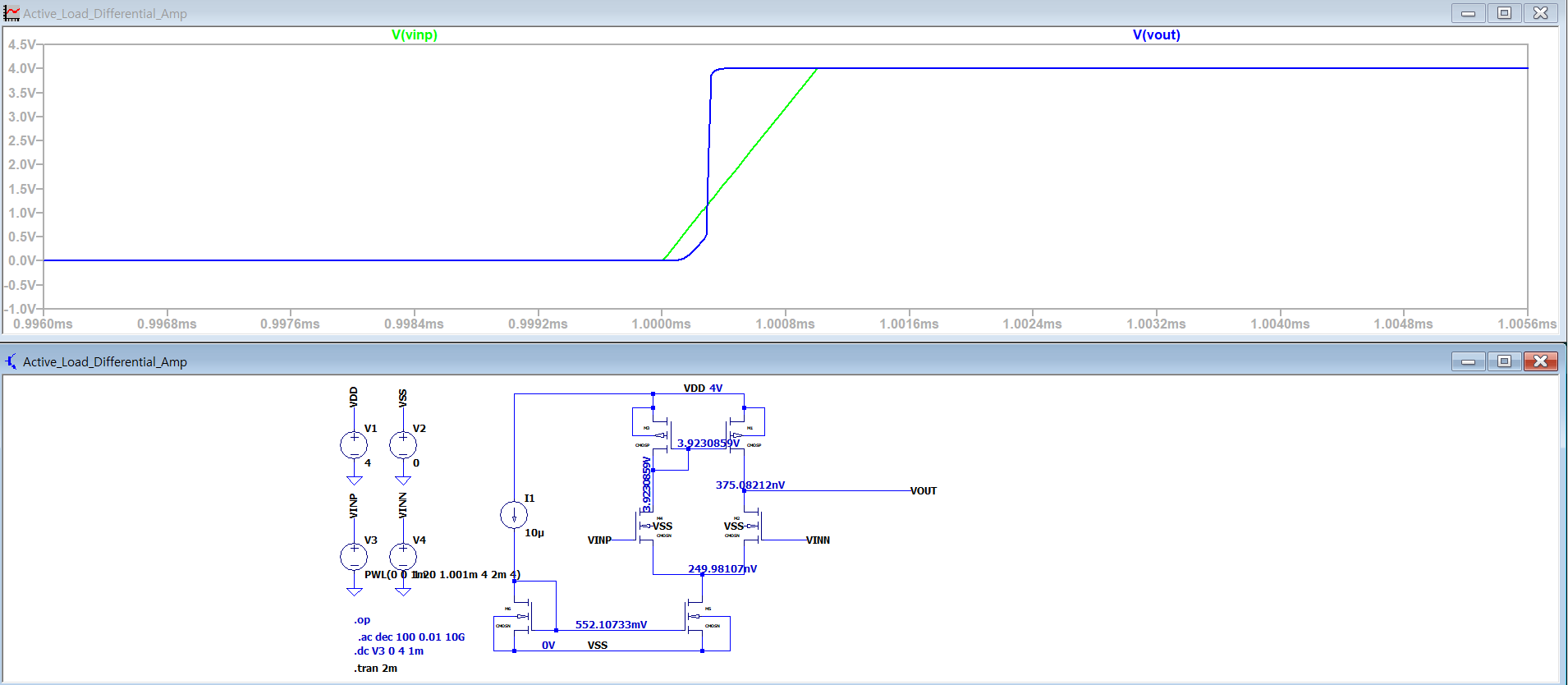

(생각해봤을 땐 Vinp랑 Vinn을 예를 들어 AC 1/-1이 아닌 1/0으로 해서 Vout을 Gain으로 하려고 한 게 아닌가 싶습니다)Slew Rate도 다음과 같이 굉장히 가파르게 나오는데 이렇게 나와도 되는 건가요? ㅜㅜ 안좋은건지 여쭙고 싶습니다.

4. 또한 추가적으로 ICMR은 시뮬레이션을 안하는지도 궁금합니다.

강의를 이렇게 올려주셔서 잘 듣고 있습니다. 항상 감사드립니다.

답변 1

0

안녕하세요, 답변 남겨드립니다.

첫 번째 질문인 CMRR에서 phase가 영상과 다르게 나오는 게 정상인지에 대해서는, 지금처럼 LTspice에서 V(vout_dm)/V(vout_cm)로 CMRR을 구성하시면 위상이 다르게 보이는 경우가 충분히 정상 범주입니다. CMRR은 원래 주파수에 따른 복소비로 정의되어 CMRR(jw) = Ad(jw) / Ac(jw) 이고, Ad와 Ac가 각각 폴/제로를 갖는 전달함수이기 때문에 CMRR도 크기와 위상을 동시에 가집니다. 다만 현업에서 “CMRR 스펙”이라고 말할 때는 거의 항상 |CMRR|만 dB로 관리하고 위상은 스펙 항목으로 두지 않는 경우가 대부분이라, 학습 단계에서는 phase가 영상과 다르다고 해서 곧바로 비정상이라고 보지 않습니다. 특히 active-load differential pair는 공통모드 경로(Ac)가 차동 경로(Ad)와 다르게 테일 전류원 ro, 미러의 ro와 기생 C, 입력쌍 소스 노드 임피던스 변화를 강하게 타면서 추가 폴/제로가 생기기 쉬워서, 같은 magnitude 감소 타이밍이라도 phase가 더 빨리(또는 더 늦게) 돌아가는 현상이 흔합니다. 또 한 가지 실무적으로 자주 보이는 현상은, 분모인 V(vout_cm)가 어떤 대역에서 매우 작아지거나 위상이 급격히 변하면(거의 0에 가까워지거나 notch처럼 보이는 구간) 비의 위상이 90도~180도 이상 크게 휘어 보일 수 있다는 점인데, 이건 “비를 취하는 수학적 결과”로도 충분히 발생합니다. 결론적으로 CMRR의 phase는 “볼 수는 있지만” 보통 합격/불합격을 가르는 1차 기준은 아니고, |CMRR|이 저주파에서 충분히 높고 주파수에 따라 어떻게 떨어지는지가 핵심입니다. 예를 들어 저주파에서 |CMRR|이 60 dB 이상이고, 1 MHz에서 40~50 dB 이상 유지되는지 같은 식으로 정량 목표를 잡는 방식이 일반적입니다(목표 수치는 제품군마다 다릅니다).

두 번째 질문인 “ADM/ACM을 gain이 아니라 voltage로 구해도 되나”는, 지금처럼 V(vout_dm)/V(vout_cm)로 보는 방식 자체는 괜찮지만, 딱 한 가지 조건이 충족될 때만 “전압비가 곧 CMRR”이 됩니다. 그 조건은 dm 실험에서의 입력 차동 진폭 Vdm과 cm 실험에서의 입력 공통모드 진폭 Vcm을 동일하게 정규화하는 것입니다. 일반식으로 보면 V(vout_dm)/V(vout_cm) = (AdVdm)/(AcVcm) 이라서, Vdm=Vcm=1일 때만 Ad/Ac가 됩니다. 여기서 가장 흔한 함정이 dm을 VINP=AC 1, VINN=AC -1로 두는 경우인데, 이때 Vdm의 AC 진폭은 2가 됩니다. 반면 cm을 VINP=AC 1, VINN=AC 1로 두면 Vcm은 1이어서, 결과적으로 전압비로 만든 CMRR이 실제보다 2배 커지고 dB로는 20*log10(2)=6.02 dB 과대평가됩니다. 그래서 현업에서는 dm을 VINP=+0.5, VINN=-0.5로 줘서 Vdm=1로 맞추고, cm을 VINP=1, VINN=1로 줘서 Vcm=1로 맞춘 뒤, 그때의 V(vout_dm)/V(vout_cm)를 CMRR로 해석하는 방식을 많이 씁니다. 질문에 적어주신 “AC 1/-1이 아닌 1/0으로 해서 Vout을 gain으로 보려던 것 같다”는 접근은 단일 입력 자극이어서 차동/공통모드가 섞이기 쉽고, CMRR 측정 정의를 깔끔하게 만들기 어렵기 때문에 권장되지는 않습니다. 정리하면, 전압으로 구하셔도 되지만 Vdm과 Vcm을 1로 맞춰서 “전압이 곧 전달함수”가 되게 만들어 주셔야 수치가 정확해집니다.

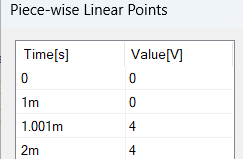

세 번째 질문인 slew rate가 지나치게 가파르게 나오는 게 정상인지에 대해서는, 출력 부하 조건이 거의 없으면 그렇게 보이는 것이 오히려 정상에 가깝습니다. slew rate는 1차적으로 SR = Imax / Cload로 정해지는데, 출력에 명시적으로 Cload를 달지 않으면 기생 커패시턴스(수 fF~수십 fF 수준)만 남아서 SR이 비현실적으로 커지기 쉽습니다. 예를 들어 출력으로 밀어줄 수 있는 전류가 10 uA 수준이고 Cload가 10 fF라면 SR = 10e-6/10e-15 = 1e9 V/s = 1000 V/us가 되어 파형이 거의 수직처럼 보일 수 있습니다. 반대로 Cload를 1 pF만 걸어도 SR = 10e-6/1e-12 = 1e7 V/s = 10 V/us로 현실적인 숫자가 됩니다. 그래서 실무에서는 slew rate를 평가할 때 Cload를 목표 환경으로 고정해서 봅니다. 예를 들어 “센서 프론트엔드 내부 노드”면 1 pF 전후, “패드/버퍼 근처”면 수 pF~수십 pF까지도 가정하는 식으로 시나리오를 정하고, 그 조건에서 dv/dt를 10%~90% 구간의 기울기로 재서 SR을 정량화합니다. 그리고 입력 스텝도 너무 크게 주면 출력이 레일 근처로 포화되면서 “slew”가 아니라 “포화 후 회복(settling with saturation)”을 보게 되니, 소신호 settling(예: 입력 10 mV~50 mV)과 대신호 slew(예: 입력 수백 mV)를 분리해서 보는 것이 안전합니다. “가파르면 안 좋은가”는 그 자체로 나쁘다기보다, 그 가파름이 어떤 Cload에서도 유지되는지, 그리고 그 과정에서 오버슈트/링잉이 커지지 않는지(안정도)가 더 중요합니다. 예를 들어 Cload=5 pF에서 SR이 2 V/us 이상 나오면서도 링잉이 ±5% 이내로 정착하면 좋은 설계라고 보는 식의 판단을 합니다.

네 번째 질문인 ICMR을 시뮬레이션 안 하는지에 대해서는, 단일 active-load differential amp라도 ICMR은 보는 것이 맞고, 실무에서도 기본 체크 항목입니다. 방법은 차동 입력을 0으로 두고(VINP=VINN=VCM), VCM을 DC로 스윕하면서 모든 소자가 포화(saturation)를 유지하는 구간과 그 구간에서의 이득/동작점을 같이 확인하는 것입니다. 개략적으로 NMOS 입력쌍 구조에서 하한은 VCM_min ≈ VSS + VGS(in) + VDSsat(tail)로 잡히는 경우가 많고, 상한은 PMOS 로드의 헤드룸과 출력 노드 전압 범위에 의해 제한됩니다. 현업에서 빠르게 감을 잡을 때는 오버드라이브를 Vov≈0.2 V 정도로 두고, 입력쌍과 테일에 각각 약 0.2 V 헤드룸이 필요하다고 보면 하한은 VSS+0.4 V 근처부터 열리는 그림이 자주 나오며, 상한은 로드의 VSDsat와 출력 스윙 한계가 맞물려 결정됩니다. 이건 공정/모델/바이어스에 따라 크게 달라지므로, 실제로는 VCM을 예를 들어 0.2 V에서 2.0 V까지 1 mV 스텝으로 올려가며 각 트랜지스터의 Vds가 Vdsat보다 큰지(즉 Vds > Vov 조건)와 출력 DC 레벨이 어디까지 따라오는지를 동시에 보는 방식이 가장 확실합니다. 이렇게 하면 “어느 소자가 먼저 선형영역으로 떨어져 ICMR 한계를 만드는지”가 수치로 바로 드러나고, 그에 맞춰 W/L이나 바이어스 전류를 어떻게 조정해야 하는지도 설계 의사결정이 쉬워집니다.

요약해서 말씀드리면, LTspice에서 V(vout_dm)/V(vout_cm)로 CMRR을 보는 방식은 실무적으로도 많이 쓰는 편이고, phase가 영상과 달라지는 것 자체는 충분히 정상일 수 있습니다. 다만 전압비가 정확한 CMRR이 되려면 dm과 cm 입력 AC 진폭을 반드시 동일하게 정규화해서 6.02 dB 같은 스케일 오차가 안 생기게 만드는 것이 핵심이고, slew rate는 Cload를 명시하지 않으면 과장되어 보이기 쉬우며, ICMR은 반드시 VCM sweep으로 포화 조건과 동작 범위를 확인하시는 게 맞습니다.

[HDL 32장-2부] 참고 링크 관련

1

35

2

[LTspice 질문] PSRR 측정 방법 질문드립니다.

0

33

2

강의 만료일 연장 신청

0

31

2

기초예제 파일 불러오기 문의

0

25

2

Zybo 환경에서 PL RTL UART 보드 검증 방법

0

30

2

혹시 별도의 자료가 있나요?

0

32

2

queue assignment pattern 문의 건

0

32

1

Differential Amp의 4가지 종류

0

41

1

single-stage amp 시뮬레이션 해보기 회차에 mosfet 정보가 안뜹니다

0

91

2

SPICE Output Log에 대한 질문

0

74

2

active load differential amp 설계

0

73

2

16_bitRCA 테스트벤치 관련질문드립니다.

0

75

2

4-Input NAND Gate 모듈 코드에 대해 질문 드립니다.

0

124

2

verilog 문법 관련 질문 드립니다.

0

58

1

Active load Diffrential amp 설계와 관련하여 질문이 있습니다.

0

97

5

module FA_CLA_1b assign 구문 질문

0

73

2

single stage amp 시뮬레이션 질문드립니다

0

83

2

Slew rate 질문드립니다

0

262

2

view에 mosfet 정보가 안뜨고 있습니다.

0

128

2

Trade Off 강의에서 궁금한 점이 있습니다.

0

175

2

부품 심볼이 없습니다.

0

107

1

여기서 강사님이 보여주신 내용대로 안나옵니다/

0

167

2

강의 질문드립니다.

0

178

2

메모리 제품 검증에서 FPGA 활용

0

234

2