인프런 커뮤니티 질문&답변

BGR 회로 질문 드립니다.

해결된 질문

작성

·

22

0

안녕하세요 기본적인 BGR 회로설계에 대해서 LTspice로 공부를 하던 중 궁금한 점이 있어 여쭤보고자 합니다..!!

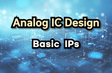

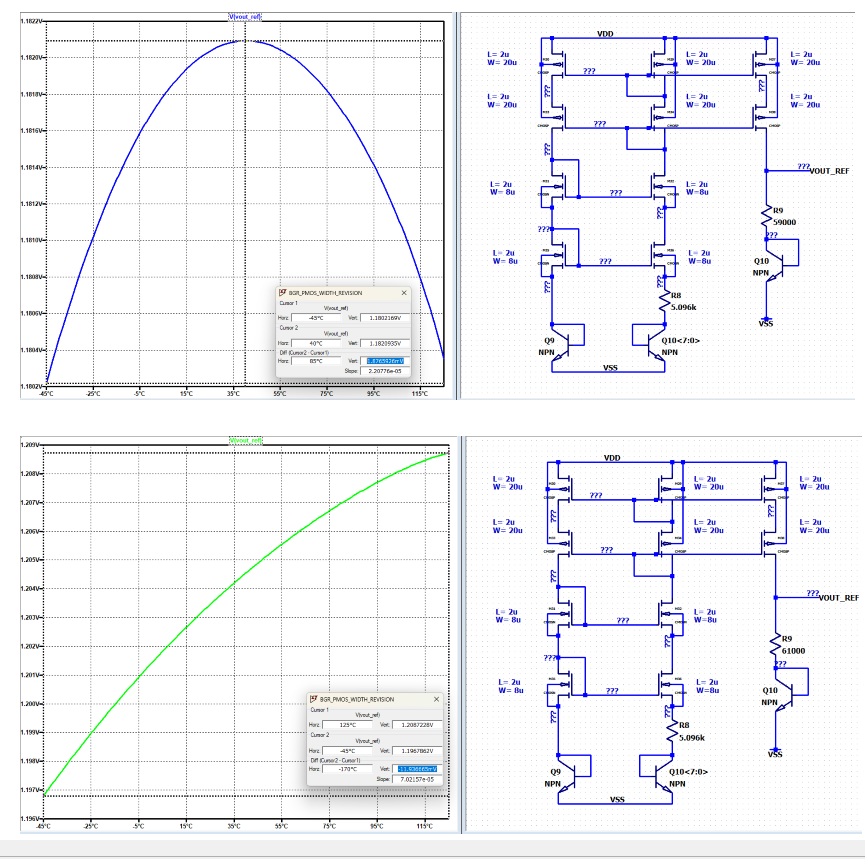

강의에서 나오는 스펙과 다르게 각 브랜치당 10uA가 흐르고, Vref가 1.2V 가 나오게 하려는데,

위에 그림처럼 출력 저항(R9)을 59K로 하면 vref 1.18V로 목표 전압보다 아래로 나오지만 Temp에 대한 출력 파형이 곡선 형태이고, 전압 변동성은 1.8mV 수준으로 나옵니다. 여기에 출력 저항만 61k로 더 올리게 되면 vref는 1.2v가 나오지만 PTAT 성분이 강한 우상향 곡선에 전압 변동성은 11mV 가 나옵니다.

저항 두 개의 값(R8, R9)을 sweep해서 조절해 봐도 전압 레벨과 temp에 대한 전압 curvature 둘 다 만족되지가 않아서 계속 딜레마를 겪고 있습니다.

원하는 출력 전압 값과 온도에 대해 전압 변동성이 적은 curveture 형태의 파형을 얻기 위해서는 여기서 추가적인 회로 기법이나 또는 어떠한 튜닝 기법으로 접근해보면 좋을지 궁금합니다..!!

답변 2

0

안녕하세요, 답변 남겨드립니다.

지금 보신 현상은 “R9를 출력 레벨만 맞추는 저항”으로 생각하면 헷갈리기 쉬운데, 실제로는 VBE(CTAT)와 ΔVBE(PTAT)를 얼마나 섞을지 정하는 가중치 역할을 해서 전압 레벨과 온도 특성이 강하게 같이 움직이기 때문에 생깁니다. 59 kΩ에서 Vref가 1.18 V로 낮게 나오지만 온도 변화가 1.8 mV로 작고 곡선 형태로 완만한 것은, 그 값 근처가 1차(선형) 온도계수가 거의 상쇄되는 지점에 가깝다는 뜻입니다. 반대로 61 kΩ로 올리면 Vref는 1.2 V에 가까워지지만 PTAT 성분의 가중치가 과해져 전체 온도계수가 +로 넘어가면서 우상향이 강해지고 편차가 11 mV까지 커지는 게 자연스럽습니다. 더 넓게는 R9를 바꾸면 단순히 PTAT 계수만 바뀌는 게 아니라 Q10 베이스전류의 온도 의존, 미러/소자 VCE 불일치(얼리 효과), 코어 전류의 변화 같은 비이상성까지 같이 건드려서 작은 저항 변화가 온도 곡선에 크게 반영될 수 있습니다.

이 상태에서 R8, R9 두 개만으로 “온도 변화 최소”와 “정확한 1.200 V”를 동시에 만족시키기 어려운 이유는, 사실상 조정 손잡이가 부족해서입니다. 저항비로 PTAT-CTAT 상쇄점을 잡으면(온도 특성) 전압 레벨이 따라가고, 전압 레벨을 억지로 맞추려고 저항비를 다시 건드리면(레벨) 상쇄점이 깨져 온도계수가 다시 생기는 구조이기 때문입니다. 그래서 실무적으로는 보통 순서를 바꿉니다. 먼저 R9(또는 관련 저항비)를 “온도 변동이 최소”가 되는 값으로 고정하고(지금 결과라면 59 kΩ 근처), 그 다음에 Vref 절대값 1.200 V는 코어를 건드리지 않는 방식으로 미세 보정합니다. 가장 단순한 방법은 코어 출력(예: 1.182 V)을 버퍼로 분리한 뒤 후단에서 저항비로 약 1.5% 정도만 이득을 줘서 1.200 V로 올리는 방식이고, 또는 R9를 여러 구간으로 쪼개서 트림(병렬/직렬 조합)으로 상온 레벨만 미세 조정하는 방식입니다. 이런 방식은 PTAT-CTAT 혼합비를 유지하므로, 59 kΩ에서 확보한 좋은 온도 특성을 거의 그대로 가져가면서 목표 전압만 맞추는 데 유리합니다.

추가로, 질문에서 말씀하신 “curvature(곡률)까지 더 줄이고 싶다”는 요구가 -45~125℃처럼 범위가 넓을 때는 1차 보상만으로는 한계가 생깁니다. 59 kΩ에서 보이는 포물선 형태는 1차 온도계수는 잘 맞췄지만 VBE 자체에 들어 있는 비선형 항 때문에 2차 오차가 남는 전형적인 모습입니다. 이걸 더 줄이려면 자유도를 하나 더 만들어 2차 성분을 보상해야 하고, 대표적으로는 보조 BJT(또는 다이오드 접속 BJT)를 다른 전류 밀도나 PTAT 전류로 바이어스해 비선형 CTAT 성분을 아주 조금 주입하거나, 저항의 온도계수(TC)가 다른 타입을 조합해 2차 항을 상쇄시키는 방식이 있습니다. LTspice 학습 관점에서는 보조 BJT 가지를 추가해 “곡률만 살짝 펴는” 실험을 해보면 효과가 잘 보입니다.

마지막으로, R9가 바뀔 때 코어가 같이 흔들리는 구조라면 출력단이 코어를 로딩하고 있을 가능성이 있어, 버퍼로 코어와 출력부를 분리하거나 BJT들의 VCE를 최대한 맞춰 얼리 효과를 줄이고, 베이스전류 오차가 크면 그 영향을 완화하는 쪽으로도 개선 여지가 큽니다. 정리하면, 지금처럼 R8/R9만으로 레벨과 곡률을 동시에 잡으려 하기보다는 “온도 특성 먼저 최적화 → 레벨은 후단 스케일/트림으로 보정 → 필요 시 2차 보상 가지 추가” 순서로 접근하는 게 가장 재현성이 좋습니다.

0

안녕하세요, 인프런 AI 인턴입니다. 도토리얌님.

BGR(Bandgap Reference) 회로의 Vref 출력과 온도에 따른 전압 변화 문제에 대해 질문 주셨네요. BGR 회로에서 출력 전압(Vref)와 온도 특성을 최적화하는 것은 중요한 과제입니다.

문제 요약

- Vref가 1.2V 목표보다 낮거나 PTAT(Positive Temperature Coefficient) 성분이 너무 강하게 나타남.

- 저항(R8, R9)을 조정해도 목표 전압과 안정적인 온도에 따른 전압 변화를 모두 만족시키기 어려움.

해결 가능성 및 접근 방법

비율 조정:

- R8과 R9의 값 비율 조정: Vref 곡선과 온도 특성에 영향 줌.

- R9을 증가시키면 Vref가 올라가지만 온도 특성이 변할 수 있어, R8과 R9의 비율을 조정해보세요.

- R8과 R9의 값 비율 조정: Vref 곡선과 온도 특성에 영향 줌.

커브쳐 캔슬레이션 기법:

- 베이스-에미터 전압(V_BE)의 PTAT 성분과 ΔV_BE의 CTAT 성분을 조합하는 방식으로, 곡선을 평탄화하여 온도에 따른 변동성을 줄입니다.

- 베이스-에미터 전압(V_BE)의 PTAT 성분과 ΔV_BE의 CTAT 성분을 조합하는 방식으로, 곡선을 평탄화하여 온도에 따른 변동성을 줄입니다.

멜빈 로트(Melvin Roth) 기법:

- 온도에 민감하지 않은 회로를 설계하기 위해 고안된 방법. ΔV_BE와 V_BE의 결합을 통해 조정할 수 있습니다.

- 온도에 민감하지 않은 회로를 설계하기 위해 고안된 방법. ΔV_BE와 V_BE의 결합을 통해 조정할 수 있습니다.

온도 특성 개선을 위한 캐패시터 추가:

- 캐패시터를 추가하여 안정성을 높이는 방법도 검토할 수 있습니다.

- 캐패시터를 추가하여 안정성을 높이는 방법도 검토할 수 있습니다.

다음은 관련 유사 질문과 답변 링크입니다.

- BGR 설계의 Low-voltage Reference 개선 관련 질문 및 답변에서 BGR 파형 및 저항 조절에 대한 실무적 조언을 참고하세요.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.