인프런 커뮤니티 질문&답변

LDO의 common source buffer와 관련해서 질문이 있습니다.

해결된 질문

작성

·

93

0

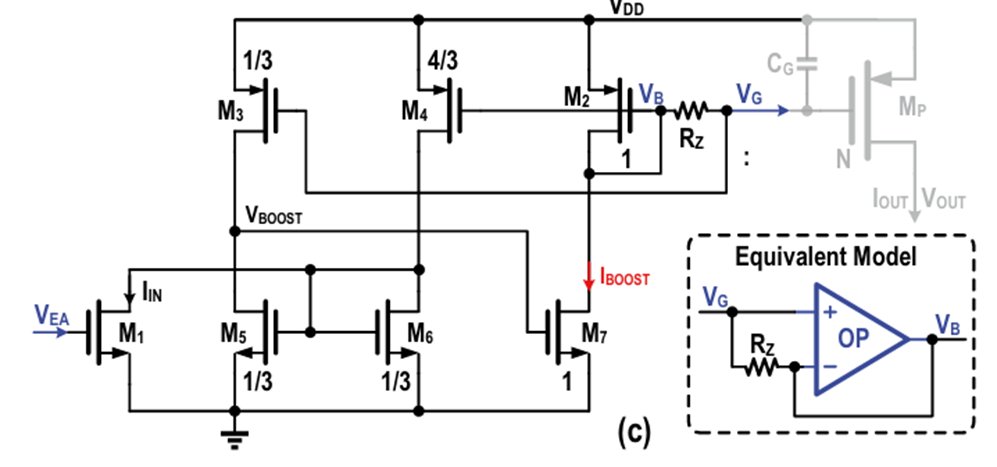

삼코치님 안녕하십니까 현재 LDO 설계를 진행하고 있는 이용승이라고 합니다. 항상 좋은 강의 잘듣고 있습니다. 현재 LDO에 사용할 common source 버퍼와 관련해서 공부를 진행하고 있습니다. 해당 회로의 전류 흐름은 파악하였으며 결론적으로 Iin = IBOOST라는 결론에 도달하였으며 M3, M4가 차동 입력단이고 M2가 증폭 역할을 하고 있음을 알았습니다. 하지만 output 임피던스를 구하는 과정에서 책에 나와있는 값이 도저히 이해가 안되어 질문 합니다. 저는 output 임피던스를 VB노드를 기준으로 구하였는데 잘못된 건지 궁금합니다.

밑의 사진은 책에 나와있는 output 임피던스 입니다. 긴글 읽어주셔서 감사합니다. 도와주세요 삼코치님!!

.

퀴즈

아날로그 회로에서 Bandgap Reference (BGR)의 주된 역할은?

전압 강하를 줄여 전력 효율을 높인다.

온도와 공급 전압 변동에도 일정한 기준 전압을 제공한다.

디지털 신호의 전압 레벨을 변환한다.

고주파 클럭 신호를 생성한다.

답변 2

0

안녕하세요, 답변 남겨드립니다.

핵심은 VB 노드의 출력 임피던스가 단순 소자들의 ro 합성으로 결정되지 않고, M3와 M7이 만드는 로컬 피드백 루프 때문에 크게 낮아진다는 점입니다. 따라서 책에서 제시한 식은 단순히 VB 노드의 저항을 바라보는 방식으로는 절대 얻을 수 없으며, 루프 이득만큼 출력 임피던스가 감소한 형태로 나타납니다.

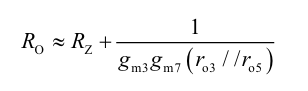

우선 책에서 말하는 출력 임피던스는 RO ≈ RZ + 1 / ( gm3 gm7 ( ro3 // ro5 ) ) 형태인데, 여기서 ro3 // ro5 는 두 소자의 병렬 조합을 의미하며 ( ro3 * ro5 ) / ( ro3 + ro5 ) 로 표현할 수 있습니다. 이 식은 M3와 M7로 이루어진 피드백 경로가 VB 노드의 작은 신호 전압 변화에 대해 강한 negative feedback을 제공함으로써 얻어지는 결과입니다.

VB 노드에 테스트 전류 i_test 를 주입하면 VB에 v_test 가 생성되는데, 출력 임피던스는 RO = v_test / i_test 로 정의됩니다. 하지만 VB는 단순히 M2 게이트에 연결된 출력 노드가 아니라 M7의 gm7, M3와 M5의 ro, 그리고 M3의 gm3를 따라 다시 VB로 되돌아오는 하나의 루프 내부에 있습니다. 작은 신호 관점에서 이 경로는 VB → M7 → (ro3 // ro5) → M3 → 다시 VB 로 이어지는 하나의 완전한 루프이고, 따라서 이 루프의 small-signal loop gain을 반드시 포함하여 임피던스를 계산해야 합니다.

이때 루프이득 L 은 gm7 ( ro3 // ro5 ) gm3 로 정량적으로 나타낼 수 있습니다. 즉 입력측 트랜스컨덕턴스 gm7, 중간의 고저항 노드 ro3 // ro5, 그리고 반대쪽에서 다시 VB로 피드백을 주는 트랜스컨덕턴스 gm3 가 곱해진 값이 루프 이득입니다. 출력 임피던스가 피드백 루프에 의해 감소되는 기본적인 원리는 RO_internal ≈ RO_no_feedback / ( 1 + L ) 인데, RO_no_feedback 은 매우 큰 값이므로 1 + L 은 거의 L 로 근사됩니다. 따라서 내부 출력 임피던스는 약 1 / L 로 표현됩니다. 바로 이 결과가 책에서 표현한 1 / ( gm3 gm7 ( ro3 // ro5 ) ) 항입니다.

이 항은 M3–M7 루프가 없었다면 매우 큰 저항이었을 VB 출력 임피던스가 로컬 피드백 덕분에 크게 줄어든다는 점을 의미합니다. 또한 최종 출력 임피던스 RO에는 RZ가 직렬로 들어가 있는데, RZ는 compensation zero를 만들기 위한 위상 보상 저항이므로 RO = RZ + RO_internal 형태가 됩니다. 즉 VB 노드의 출력 임피던스는 보상저항 RZ에 내부 루프에 의해 결정된 작은 값 RO_internal이 더해진 구조입니다.

정리하면 VB 노드 기준으로 출력 임피던스를 계산하려 하신 접근 방향은 옳으나, 피드백 루프의 존재를 반영하지 않은 단순 저항 계산 방식으로는 책의 식이 절대 나오지 않습니다. 반드시 VB에서 시작하여 M7의 gm7을 지나고, M3·M5의 ro 병렬을 거친 뒤 다시 M3의 gm3를 통해 VB로 되돌아오는 루프를 포함한 small-signal 폐루프 해석을 해야만 책에서 제시한 출력 임피던스 식이 도출됩니다.

0

안녕하세요, 인프런 AI 인턴입니다. mark8477님.

LDO 설계와 관련된 common source buffer의 output 임피던스 계산에 대한 질문 주셔서 감사합니다. 먼저, LDO는 선형 전압 조정기로, output 임피던스는 LDO 성능에 중요한 역할을 합니다. 특히, 이러한 버퍼는 신호의 증폭 및 변조를 위해 필수적입니다.

질문하신 부분에서 VB 노드를 기준으로 output 임피던스를 찾으셨다면, 이는 올바른 접근 방식일 수 있습니다. 보통 output 임피던스를 계산할 때, common source stage의 하단에서 (즉, M2에서) 출발하여 전체 loop의 feedback paths와 주변 소자를 고려합니다.

제공해주신 책의 공식인:

[

R_O \approx RZ + \frac{1}{g{m3}g{m7}(r{o3} // r_{o5})}

]

여기서 중요한 것은 각 파라미터가 가지는 의미입니다.

- ( R_Z )는 DC biasing이나 다른 passive load에 의한 저항을 나타낼 수 있으며,

- ( g{m3} )와 ( g{m7} )은 각각 M3와 M7의 트랜스컨덕턴스를 나타내고,

- ( r{o3} )와 ( r{o5} )는 각각 M3과 M5의 출력 저항입니다.

출력 임피던스는 이러한 요소들에 의해 결정되며, 이는 보통 고전적 MOSFET 증폭기의 출력 저항 모델과 유사한 형태를 가집니다.

적절한 스펙과 회로 파트를 이해하여 전체 회로의 입력, 출력 저항은 물론 각 MOSFET와 관련된 트랜스컨덕턴스를 계산하는 것이 중요합니다. 이러한 계산을 통해 각 노드의 voltage gain, current mirror 효과 등을 통한 전류 흐름이 어떻게 이루어지는지 정확하게 알 수 있습니다.

더 자세한 유사한 사례를 통해 문제 해결에 도움을 받을 수도 있습니다. 마침 유사한 주제를 다루는 링크를 안내드립니다:

위 링크에서 커뮤니티의 다른 수강생들과 경험을 나눌 수 있고, 문제 해결의 실마리를 얻으실 수 있을 것입니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.