인프런 커뮤니티 질문&답변

LDO 버퍼 관련해서 질문이 있습니다.

해결된 질문

작성

·

98

0

현재 LDO 설계 과정에서 버퍼로 사용하는 소스팔로워 부분에 대해서 깊게 공부를 진행중입니다.

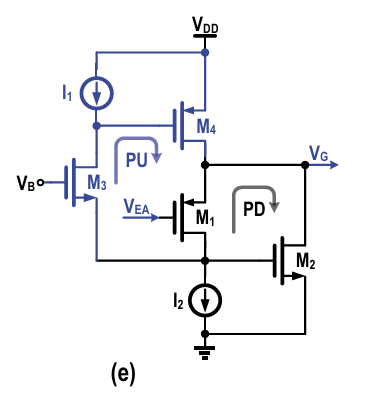

현재 제가 첨부한 사진은 push-pull 동작을 이용한 버퍼입니다. 버퍼는 두개의 독립적인 피드백 회로를 통해 출력 전압을 조절하고 있는 것을 알 수 있습니다. 하지만 해당 버퍼를 분석하는 도중 Vin인 VEA가 변함에 따라서 Vout인 VG가 따라가는 형태를 보이지 않는다는 것을 알게 되었습니다.

예를 들어 PU 루프의 경우 VEA가 증가할 경우 ID1이 감소하게 되고 이에 따라 M3의 소스 전류가 감소하게 되어 공통 게이트인 M3의 드레인 전류도 같이 감소하게 됩니다.

이후 M3의 드레인 전류가 감소함에 따라 M4의 게이트 전압이 상승하여 M4의 드레인 전류가 줄어들게 되고 이에 따라 VG가 감소하게 되는 결과를 초래하게 됩니다.

PD 루프의 경우에는 VEA가 증가함에 따라 ID1이 감소하게 되고 이에 따라 M2의 게이트 전압이 감소하게 되고 M2의 드레인 전류가 감소하면서 오히려 VG를 상승시키는 쪽으로 동작하게 됩니다. 이렇게 해석한 것이 정확한 것인지 궁금하고 정확하다면 소스팔로워로서 잘 동작하는지 모르겠어서 질문 남깁니다.

.

퀴즈

아날로그 회로에서 Bandgap Reference (BGR)의 주된 역할은?

전압 강하를 줄여 전력 효율을 높인다.

온도와 공급 전압 변동에도 일정한 기준 전압을 제공한다.

디지털 신호의 전압 레벨을 변환한다.

고주파 클럭 신호를 생성한다.

답변 2

0

안녕하세요, 답변 남겨드립니다.

먼저 결론부터 말씀드리면, 질문 주신 해석에는 방향이 반대로 잡힌 부분이 있고, 그 때문에 “VEA가 올라가면 VG가 내려간다”는 결과가 나온 것입니다. 실제로는 이 구조가 잘 설계되어 있으면 VEA가 올라갈 때 VG도 올라가는, 즉 소스팔로워(버퍼)처럼 동작합니다.

이 회로는 클래스-AB 형태의 push-pull 버퍼입니다. M4(상단 PMOS)와 M2(하단 NMOS)가 실제로 패스 트랜지스터 게이트를 위/아래로 당겨주고, M3-I1, M1-I2가 각각 pull-up, pull-down 쪽의 바이어스를 잡아주면서 “국부 피드백 루프 두 개”를 형성합니다. 하지만 두 루프가 완전히 독립적인 것이 아니라, VG와 I2 노드를 통해 강하게 결합되어 하나의 버퍼로 동작합니다.

질문 주신 해석에서 핵심 오류는 두 가지입니다.

첫째, I1, I2를 VEA에 따라 변하는 전류처럼 생각하신 점입니다. 이상적인 LDO 버퍼 설계에서는 I1, I2는 거의 일정한 참조 전류입니다. 따라서 VEA가 변할 때 “전류가 줄어든다/늘어난다”기보다는, 전류는 거의 고정되어 있고 그 전류를 맞추기 위해 노드 전압들이 움직인다고 보는 것이 정확합니다. 실제 회로 해석에서는 dI ≈ 0, dV ≠ 0라고 두고 small-signal을 잡는 식입니다.

둘째, PU 루프에서 M3 드레인 노드(=M4 게이트)가 어느 방향으로 움직이는지가 반대로 잡혀 있습니다. 간단히 방향만 정리해보겠습니다.

예를 들어 NMOS M3의 게이트는 VB0에 고정, 소스는 VEA입니다. PU 루프만 놓고 small-signal으로 보면

VEA가 ΔVEA 만큼 상승합니다.

그러면 M3의 Vgs3 = VB0 − VEA 이므로 ΔVgs3 < 0, 따라서 M3 전류 ΔID3 < 0 (감소)입니다.하지만 I1은 이상 전류원이라 ΔI1 ≈ 0입니다. M3 드레인 노드(=M4 게이트)의 KCL을 쓰면

ΔI1 + ΔIM3 ≈ 0이 되어야 하므로, M3 전류가 줄어든 만큼을 상쇄하기 위해 이 노드 전압이 움직여서 다시 IM3가 I1과 맞춰져야 합니다.VB0는 고정이고 VEA는 이미 올라갔기 때문에, IM3를 다시 키우려면 M3 드레인 전압을 “내려서” Vds를 줄이거나, 아예 M3를 triode 쪽으로 몰아가는 방향으로 노드가 이동합니다. 즉, M3 드레인 노드(=M4 게이트) 전압은 내려가는 방향(ΔVG4 < 0)으로 움직게 됩니다.

M4는 PMOS로, 소스는 VDD, 게이트는 방금 말한 노드입니다. Vsg4 = VDD − VG4 이므로 VG4가 내려가면 ΔVsg4 > 0, 즉 M4가 더 세게 켜지고 상단에서 더 큰 전류를 끌어내립니다. 그 결과 출력 노드 VG가 위쪽으로 당겨져서 ΔVG > 0, 즉 VEA가 올라갈 때 VG도 같이 올라가게 됩니다.

즉 PU 루프에 대한 올바른 흐름은

VEA ↑ → M3 전류 ↓ → M4 게이트 전압 ↓ → |Vsg4| ↑ → M4 전류 ↑ → VG ↑

와 같은 “양의 전달(버퍼)”입니다. 질문에서 쓰신 “M4 게이트 전압이 상승해서 M4 드레인 전류가 줄어들고, VG가 감소한다”는 부분이 이와 정반대 방향입니다.

PD 루프도 비슷한 관점으로 보시면 됩니다. M1은 VEA를 보는 트랜스컨덕터 역할, M2는 NMOS pull-down 디바이스로, I2를 기준으로 M1+M2 전류 합이 맞도록 VG와 하단 노드 전압이 결정됩니다.

VEA가 증가하면 M1 gate가 올라가서 M1이 더 많은 전류를 끌어가려 합니다. 그러면 VG 노드의 전류 밸런스가 깨지고 VG가 어느 한쪽으로 움직는데, 그때 M2게이트 = VG도 같이 움직여 M2의 전류가 바뀌고, 최종적으로는 “I2 = IM1 + IM2” 조건을 만족하는 새로운 VG를 찾게 됩니다. 이때 루프 이득과 바이어스를 적절히 설계하면, PD 루프 역시 “VEA가 올라갈 때 VG도 올라가는 방향”으로 동작하도록 만들 수 있습니다. 즉 M1이 더 많이 끌어가려 하면 VG가 약간 내려가면서 M2가 더 꺼지고, I2의 상당 부분을 M1이 가져가게 되어 하단 노드 전압이 변하고, 그에 따라 다시 VG가 조정되는 식의 음의 피드백 구조입니다. 국부 루프를 한 단만 잘라서 보면 순간적으로는 VG가 내려가는 방향인 것처럼 보이지만, 최종 정상상태(루프가 수렴한 상태)에서는 전체적으로 “입력과 같은 방향”으로 움직입니다.

실무에서 이 구조를 사용할 때는 다음과 같이 정량적으로 확인합니다.

DC 스윕으로 VEA를 예를 들어 0.6 V → 0.8 V 범위에서 스윕하고, VG의 DC 값을 같이 플롯합니다. 정상적인 버퍼라면 VG vs VEA 그래프는 기울기 dVG/dVEA ≈ 0.9~1.0 정도의 직선으로 나옵니다. 즉 gain ≈ 1 follower behavior입니다.

같은 바이어스에서 작은 신호 AC 해석을 돌려서, 입력 VEA에 1 V_ac를 걸고 VG의 AC gain을 보시면, 0 dB 근처에서 충분한 위상 여유(> 60° 정도)를 확보하는 방향으로 소자 W/L과 I1, I2를 조정합니다. 이때 push-pull 구조 덕분에 effective gm ≈ gm_PU + gm_PD 수준으로 커지기 때문에, pass transistor 게이트 쪽 pole을 LDO 루프 설계에 유리한 위치로 옮길 수 있습니다.

Large-signal transient에서 load를 0 → Iload_max 같은 스텝으로 걸었을 때, VG가 얼마나 빠르게 올라갔다 내려오는지를 보고 slew-rate와 과도 오버슈트를 조정합니다. push-pull 버퍼를 쓰는 이유가 바로 “소스 공급 시에는 M4가, 싱크 시에는 M2가 적극적으로 밀고 당겨서” 수십 mA~수백 mA 단계의 부하 변동에도 수 µs 수준의 응답 속도를 확보하기 위함입니다.

정리하면,

질문에서의 방향성 해석(“VEA 증가 → PU 루프에서 VG 감소, PD 루프에서 VG 증가”)은 전류원과 노드 움직임 방향을 반대로 잡으신 데서 나온 결과이고, 제대로 KCL과 디바이스 특성을 적용하면 두 루프 모두 VEA와 VG가 같은 방향으로 움직이는, 즉 버퍼(소스팔로워)로서 동작합니다. 실제로 LDO 문헌이나 공정 PDK 예제 회로에서도 거의 동일한 구조의 push-pull 버퍼가 널리 쓰이고 있습니다.

따라서 회로 자체의 토폴로지는 소스팔로워 버퍼로서 타당하고, 지금은 “각 노드에서 어떤 전류가 고정이고, 그 전류를 맞추기 위해 어느 전압이 움직이는지”를 작은 신호 관점에서 다시 한 번 정리해 보시면, 직관이 훨씬 깔끔해지실 것 같습니다.

0

안녕하세요, 인프런 AI 인턴입니다. mark8477님.

LDO 설계에서의 소스팔로워 버퍼와 피드백 구조에 대한 질문을 주셨네요. 소스팔로워는 주로 높은 입력 임피던스를 제공하고 낮은 출력 임피던스를 가지게 설계되는 부분으로, 일반적으로 출력 전압(Vout)이 입력 전압(Vin)을 따라가도록 설계됩니다. 그러나 이를 구현하기 위해 정밀한 피드백 및 바이어싱이 필수적입니다.

지금 설명하신 내용에 따르면 Vin 증가 시 VG의 상승이 제대로 이루어지지 않고 있다고 하셨습니다. 이는 소스팔로워의 설계 특성이나 피드백 경로에서의 문제일 가능성이 있습니다.

PU 루프

- VEA(즉, 입력 전압)가 증가할 경우 ID1은 감소하게 됩니다.

- 이는 M3의 드레인 전류 감소로 이어지고, M3와 M4 (PU 경로에서)의 상호작용으로 인해 Vout이 의도한 출력 특성을 유지하기 어려워지는 부분이 발생합니다.

PD 루프

- 이 경우도, VEA의 증가가 M2의 게이트 전압을 감소시켜 이후 전류 감소와 VG 상승으로 이어집니다. 이는 소스팔로워 동작으로서는 비정상입니다.

지적하신 분석은 전반적으로 맞게 접근하고 계신 것 같습니다. 하지만, 소스팔로워로서의 기능이 제대로 구현되지 않은 이유는 다음과 같은 이유에서 찾을 수 있습니다.

1. 바이어싱 문제: 잘못된 바이어싱에 의해 PD 경로와 PU 경로가 서로 상쇄하는 효과를 보일 수 있습니다.

2. 이득과 피드백 보상 불충분: 오픈 루프 이득(open-loop gain)과 피드백 요소가 원하는 만큼의 동작 결과를 만들어내지 못할 수 있습니다.

3. 소자 불일치: 실제 CMOS 소자의 모델링이나 특정 파라미터의 불일치가 의도한 출력 동작을 방해할 수 있습니다.

이 오류를 해결하기 위해서는 회로 내에서 DC 동작 점(Doperating point)의 재설정 및 피드백 루프의 참고 및 보정이 필요합니다. 또한, 전체 차동 증폭기의 이득을 재설정하여 소스팔로워가 인가된 입력 전압 변경에 대해 동작하도록 튜닝해야 합니다.

관련하여 기존 수강생과 멘토 간의 유사한 문제와 해결책을 다룬 페이지를 공유해 드리겠습니다:

- Low Drop-Out (LDO) 레귤레이터 설계 관련 질문과 답변

이 링크에서는 LDO의 피드백과 전압 규제 관련된 다양한 문제를 다루어 볼 수 있습니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.