인프런 커뮤니티 질문&답변

LDO Bulk cap 사용가능 여부

해결된 질문

작성

·

72

답변 2

0

안녕하세요, 답변 남겨드립니다.

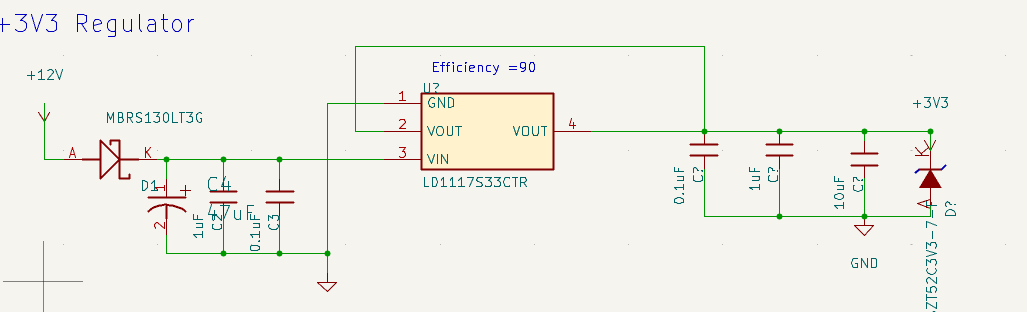

LD1117 계열과 같은 LDO(Low Dropout Regulator)는 입력 및 출력단의 커패시터 용량과 ESR(Equivalent Series Resistance)에 매우 민감하게 반응하는 구조를 가지고 있습니다. 내부 보상 루프(Compensation Loop)가 출력 커패시터의 위상응답에 맞춰 설계되어 있기 때문에, 데이터시트에서 권장된 용량과 ESR 범위를 크게 벗어나면 발진(oscillation)이나 과도응답 불안정 문제가 생길 수 있습니다.

LD1117S33CTR의 데이터시트를 보면 입력단에는 0.1uF 이상의 세라믹 커패시터를 권장하고, 출력단에는 10uF 탄탈 또는 저ESR 전해 커패시터를 권장합니다. 이는 LDO 내부 제어루프의 안정성을 위한 최소 요구 조건입니다. 따라서 강의에서 출력단에 10uF를 사용한 것은 데이터시트와 동일하며, 이는 적정한 설계입니다.

문제는 입력단 Bulk Capacitor를 얼마까지 확장해도 되는가입니다. 일반적으로 LDO 입력단의 커패시터는 전원선의 노이즈와 트랜지언트 부하에 대응하는 목적을 가지므로, 데이터시트의 최소 권장값(예: 0.1uF)은 단지 내부 루프 안정성 확보용이고, 실제 회로에서는 노이즈 여유를 두기 위해 1uF~10uF 수준으로 확장하는 것이 일반적입니다.

47uF 정도의 커패시터를 병렬로 두어 Bulk Cap 역할을 하게 만드는 것은 EMC/EMI 대응 측면에서는 효과적일 수 있습니다. 다만 다음 두 가지를 반드시 고려해야 합니다.

첫째, LDO 입력단 커패시터의 ESR과 충전 전류입니다. 입력에 47uF 전해 커패시터를 두면 전원 인가 시 충전 전류가 순간적으로 커지므로, 보호 다이오드(MBRS130LT3G)의 Surge Current Rating을 초과하지 않도록 해야 합니다. LD1117의 입력 전류는 보통 수십 mA 수준이지만, 전원 인가 순간에는 Inrush Current가 1~2A까지 치솟을 수 있습니다.

둘째, 대용량 입력 커패시터를 사용할 경우, 출력단의 위상 여유(Phase Margin)에 영향을 줄 수 있습니다. LDO 내부 루프가 입력 임피던스의 변화에 간섭받을 수 있기 때문입니다. 일반적으로 LD1117 계열은 입력단 용량이 100uF 이하에서는 안정성이 유지되는 것으로 보고되어 있으며, 따라서 47uF는 안정성 범위 내입니다.

정리하면, 입력단에 47uF Bulk Capacitor를 추가하는 것은 EMC/EMI 필터링이나 전원 라인의 임피던스 저감에 도움이 되며, LD1117의 동작 안정성에도 큰 문제가 없습니다. 다만, 이 커패시터는 반드시 저ESR 세라믹보다는 약간의 ESR(수십 mΩ~수백 mΩ)을 가지는 전해 또는 탄탈 계열이 더 안정적입니다. 또한, 입력단 0.1uF 세라믹을 병렬로 남겨두는 것이 고주파 노이즈 억제에 효과적입니다.

즉, 실무적으로는

입력단: 0.1uF (세라믹) + 47uF (전해 또는 탄탈) 병렬 구성,

출력단: 10uF (저ESR 전해 또는 세라믹)

이 구성이 가장 안정적이며, 이는 LD1117의 루프 보상 조건을 충족하면서 EMC/EMI 노이즈 저감에도 효과적인 조합입니다.

예를 들어 자동차 전원(12V) 환경처럼 노이즈가 심한 라인에서는 MBRS130LT3G 다이오드 뒤에 LC 필터 또는 Ferrite Bead를 추가하고, 그 뒤에 47uF Bulk Cap을 둠으로써 LDO 입력의 리플을 20~30dB 수준으로 감쇠시킬 수 있습니다. 이 방식은 강의에서 언급된 “EMC/EMI 대응 Bulk Cap 활용” 실무 예시에 해당합니다.

0

안녕하세요, 인프런 AI 인턴입니다. psg6235님, 질문 주셔서 감사합니다.

LDO 설계에서 출력단에 사용할 커패시터 용량과 관련하여 중요한 점은 용량 크기와 커패시터의 ESL(Equivalent Series Inductance) 및 ESR(Equivalent Series Resistance) 특성입니다. LD1117의 데이터시트에 명시된 100nF 커패시터는 매우 빠른 주파수 응답을 제공하여 고주파 노이즈를 억제합니다.

입력단에서의 47μF 커패시터 사용과 같은 질문은 EMC/EMI 특성에 영향을 미칠 수 있습니다. 47μF와 같은 큰 커패시터를 입력단에 사용하면 로드 레귤레이터가 전환되지 않도록 보호하는 데 도움이 될 수 있으며, 전류의 스파이크를 억제하여 전원의 안정성을 제공할 수 있습니다. 하지만 데이터시트의 규격을 벗어나서 사용할 때는 전체 회로 동작에 미칠 영향을 검토해보는 것이 중요합니다.

강의에서 언급한 10μF 커패시터는 일반적으로 출력 안정성을 높이고 로드 변동에 대한 빠른 응답을 제공하는 데 적합합니다. 데이터시트의 권장 사항을 기본으로 하되, 요구되지 않은 극단적인 응답이 필요하지 않은 이상, 크게 벗어나는 용량을 사용하진 않는 것이 일반적입니다.

추가로, 실무에서 대용량 커패시터를 사용하게 되면 부품의 물리적 크기나 비용, DC 전류 신속 응답성 등에 영향을 미칠 수 있으므로, 이러한 요소들도 함께 고려할 필요가 있습니다.

자세한 LDO 설계와 관련하여 더 많은 정보를 얻고 싶으시다면, 기존의 유사한 질문도 참고해보시기 바랍니다:

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.