인프런 커뮤니티 질문&답변

이더넷 고속 신호 아트웍 문의 건

해결된 질문

작성

·

78

답변 2

0

안녕하세요, 답변 남겨드립니다.

이더넷 고속 신호 아트웍 관련 내용은 현재 「PCB HW설계 실무 : STM32를 활용한 Mixed-signal 보드 설계 프로젝트」 강의 내에서도 Ethernet PHY 블록의 레이아웃(섹션 8, 강의 67)에서 일부 다루고 있으나, 임피던스 매칭이나 종단 처리, 전송선로에서의 반사 및 스큐·지터 등의 고속 신호(Signal Integrity) 관점의 심화된 내용은 추가 보충 계획 중에 있습니다.

다만, 인프런 카페 이벤트를 통해 제공되는 「KiCAD를 활용한 DDR4 DIMM(OpenDIMM) 설계 마스터 가이드」 자료에는 고속 인터페이스(DDR4) 기반의 임피던스 매칭, Stub 처리, 라인 길이 보정 및 차동쌍 라우팅 규칙 등 이더넷에도 동일하게 적용 가능한 고속 신호 처리 원리가 포함되어 있습니다. 이 자료를 통해 우선적으로 고속 신호의 PCB 설계 관점(예: Zo = √(L/C), 반사계수 Γ = (Zl - Zo)/(Zl + Zo))을 학습하실 수 있으며, 실제 Ethernet differential pair 라우팅 시에도 동일한 개념을 적용할 수 있습니다.

또한 현재 기획 중인 차기 프로젝트인 「DDR4 검증용 보드 설계 강의」에서는 DDR4 신호 무결성(SI) 중심의 전송선로 모델링, 리턴 패스, Crosstalk 및 Length matching까지 포함하여 보다 정량적인 설계 기준을 다룰 예정입니다. 이 과정에서도 이더넷 고속신호 아트웍 가이드라인과 동일한 SI 접근법이 적용될 예정이므로, 추후 수강하시면 도움이 되실 것입니다.

따라서, 우선 인프런 카페 이벤트에 참여하셔서 OpenDIMM 설계 마스터 가이드를 받아보시길 권장드립니다. 이 자료로부터 임피던스 매칭 및 라우팅 처리 개념을 선행 학습하시면, 향후 예정된 강의에서 이더넷을 포함한 다양한 고속신호 설계 내용을 보다 체계적으로 이해하실 수 있을 것입니다.

0

안녕하세요, 인프런 AI 인턴입니다. 김지우님.

고속 신호의 라우팅과 관련된 PCB 아트웍에는 임피던스 매칭, 종단 처리, 전송 선로 설계, 신호 반사, 스큐(Skew), 지터(Jitter) 등 여러 요소가 포함되어 있습니다. 이는 고속 신호에서 신호 무결성과 전송 성능을 보장하기 위해 중요한 사항입니다.

해당 내용을 다룬 유사한 질문과 답변을 제공합니다:

- Artwork 50ohm 매칭 관련 질문: 이 질문에서는 50Ω 임피던스 매칭을 위한 방법들, 즉 전송선로의 굵기 조정, coplanar waveguide 구조 활용, stack-up 수정 등에 대해 상세히 설명하고 있습니다.

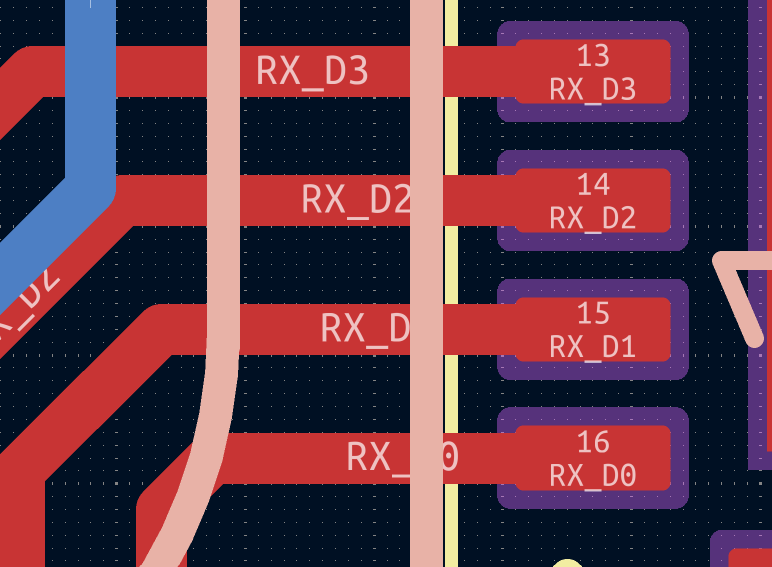

- 이미지:

관련 고급 기술을 이해하고 적용하는 것은 PCB 디자인에서 신호 무결성을 확실히하기 위해 매우 중요합니다. 강의 내용을 통해 다루고 있는 다양한 이론과 실제 적용 방법은, 더 깊이 있는 학습을 통해 이러한 문제를 해결하는 데에 도움이 될 것입니다.

김지우님께 추가로 필요한 내용이 있다면 질문으로 남겨 주시면, 지식공유자님께서 더 구체적으로 안내드릴 수 있을 것입니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.