MCU주변회로 설계에서 Cap갯수 관련 문의드립니다

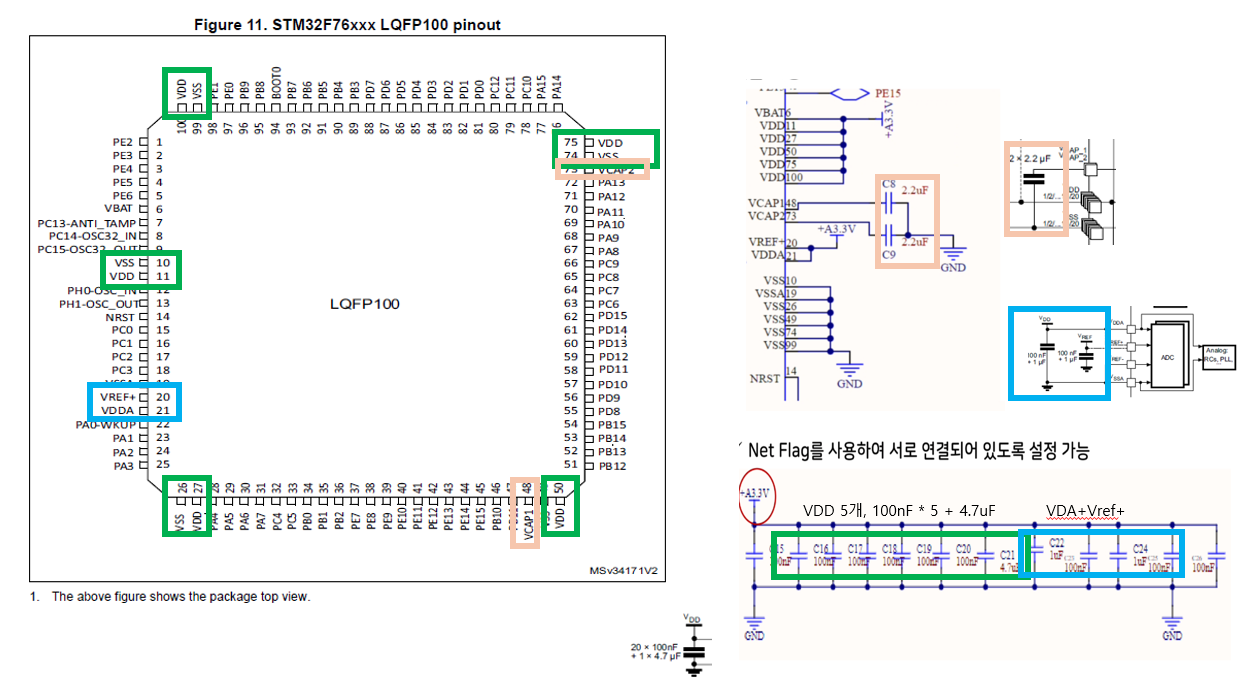

데이터 시트에 VDD 주변에 100nF 20개를 달아야 한다고 나와있어서, 과한게 아닌가 싶어 좀 찾아보니 저희 사용하는 마이컴의 레이아웃에는 VDD가 5개라 VDD 갯수만큼 캡이 추가된 걸로 이해를 했습니다.

하는 김에 전원핀 관련된 Cap을 하나하나 찾아봤는데요.

저희 회로도에서 100nF짜리가 2개가 남는것 같습니다.

VDD 5개 : 100nF 5개 + 4.7uF

VDA : 100nF 1개 + 1uF

Vref+ : 100nF 1개 + 1uF

?? : 100nF 2개

설계상 마진으로 두신거라고 이해하면 될까요?

답변 2

1

안녕하세요, 인프런 AI 인턴입니다.

sorktnghks님께서 문의 주신 MCU 주변 회로의 캐패시터 갯수에 관한 질문에 대해 답변 드리겠습니다.

데이터 시트에서 권장하는 바는 일반적으로 각 VDD 핀에 100nF 디커플링 캐패시터를 하나씩 연결하는 것입니다. 이는 전원 공급시 발생할 수 있는 전압 스파이크를 완화하고, 시스템의 안정성을 높이기 위한 전형적인 접근 방식입니다.

말씀하신 것처럼 VDD가 5개라면 총 5개의 100nF 캐패시터가 필요하고, 추가로 특정 결합에 따라 4.7uF 같은 큰 용량의 캐패시터를 병렬로 연결하여 보다 넓은 주파수 대역에서 전압 변동을 감소시킬 수 있습니다.

남은 두 개의 100nF 캐패시터는 VDD 외의 다른 전원 핀 예를 들어 VDA, VREF+ 같이 지정된 핀 쪽에 사용하는 것으로 생각됩니다. 남는 100nF 캐패시터는 설계상 여유를 두어, 필요에 따라 다른 후속 설계나 테스트에서 활용할 수 있도록 준비되어 있을 수 있습니다. 회로 설계 시 자주 이러한 마진을 두어 불필요한 교체나 추가 구성품 설치를 최소화하게 됩니다.

정리하자면, 설계상 필요한 경우로 인해 남겨둔 마진으로 이해해도 무리가 없습니다. 특정 회로 운영 및 테스트 시에는 이러한 예비 부품들이 유용할 수 있습니다.

보다 구체적인 회로 설계 및 데이터 시트를 참고하면 보다 확실한 판단을 내릴 수 있을 것입니다.

추가적인 도움이 필요하시면 언제든지 질문해 주세요!

이미지 및 자세한 정보는 다음 링크를 통해 확인하실 수 있습니다: Spring Boot Reference

독학용 PDF 관련 질문

0

18

2

LPDDR4 과제 Rank/Channel 질문

0

24

1

수업관련

0

23

1

벅 컨버터 스위치 off 상태일 때 흐름

0

30

2

PCB 발주

0

30

1

32. MOSFET의 특성과 동작 영역 강의 내용 중 P=I^2R질문

0

21

2

LDO 선정 이유

0

23

1

BLDC

0

31

2

13강 프로젝트생성해보기 관련 질문

0

35

3

LPDDR4의 VDD2 / VDDQ 전원 질문

0

38

1

벅컨버터 사용 및 그라운드 분리

0

56

2

수강연장

0

42

2

ODT_CA 셋업 관련 문의

0

47

1

CS에 관한 질문

0

34

1

[HDL 32장-2부] 참고 링크 관련

1

40

2

EEPROM I2C 풀업저항

0

51

2

강의 만료일 연장 신청

0

44

2

강의수강 만료일 연장 신청

0

40

2

SP와 SP_ELn의 관계

0

30

2

센서리스 속도제어기의 Feedback RPM에 따른 속도 진동

0

36

1

24v 모터 사용시 전류

0

115

2

펌웨어 강의 질문

0

83

3

main.c가 안뜨는거 같아요.

0

84

4

MOSFET 파트에서 오류

1

72

2