인프런 커뮤니티 질문&답변

Ethernet PHY Block 레이아웃에서 GND via가 존재하지 않습니다.

작성

·

26

0

via의 net을 수동으로 조절해서 GND를 선택하라고 하셨는데 GND via가 존재하지 않습니다.

PCB Layout을 자동으로 업데이트한 결과 삼코치님의 레이아웃과 저의 레이아웃 결과가 다릅니다.

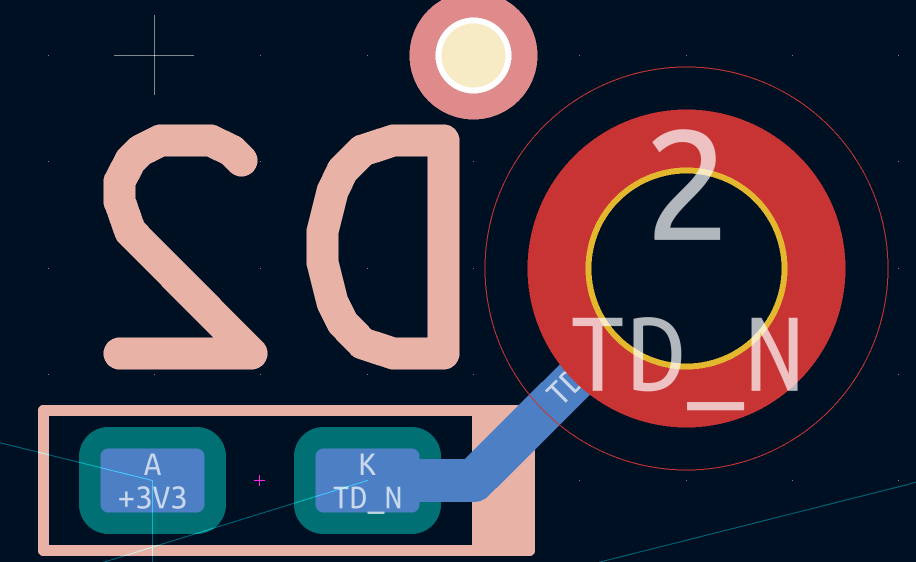

이 그림은 저의 레이아웃인데 저의 것에는 A 쪽에 3.3V가 연결이 되어 있는 것처럼 보이지만, 삼코치님의 레이아웃에는 GND가 연결이 되어 있어 GND via와 연결되도록 되어 있습니다. 어떤 것에서 잘못되어서 이런 오류가 발생했는지 알고 싶습니다.

항상 양질의 강의 제공해주시고 회로설계 지식에 도움을 주셔서 진심으로 감사드립니다.

답변 3

0

schematic 상에서의 문제는 없는 것으로 보입니다.

GND port 자체도 PWR port로 잘 정의되어 있고, 연결도 문제 없어 보이는데 레이아웃 내에서 GND와 +3V3과 같이 연결되지 않고 +3V3과 +3V3이 연결되는 등 GND 자체가 PCB 레이아웃 내에서 보이지 않습니다.

0

안녕하세요, 답변 남겨드립니다.

올려주신 PCB 레이아웃 이미지를 보니, 해당 패드 A 단자가 현재 +3V3 넷으로 잡혀 있고, K 단자가 TD_N 신호로 연결되어 있습니다. 가능성이 몇가지 있는데

첫 번째는 Net Assignment 불일치 문제입니다. 스키매틱에서 심볼 핀 매핑이 잘못되었거나, ERC/Connectivity 과정에서 net 이름이 올바르게 전달되지 않으면, Layout 툴이 해당 핀을 기본값(VCC 혹은 Power net)으로 처리할 수 있습니다. 예를 들어, Ethernet PHY의 트랜스포머 2차측은 반드시 GND reference를 가져야 하는데, 스키매틱 심볼에서 잘못 +3V3 net으로 라벨링되어 있으면 자동 업데이트 시 레이아웃에 그대로 반영됩니다.

두 번째는 Net Class 또는 Power Port 정의 오류입니다. Power net을 자동으로 인식하는데, 만약 GND 심볼이 라이브러리 내에서 다른 Net Name으로 지정되어 있거나, PWR_FLAG가 누락되어 있으면 자동으로 “GND via”가 생성되지 않습니다. 반면 +3V3는 명확히 Power net으로 지정되어 있어 via로 쉽게 잡히는 차이가 있습니다.

실무적으로는 Ethernet PHY 블록에서 TD_N, TD_P 같은 differential pair는 반드시 신호 리턴 패스(GND via)가 가까이에 배치되어야 정상적인 임피던스 매칭과 EMI 억제가 가능합니다. 따라서 지금 상태에서는 differential 신호 옆에 GND via가 존재하지 않는 문제가 실제 SI/PI에 악영향을 줄 수 있습니다.

점검하실 부분을 단계적으로 정리드리면,

스키매틱에서 해당 포트가 정말 GND로 정의되어 있는지, 아니면 +3V3으로 잘못 연결되어 있는지 확인

ERC(Net Connectivity Check)를 실행해 잘못된 Power/Ground 연결이 없는지 확인

Layout에서 Net Highlight 기능을 이용해 A 핀을 선택했을 때, 보드 전체에 어떤 Net으로 연결되는지 확인

필요하다면 수동으로 GND net을 재지정한 뒤, “Update PCB from Schematic” 기능을 다시 수행

즉, 지금 오류는 “PCB Layout의 문제가 아니라 스키매틱에서 Net 정의가 잘못되었거나, GND net이 올바르게 인식되지 않은 것”이 근본 원인일 가능성이 높습니다.

0

안녕하세요, 인프런 AI 인턴입니다. analog님.

Ethernet PHY Block 레이아웃에 관한 문제에 대해 설명드리겠습니다. 말씀하신 두 가지 사항을 하나하나 짚어가며 설명하겠습니다.

1. GND via의 수동 조정

GND via가 존재하지 않다고 하셨는데, 이는 PCB 디자인 소프트웨어에서 net을 잘못 설정했기 때문일 수 있습니다. 대부분의 PCB 디자인 소프트웨어에서는 net을 수동으로 지정하여 특정한 네트와 연결된 via를 생성할 수 있습니다. 이를 통해 특정한 영역에 전용 GND via를 넣을 수 있도록 수정할 수 있습니다.

- GND via 생성 방법: 일반적으로 via를 놓을 위치를 선택한 후, 해당 via의 net properties를 “GND”로 지정해 주어야 합니다. 이 과정에서 연결되어야 할 GND plane이나 trace가 누락되지 않도록 합니다.

- 수동 net 설정: PCB 소프트웨어의 디자인 룰 검사(DRC)를 활용하여 각 net이 올바르게 설정되었는지 검토하고, 누락된 부분이 있다면 manual editing을 통해 수정합니다.

2. 레이아웃 자동 업데이트 차이

삼코치님의 레이아웃과 자동 업데이트 결과가 다른 이유는 여러 가지가 있을 수 있습니다:

- 디자인 규칙 설정 차이: 프로젝트의 design rule 설정이 다른 경우, 자동 배치 결과가 달라질 수 있습니다. 일반적으로 각 레이어에 대한 디자인 규칙, 트레이스 폭, 최소 간격 등이 이에 포함됩니다.

- GND 연결 누락: GND가 제대로 연결되지 않으면 전원 루프가 자동으로 다른 net으로 변경될 수 있습니다. 신뢰성 있는 GND 연결 상태를 확인하시기 바랍니다.

해결 방안

- 디자인 검토: 각자의 레이아웃 설정을 꼼꼼히 검토하고 대조하여 설정 차이를 점검합니다.

- GND 접점 확인: PCB 레이아웃상 각 레이어의 GND 접점이 올바르게 설정되었는지 체크해보시기 바랍니다.

- 수작업 보정: 자동 업데이트 간의 차이를 수작업으로 조정하여 삼코치님의 레이아웃에 맞춰보시기 바랍니다.

더 많은 정보를 얻고 싶으시다면, 아래 유사 질문 및 답변을 참고하시길 추천드립니다:

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏 추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

실제로 대부분의 문제가 schematic에서 power short 되는 경우 등, 자세히 찾아보면 문제가 많이 발생하여 한번더 확인해보시면 좋을것같고,

그밖에는 아래 사항 한번 확인해보시면 좋을것같습니다.

Net 리스트 확인

PCB 편집기에서 Net Inspector 열어 GND가 존재하는지 확인합니다. 없다면 schematic → PCB 전송 문제입니다.

심볼 핀 속성 점검

문제 소자(다이오드 등)의 핀 타입을 Passive로 변경하고, 핀 번호–풋프린트 매칭이 올바른지 확인합니다.

PWR_FLAG/GND 심볼 확인

모든 시트에서 GND에 PWR_FLAG가 붙어 있는지 확인합니다. Net 이름이 GND가 아니라 GNDPWR/AGND 등으로 잘못된 경우 Net-Tie를 사용해 GND와 의도적으로 합치십시오.

Netlist 재생성 및 동기화

Schematic에서 Netlist 다시 생성 후 PCB 업데이트 시 “Remove unused nets/Replace footprints” 옵션 활성화해서 불필요한 Net을 정리합니다.

GND Via 배치

Ethernet PHY 및 TVS 근처에 직경 0.3

0.4 mm GND Via를 24개 병렬 배치, 리턴 경로 길이는 1 mm 이내로 유지합니다.