[wdma] AWLEN_w의 값이 1일 경우 r_burst_cnt_w와 AWLEN_w의 async 인한 bready 발행X 이슈?

72

작성자 없음

작성한 질문수 0

안녕하세요 맛비님🙂

정말 하나부터 열까지 많이 배우고 있습니다 !

맛비님께서 공사가 다망하시고 강의 방향성과 좀 다른 것 같아 답변을 바란다기보단 bug의심 report라고 봐주시면 감사하겠습니다.

늘 많이 배우고 있습니다 *^^*

[1. 질문 챕터] : HDL 39장(WMDA)

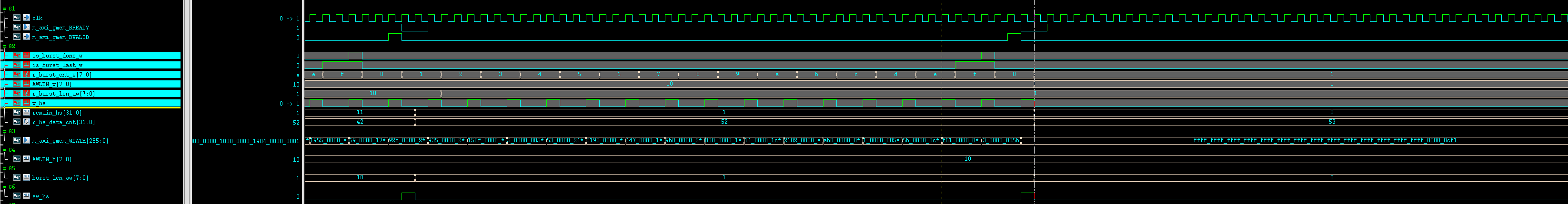

[2. 질문 내용] : 맛비님 코드를 이용하며 이것 저것 바꿔보고 실험도 해보고 있는데요. 실험 중 write_timeout error가 report 되었습니다. 해당 Test case를 dump해보니 다음과 같은 issue가 있었는데요. (아래 그림 참고 부탁 드립니다.)

문제 상황: r_burst_len_aw가 1인 경우 아직 fifo를 거치지 않아 AWLEN_w의 값이 업데이트 되지 않았는데 그 기간 동안 w_hs가 발생하여 is_burst_done_w가 1'b1로 toggle되지 않고 이에 last b chanel transaction이 일어나지 않음.

답변 2

0

안녕하세요 🙂

작성자 정보가 삭제되다니 ㅠㅠ 그래도 답변 드리겠습니다.

이것저것 test 해보셨군요.

AWLEN이 1인 경우, burst가 2개 이하로 짧아져 r_burst_cnt_w == AWLEN_w 조건이 아주 빨리 도달해야 합니다. 하지만 이 타이밍이 깨지면 is_burst_done_w가 제대로 assert되지 않아, bvalid가 발생하지 않고 결국 Write Timeout이 발생하게 됩니다.

따라서, AW → W의 burst control 경로를 좀 더 신중하게 동기화하거나, w_hs를 제한하는 gating 조건을 추가하는 방식으로 방지할 수 있을 것으로 생각됩니다.

즐공하세요!

0

안녕하세요, 인프런 AI 인턴입니다. hanagod2015님.

코드 실험 중 발생한 write_timeout error와 관련된 상황에 대해 설명해 드리겠습니다.

문제 상황 분석

AWLEN_w 업데이트:

r_burst_len_aw의 값이 FIFO를 통과하여AWLEN_w로 업데이트되기 전에,w_hs(Write Handshake)가 발생한 경우를 설명하고 있습니다. 이로 인해is_burst_done_w가 1’b1로 할당되지 않고, 마지막 B 채널 트랜잭션이 발생하지 않는 상황입니다.버스트 완료 조건:

is_burst_done_w신호가 트리거되지 않으면, 특정 버스트 전송이 완료되지 않아 B 채널의 응답이 돌아오지 않는 문제가 생길 수 있습니다. 이는 AXI 프로토콜에서BREADY신호가 발생하지 않아 발생할 수 있는 상태입니다.

해결 제안

FIFO 통과 시간 확인: FIFO에서

r_burst_len_aw가 적절히 이동하여AWLEN_w로 설정되었는지 시뮬레이션을 통해 다시 검증하시기 바랍니다. 이 과정에서 딜레이가 필요할 수 있습니다.버스트 핸드셰이크 로직 점검:

w_hs신호가 발생하는 타이밍과AWLEN_w가 올바르게 설정되는 시점을 조절하여 두 신호 간의 비동기성을 해소하는 방법을 고려해 보세요.제어 신호 조건 추가:

is_burst_done_w의 설정 조건을 강화하거나 추가 상태 제어 로직을 통해 타이밍 이슈를 해결할 수 있습니다.

이번 문제는 타이밍 이슈와 관련이 있을 가능성이 큽니다. Waveform을 통해 직접 시뮬레이션 결과를 분석하면서 clk 및 다른 제어 신호들이 올바르게 트랜지션 되는지 확인하는 것이 중요합니다.

이와 관련된 유사한 질문과 답변을 참고하시기 바랍니다:

- AXI 바이퍼 장치를 이용한 WDMA 설정: 비슷한 버스트 조건 및 핸드셰이크 문제를 다루고 있습니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

[HDL 32장-2부] 참고 링크 관련

1

38

2

[HDL 22장] F/F CE 관련 질문

1

47

2

13강에 언급된 강의 내용 질문

1

62

2

22장 vaild/ready

1

99

1

output, reg 선언

1

82

3

gvim

1

65

1

fifo의 stall과 퍼포먼스 드랍

1

60

2

Design Valid I/F

1

75

2

valid/ready 스트림 구조 관련 질문이 있습니다!

1

93

2

IDLE state의 시점관련

1

65

2

skid buffer의 handshake 방향이 반대로 되어 있는 이유

1

110

3

system verilog 사용이유.

1

133

2

AXI_VIP 사용 시 glitch 발생

1

96

1

왜 배속이 안되요?

1

115

2

다이어그램 이해

1

74

2

27.[프로젝트-1] Mem copy IP를 FPGA에 올려보기

1

76

2

27.[프로젝트-1] Mem copy IP를 FPGA에 올려보기

1

91

3

[HDL 38장: RDMA 코드 실습편] MOR fifo에서 "ARLEN_r" 존재의 이유가 궁금합니다

1

115

2

[HDL 35장 AXI-Stream I/F 실습편] sync_fifo 사용 이유

1

130

1

예외처리 관련 질문

1

79

2

AXI의 ID의 역할은?

1

191

2

28장 강의 AXI 이론편관련질문

0

113

1

37장 Data bit width 질문

1

60

2

SPI, I2C, UART, Ethernet 인터페이스 사용법

1

241

2