인프런 커뮤니티 질문&답변

DRC Error 문의

해결된 질문

작성

·

142

0

안녕하세요 삼코치님, Artwork 작업 중

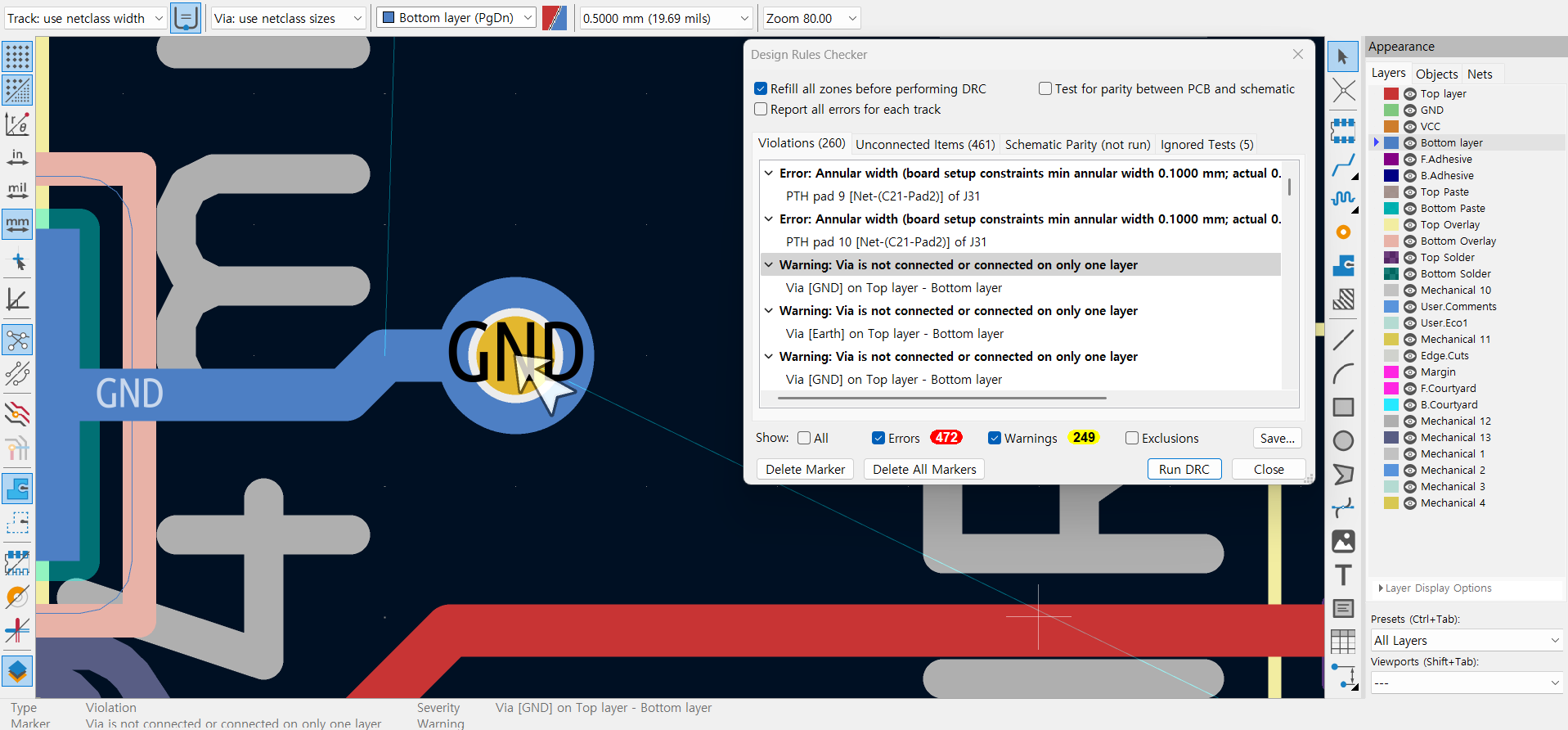

궁금한 점이 생겨 질문 남깁니다. 현재 강의의 회로에서 PHY CHIP 먼저 Routing을 하고 있었고 Design rule도 체크할 겸 DRC를 하는 와중에 해결이 안되는 부분이 있어 확인 요청 드립니다.

Bottom layer에서 GND의 VIA를 연결했는데, 연결이 되어 있지 않다고 오류가 발생했습니다.

VIA 자체에는 Full layer가 routing 되어있어서 큰 문제는 없을 거 같은데, 현재 power plane의 via에만 해당 DRC 오류가 발생하여, 과제 진행에 어려움을 겪고 있습니다.

확인해주시면 감사하겠습니다.

답변 2

0

안녕하세요, 답변 남겨드립니다.

현재 보시는 DRC 오류는 "Via is not connected or connected on only one layer"라는 경고로, 말 그대로 해당 VIA가 두 레이어(Top Layer와 Bottom Layer) 중 한쪽 레이어에서만 전기적으로 연결되어 있으며, 다른 쪽에서는 연결되지 않았다고 판단되었을 때 발생하는 대표적인 경고입니다. 이 문제는 특히 GND plane과 같이 Zone Fill(구역 도포) 방식으로 구성된 레이어에서 자주 나타나며, 그 이유는 단순히 겉보기상 VIA가 fill 안에 위치한다고 해서, 그것이 곧바로 “전기적 연결”을 의미하지 않기 때문입니다.

현상 자체는 VIA 주변에 GND 영역이 시각적으로 존재하고, VIA도 Top과 Bottom을 모두 관통하는 형태로 배치되어 있어 사용자는 이미 전기적으로 연결되어 있다고 생각할 수 있습니다. 하지만 KiCad의 DRC 엔진은 이 연결을 Net 기반의 논리 연결 여부로 판단합니다. 즉, VIA의 Net 설정이 정확하게 GND로 되어 있고, GND fill 영역 역시 정확히 같은 Net에 해당하며, 그 두 구성 요소가 실제 전기적으로 연결되는 조건(예: 충분한 접촉면적, 동일 Net, 유효한 Zone Refill)을 만족해야만 연결로 간주됩니다.

이러한 오류가 주로 발생하는 원인은 크게 두 가지입니다. 첫 번째는 Zone Fill이 최신 상태가 아니라는 점입니다. KiCad에서는 레이아웃 변경 후 Zone Fill을 수동 또는 자동으로 갱신해주어야 하며, VIA를 추가하거나 GND 트랙을 수정한 경우에도 Refill을 통해 Net 연결이 재정의되어야 합니다. 만약 “Refill all zones before performing DRC” 옵션이 꺼져 있거나, 마지막으로 Fill을 한 이후에 VIA를 추가했다면 DRC 시점에서 VIA는 아직 GND 영역에 전기적으로 연결되어 있지 않은 상태로 인식됩니다. 이럴 경우, 겉으로는 fill 안에 VIA가 포함되어 있더라도 논리 연결은 되지 않았기 때문에 DRC에서는 연결되지 않은 VIA로 판단합니다.

두 번째 원인은 VIA 자체가 GND Net으로 지정되어 있지 않거나, GND Zone과의 Net 명칭이 불일치하는 경우입니다. VIA를 삽입할 때 의도한 GND 트랙 위가 아닌 공백 영역에 삽입했거나, 트랙 위에 배치했더라도 간혹 KiCad가 VIA의 Net 정보를 자동으로 인식하지 못하는 경우가 있습니다. 이때 VIA의 Net 정보는 “(none)” 또는 “Net-(X)”처럼 표시되며, 이는 GND fill과 논리적으로 연결되어 있지 않은 것으로 간주됩니다. 마찬가지로 GND Zone이 잘못된 Net에 설정되어 있을 경우, VIA가 GND Net을 가지고 있어도 연결로 인정되지 않습니다.

이러한 문제를 해결하기 위해선, 먼저 Zone Fill을 반드시 업데이트해야 합니다. 방법은 두 가지가 있으며, 하나는 메뉴에서 “Inspect → Design Rules Checker”를 실행할 때 “Refill all zones before DRC” 옵션을 체크하고 실행하는 것이고, 다른 하나는 평소 레이아웃 수정 후 B 단축키를 눌러 직접 zone을 수동으로 refill하는 것입니다. 두 방식 모두 동일하게 동작하며, 이 과정을 통해 GND fill이 새롭게 정의되고 VIA가 그 영역 내에서 논리적으로 포함되는지 여부가 판단됩니다.

다음으로 VIA의 Net 속성을 반드시 확인해야 합니다. VIA를 클릭하거나 마우스를 가져다 대면 우측 속성 창에서 Net 이름을 확인할 수 있습니다. 이 값이 “GND”로 명확하게 설정되어 있어야 합니다. 만약 GND가 아닌 다른 이름이거나 공란으로 되어 있다면, 이는 GND와 논리적으로 연결되지 않은 것으로 판단되며 DRC 오류가 발생합니다. 이 경우 VIA를 삭제하고, 확실히 GND 트랙 또는 GND pad 상에서 VIA를 다시 삽입하는 것이 가장 확실한 방법입니다.

또한, GND Zone 설정도 확인이 필요합니다. GND fill을 클릭한 뒤 E 키를 눌러 속성 창을 열면, 해당 zone이 어떤 Net에 연결되어 있는지가 명시되어 있습니다. 이 값이 “GND”로 지정되어 있지 않다면, VIA가 GND Net을 가지고 있더라도 연결되지 않으며, 이는 결국 DRC에서 “VIA 연결 오류”로 이어지게 됩니다. zone 설정이 올바르게 되어 있는지, fill 범위가 실제로 VIA와 접촉하고 있는지도 반드시 확인해야 합니다.

추가적으로는, VIA가 zone과 너무 가까운 외곽이나 설계 규칙 상의 clearance 때문에 실질적인 도통이 이루어지지 않는 경우도 있으므로, 가능하면 VIA를 zone 내부 중심부로 이동시키는 것이 좋습니다. 그리고 DRC에서 annular ring 관련 오류도 함께 발생한 것으로 보이는데, 이는 pad 또는 VIA의 금속 테두리 너비가 설계 규칙에서 요구하는 최소치보다 좁다는 의미이므로, 해당 pad 또는 via의 drill size와 annular ring 크기도 함께 검토해보시는 것이 바람직합니다.

결론적으로, 이 오류는 단순한 시각적인 문제라기보다는 Zone Fill의 상태, VIA의 Net 연결, 그리고 Net 간의 논리적 일치 여부를 모두 확인해야만 해결할 수 있는 구조적인 문제입니다. 상기 과정을 점검하시면 본 오류는 무리 없이 해결되며, 이후에도 동일한 문제가 발생할 경우에는 Refill 및 Net 속성 확인을 루틴화하시는 것이 좋습니다.

우선 결론부터 말씀드리자면, Earth Ground는 회로 내의 Signal Ground(GND)와는 목적과 성격이 다르기 때문에, 충분히 별도의 Power Plane 또는 Zone으로 분리하여 사용하는 것이 가능합니다. 실제로 고주파 회로나 전력 노이즈에 민감한 시스템, 또는 외부 환경으로부터 전기적 노이즈가 유입될 가능성이 있는 장비에서는 Earth Ground를 별도로 구성하는 것이 일반적입니다. 이는 단순한 전기적 연결을 넘어서 시스템의 EMC(전자파 적합성), 안전성, 신호 무결성 확보와도 깊은 관련이 있습니다.

회로 설계에서 우리가 흔히 말하는 GND는 일반적으로 회로 내부의 참조 전위, 즉 0V 기준점으로 사용되는 Signal Ground입니다. 반면 Earth Ground는 외부 세계, 즉 접지극이나 금속 케이스와 같은 기계적 구조물에 연결되어 ESD(정전기)나 서지(surge)와 같은 외부 전기적 스트레스로부터 회로를 보호하기 위한 용도로 사용됩니다. 따라서 이 둘은 전기적으로 완전히 동일한 접점으로 간주해서는 안 됩니다.

실제 PCB Artwork 단계에서는 Earth Ground를 하나의 독립된 Net으로 정의하여 Power Plane 혹은 Zone으로 따로 구성할 수 있으며, 이때 중요한 점은 GND와 Earth Ground 간의 연결 방식입니다. 대부분의 경우, 이 두 영역은 직접적인 금속 연결보다는 RC 필터, TVS 다이오드, 0Ω Jumper, 혹은 공통 모드 초크(Common Mode Choke) 등을 통해 제한적이고 제어된 경로로만 연결됩니다. 이러한 연결 방식은 회로 내부의 Ground Loop 형성을 방지하고, 외부에서 유입되는 고속 노이즈를 효과적으로 차단하는 데 기여합니다.

예를 들어, 디지털 시스템의 케이스가 금속으로 구성되어 있고, 사용자와의 접촉이 빈번한 구조라면 케이스는 Earth Ground로 처리하여 ESD를 직접 흘려보내도록 하고, 내부 디지털 GND는 회로 동작 기준 전위로서 별도로 유지합니다. 이때 두 Ground는 RC 회로나 다이오드 등을 통해 일부 연결하되, 주파수 응답 특성을 조절함으로써 불필요한 고주파 노이즈의 유입을 방지합니다.

KiCad나 Altium Designer 같은 툴에서는 이러한 Ground를 별도의 Net으로 정의할 수 있으며, Zone 설정 시에도 Net 명칭을 구분하여 Earth GND와 Signal GND가 명확히 분리되도록 구성하는 것이 중요합니다. 이때 DRC(Design Rule Check) 상에서도 Net 간의 연결 여부나 적절한 VIA 설정이 되어 있지 않다면 오류가 발생할 수 있으므로, 각 Net의 속성, Zone의 연결 대상, 그리고 VIA의 위치와 Net 할당 정보를 꼼꼼히 확인해야 합니다.

정리하자면, Earth Ground는 Signal Ground와 전기적으로 분리할 수 있으며, 회로의 안전성 확보, EMC 대응, 그리고 노이즈 차단을 위한 설계 전략의 일환으로 충분히 독립된 Power Plane이나 Zone으로 운용할 수 있습니다. 다만 그 연결 방식은 반드시 목적에 맞게 설계되어야 하며, 자칫 Ground Loop나 불필요한 전류 흐름을 유발하지 않도록 구조적 설계와 시뮬레이션, 그리고 DRC 상의 확인 절차가 수반되어야 합니다.

답변 부분 확인하였습니다. 감사합니다.

말씀 주신 내용 중에 궁금한 점은 Earth ground는 외부로 부터 들어온 ESD나 Surge를 대비하고 EMC 이슈를 위한 것으로 이해했습니다.

예를 들어주신 내용 중에 디지털 시스템의 금속이 외부와 접촉시 심하다면 Earth ground 처리를 통해, ESD에 방지하지만 일부 Path를 통해 Signal ground와의 제한적 path 형성이라는 내용이 있습니다. 외부 세계/Signal의 ground를 왜 서로 연결해주는 지를 이해하지 못했습니다. 오히려 외부 세계와의 ground 연결로 인해, ESD의 Return path가 발생하여 디지털 signal에 영향을 줄 것으로 생각이 듭니다.

혹시 제가 잘못 이해하고 있는 걸까여?

질문 내용 중 제가 설명이 부족했던 부분이 있다면, 제가 다시 작성하도록 하겠습니다.

감사합니다.

1. Signal Ground와 Earth Ground를 '완전히' 분리하면 생기는 문제

이론적으로 Signal Ground와 Earth Ground를 완전히 절연시키면, 외부에서 유입된 ESD나 Surge 전류는 Earth Ground를 통해 빠져나가지만, 회로 내부로 이어지는 전류 경로가 불완전해질 수 있습니다. 이는 곧 전류의 ‘귀환 경로(Return Path)’ 부재를 의미하며, 전기적 노이즈가 차폐되지 않거나 오히려 우회 경로를 타고 Signal 영역으로 유입되는 문제를 유발할 수 있습니다.

즉, ESD 전류가 케이스(GND_SHIELD) → Earth Ground로 빠져나가면서, 그와 함께 흐르는 전자기장이 Signal GND가 지나가는 전송선이나 PCB 내의 다른 도선을 따라 간섭 전류(coupled current)로 작용할 수 있습니다. 이는 곧 시스템의 오동작, 데이터 오류, 또는 회로 손상을 초래할 수 있습니다.

2. 제한적 연결의 목적: EMC 대응과 전위차 해소

따라서 대부분의 EMC 설계에서는 Earth Ground와 Signal Ground 사이를 직접 단락(short)하는 것이 아니라, 제어된 방식으로 연결합니다. 이 연결은 다음과 같은 목적을 갖습니다:

전위차 해소: Signal GND와 Earth GND 사이의 전위차가 커지면 순간적으로 Ground loop가 형성되거나, 회로 전체가 ‘공중에 떠 있는(Ground floating)’ 상태가 됩니다. 이를 방지하기 위해 RC회로나 TVS 다이오드, 공통 모드 초크 등을 사용하여 직류는 차단하고, 고주파 노이즈만 우회시킬 수 있는 형태의 연결을 구성합니다.

귀환 경로 확보: 외부로부터 유입된 ESD 전류는 금속 케이스를 통해 들어온 뒤, PCB 내부의 신호선이나 전원선으로 전달되기 전에, Signal GND로 흘러갈 수 있는 안정된 방전 경로를 제공해야 합니다. 이때 RC 회로나 0Ω Jumper 등을 이용해 저주파 영역에서는 차단하고 고속 전류만 빠르게 우회할 수 있도록 설계합니다.

차폐 극대화: EMC 관점에서는 케이스를 Earth Ground에만 연결하는 것보다, Signal GND와도 고주파에서만 연결시킴으로써 Shielding 역할을 극대화할 수 있습니다. 특히 고속 디지털 신호가 있는 시스템에서는 케이블 실드와 Signal GND 사이에 1~10nF의 캐패시터를 넣는 방식이 자주 사용됩니다.

3. 실제 설계 예시: USB 포트 설계에서의 GND 연결

USB 회로나 Ethernet 회로를 예로 들면, 대부분의 USB 커넥터에는 Shield(GND_SHELL)가 있고 이는 시스템 케이스나 외부 세계의 Earth Ground와 연결됩니다. 하지만 이 Shield가 내부 Signal GND와 완전히 분리되어 있으면, 다음과 같은 문제가 생깁니다:

케이블을 연결할 때 발생하는 차폐 불균형으로 ESD가 Signal 선을 타고 들어올 수 있음

외부 장비와 전위차가 클 경우, 접촉 시 큰 Surge가 내부 회로로 유입될 수 있음

이를 방지하기 위해 보통은 10~100nF 커패시터나 공통모드 초크를 이용해 GND와 GND_SHELL을 AC적으로만 연결합니다. 이는 고주파 노이즈는 바이패스시키되, DC 전류는 차단하여 회로를 보호하는 효과가 있습니다.

따라서 말씀하신 “ESD Return Path가 생겨 디지털 Signal에 영향을 줄 수 있다”는 우려는 일정 부분 타당하지만, 바로 그렇기 때문에의도적이고 제어된 연결 방식이 필요하다는 것이 핵심입니다.

다시 말해, 문제는 연결 자체가 아니라, 무분별하고 통제되지 않은 ‘직접 연결’입니다. 설계자는 이 두 Ground 간을 절연하거나 단락하는 것이 아니라, Surge 전류나 고주파 노이즈가 Signal 영역으로 들어오지 않도록 제한적이고 방향성 있는 우회 경로를 제공해야 합니다. 이를 위해 RC, 다이오드, CM Choke, 캐패시터 등의 설계 기법을 사용하는 것이지요.

0

안녕하세요, 인프런 AI 인턴입니다. Edened님.

PCB DRC(Design Rule Check) 오류는 발생하는 원인을 정확히 파악하고 해결하는 것이 중요합니다. 질문하신 내용에 따라 다음과 같은 몇 가지 검토 사항을 제안드립니다:

VIA 연결 체크:

- VIA가 제대로 설정되어 있는지 확인하십시오. 특히, 보드 레이어(특히 Power/GND Plane)를 연결하는 경우, 설정이 될 수 있습니다. VIA가 명확히 GND와 연결되어 있는지, GND 폴리곤이 VIA의 열 접점을 감싸고 있는지 점검해보세요.

- VIA가 제대로 설정되어 있는지 확인하십시오. 특히, 보드 레이어(특히 Power/GND Plane)를 연결하는 경우, 설정이 될 수 있습니다. VIA가 명확히 GND와 연결되어 있는지, GND 폴리곤이 VIA의 열 접점을 감싸고 있는지 점검해보세요.

DRC 설정 확인:

- PCB 디자인 소프트웨어의 DRC 설정에서

Power Plane과 관련된 조건을 확인해보세요. 지원되는 DRC에서의 VIA 및 Power Plane 접속 설정은 일반적으로 특정한 규칙을 따르기도 합니다.

- PCB 디자인 소프트웨어의 DRC 설정에서

Polygons 및 Planes:

- GND Plane에 문제가 있을 수 있습니다. 폴리곤이 올바르게 생성되어 있고, GND Net과 VIA의 접속 부분이 끊기지 않았는지 확인하세요. 오토 리필(auto refill) 기능을 사용해 보시는 것도 도움이 될 수 있습니다.

- GND Plane에 문제가 있을 수 있습니다. 폴리곤이 올바르게 생성되어 있고, GND Net과 VIA의 접속 부분이 끊기지 않았는지 확인하세요. 오토 리필(auto refill) 기능을 사용해 보시는 것도 도움이 될 수 있습니다.

DRC 규칙 조정:

- DRC 오류가 발생하는 VIA 주변의 특정 영역은 종종 추가적인 패드나 라인 때문일 수 있습니다. 이 경우 DRC 규칙을 수정하여 더 넓은 allowance(여유)을 줄 수도 있습니다.

- DRC 오류가 발생하는 VIA 주변의 특정 영역은 종종 추가적인 패드나 라인 때문일 수 있습니다. 이 경우 DRC 규칙을 수정하여 더 넓은 allowance(여유)을 줄 수도 있습니다.

소프트웨어 복합 오류 재확인:

- DRC-Proof 기능으로 재확인해보십시오. 강의를 통해 지식공유자가 권장한 기본 설정이 적용되었는지 확인해 주시면 유용합니다.

- DRC-Proof 기능으로 재확인해보십시오. 강의를 통해 지식공유자가 권장한 기본 설정이 적용되었는지 확인해 주시면 유용합니다.

아래는 유사한 문제의 해결 방법에 대한 관련 질문 링크입니다:

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

안녕하세요 삼코치님, 해당 오류는 제가 따로 zone을 설정을 하지 않아서 발생했습니다. 각각의 오류들에 대해서 설명해주셔서 감사합니다.

추가적으로 Earth ground는 Power plane을 나누었던 것처럼 ground로 나누면 되는지 궁금해서 질문 남깁니다.

감사합니다.