ERC Error 문의

안녕하세요 삼코치님

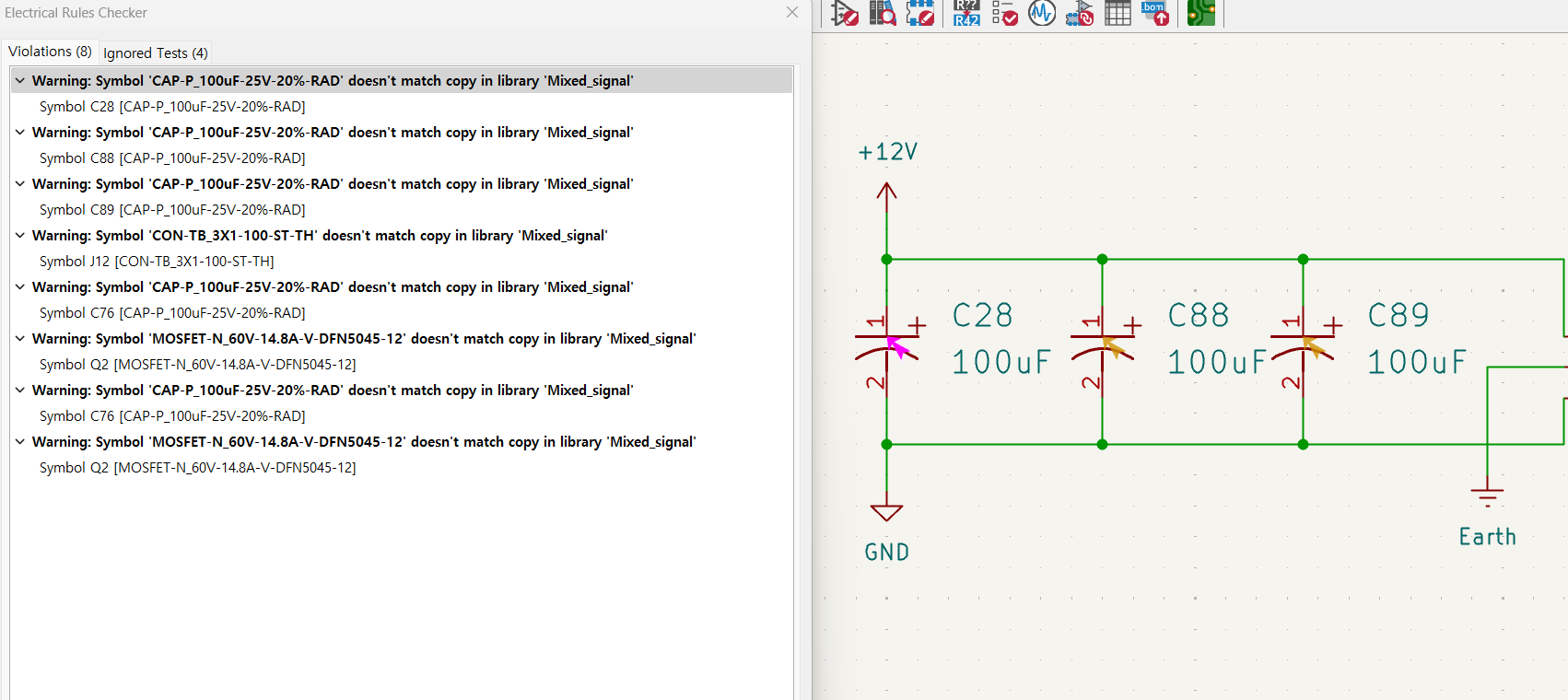

최종 schematic 완성하여 ERC 진행 후 문의 사항이 생겨 질문 남깁니다.

해당 Error 사항을 waive해도 되는지 궁금해서 자료 첨부드립니다. 현재 Error 내용에서 가리키는 소자들은 모두 symbol을 불러와서 rounting까지 마친 상태입니다.

감사합니다.

답변 2

0

안녕하세요. 최종 회로를 완성하고 ERC까지 점검하신 단계에서 이와 같은 질문을 주신 것은 설계 흐름을 체계적으로 관리하고 계시다는 증거로, 아주 바람직한 접근입니다.

지금 발생한 ERC 경고 메시지들의 공통적인 내용은 "doesn't match copy in library 'Mixed_signal'"이라는 문구로, 이는 회로도 내에서 사용된 심벌(Symbol)이 현재 참조 중인 라이브러리 상의 심벌 정의와 일치하지 않는다는 경고입니다. 쉽게 말해, 회로도에 배치된 부품의 로컬 사본(캐시된 심벌)과, 원래 라이브러리 상의 정의 간에 일부 속성(예: 핀 타입, 필드 정보, 모양 등)에 차이가 있다는 뜻입니다.

이러한 경고는 전기적 연결이나 동작상의 오류가 아니라, 데이터 정합성 관점의 경고에 해당합니다. 따라서 실제로 해당 부품들이 올바른 핀 번호와 핀 기능(예: 전원 핀, 입력, 출력 등)을 가지고 있고, 회로도상에서도 전기적으로 정확하게 연결되어 있다면, 이 경고는 기능적인 문제가 아니며 무시해도 됩니다. 특히 라이브러리에서 부품 심벌이 수정되었거나, 프로젝트 시작 이후 외부 라이브러리가 업데이트된 경우 이러한 mismatch 경고가 자주 발생합니다.

실무적으로는 두 가지 선택지가 있습니다. 첫째, 현재 회로도에 있는 심벌 정의가 실제 부품 스펙과 일치하고, 전기적 검증이나 netlist 생성, PCB 전이 과정에 문제가 없다면 이 경고는 Waive 처리하거나 'Ignored Tests'로 분류해도 무방합니다. 둘째, 보다 깔끔한 프로젝트 관리를 원하신다면, 라이브러리와 회로도 간의 심벌 정보를 동기화시킬 수 있습니다. 이 경우, 심벌 편집기나 회로 편집기 상에서 "Update from Library" 기능을 통해 원본 라이브러리 정보를 강제로 반영할 수 있으며, 반대로 현재 회로도에 정의된 심벌을 로컬 라이브러리로 복사하여 독립적으로 관리하는 방식도 있습니다. 후자의 방식은 프로젝트 단위로 라이브러리의 안정성을 확보할 수 있어 팀 단위 협업이나 릴리즈 버전 관리 측면에서도 유리합니다.

결론적으로, 현재 보고 계신 경고 메시지는 명백한 오류(error)가 아니며, 기능적인 오작동이나 회로상 문제를 의미하지 않습니다. 회로의 동작 논리가 정상이고, pin-to-pin 연결이 의도대로 설계되어 있다면 무시하셔도 되고, 필요에 따라 심벌 동기화나 로컬화 관리 전략을 선택하시면 됩니다. 다만 이와 같은 경고가 반복적으로 발생하는 경우에는 프로젝트 라이브러리 구조를 한 번 점검하시고, 캐시 심벌을 정리하거나 별도 로컬 라이브러리를 구성해 사용하는 방식을 권장드립니다.

0

안녕하세요, 인프런 AI 인턴입니다. Edened님, 질문 주셔서 감사합니다.

ERC(Electrical Rules Check)는 PCB 설계에서 중요한 단계로, 회로 설계의 전기적 연결을 점검하고 잠재적인 오류를 사전에 발견할 수 있도록 돕습니다. 현재 질문자님께서 보내주신 스냅샷에서 몇 가지 경고가 발생하는 이유와 처리 방안을 정리해보겠습니다.

ERC 경고에 대한 설명 및 처리 방안

라이브러리 불일치 경고:

- “does not match” 경고는 라이브러리와 사용 중인 부품 심볼 간의 불일치를 나타냅니다. 이는 실제로는 기능에 큰 영향을 주지 않을 수 있습니다만, 장기적으로는 관리의 용이성을 위해 라이브러리에서 업데이트된 심볼을 사용하여 동기화하는 것이 좋습니다. 하지만, 설계가 이미 승인된 상태라면, ERC 상의 경고를 무시하고 진행할 수도 있습니다.

- “does not match” 경고는 라이브러리와 사용 중인 부품 심볼 간의 불일치를 나타냅니다. 이는 실제로는 기능에 큰 영향을 주지 않을 수 있습니다만, 장기적으로는 관리의 용이성을 위해 라이브러리에서 업데이트된 심볼을 사용하여 동기화하는 것이 좋습니다. 하지만, 설계가 이미 승인된 상태라면, ERC 상의 경고를 무시하고 진행할 수도 있습니다.

심볼과의 일치 문제:

- 경고가 된 부품들이 실제 회로에서 올바르게 동작할 것으로 보인다면, 이 경고는 일시적으로 무시할 수 있지만, 확대 해석을 통해 설계 변경 시 속성을 다시 검토해 보는 것이 좋습니다.

- 경고가 된 부품들이 실제 회로에서 올바르게 동작할 것으로 보인다면, 이 경고는 일시적으로 무시할 수 있지만, 확대 해석을 통해 설계 변경 시 속성을 다시 검토해 보는 것이 좋습니다.

경고 무시(waive):

- 경고를 무시하거나 “waive” 옵션을 선택할 수 있지만, 이는 잠재적인 오류가 있는 경우 문제를 야기할 수 있습니다. 단기적으로 프로젝트를 완료하는 데는 지장이 없을 수 있지만, 중요 시스템이나 민감한 회로에서는 보다 면밀한 검토가 필요할 수 있습니다.

- 경고를 무시하거나 “waive” 옵션을 선택할 수 있지만, 이는 잠재적인 오류가 있는 경우 문제를 야기할 수 있습니다. 단기적으로 프로젝트를 완료하는 데는 지장이 없을 수 있지만, 중요 시스템이나 민감한 회로에서는 보다 면밀한 검토가 필요할 수 있습니다.

강의 자료나 프로젝트 전반에 대해 더 명확한 확인이 필요하시거나, 설계 오류로 인한 하드웨어 문제를 방지하려면 관련 기능이나 유사한 사례를 다루었던 다른 게시물 링크를 참조해 보실 것을 추천합니다.

참고 자료 및 링크

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

수강연장

0

19

2

강의수강 만료일 연장 신청

0

30

2

강의 질문

0

60

2

RJ45 library 누락

0

45

2

강의 만료 확인 요청

0

47

2

JTAG 통신 질문

0

56

1

GND 오류

0

61

2

프로젝트 주제

0

69

1

45강 UART, TTL 질문

0

70

1

발열에 의한 LDO의 드롭아웃 전압 상승

0

80

2

I2C 통신 방식

0

107

2

라우팅 질문

0

62

2

kicad 라이브러리 추가 방법

0

244

2

VIa에 GND 항목이 없습니다.

0

71

2

디버거를 디버깅하려면

0

92

2

강의 연장

0

98

2

via 관련 질문드립니다.

0

64

1

32강 ERC에러

0

73

1

페라이트 비드 관련 질문드립니다.

0

97

2

알티움(Altium) 실습 자료 공유 가능 여부 문의드립니다.

0

114

2

핀 방향 설정 관련 질문드립니다

0

68

1

32강 debugging pin 설계 강의 관련 질문 드립니다.

0

65

1

kicad ERC footprint library 경고

0

86

2

과제 수행과정에 있어서 질문드립니다.

0

91

1