인프런 커뮤니티 질문&답변

질문0623 : BGR 따라 설계하기

해결된 질문

작성

·

447

·

수정됨

0

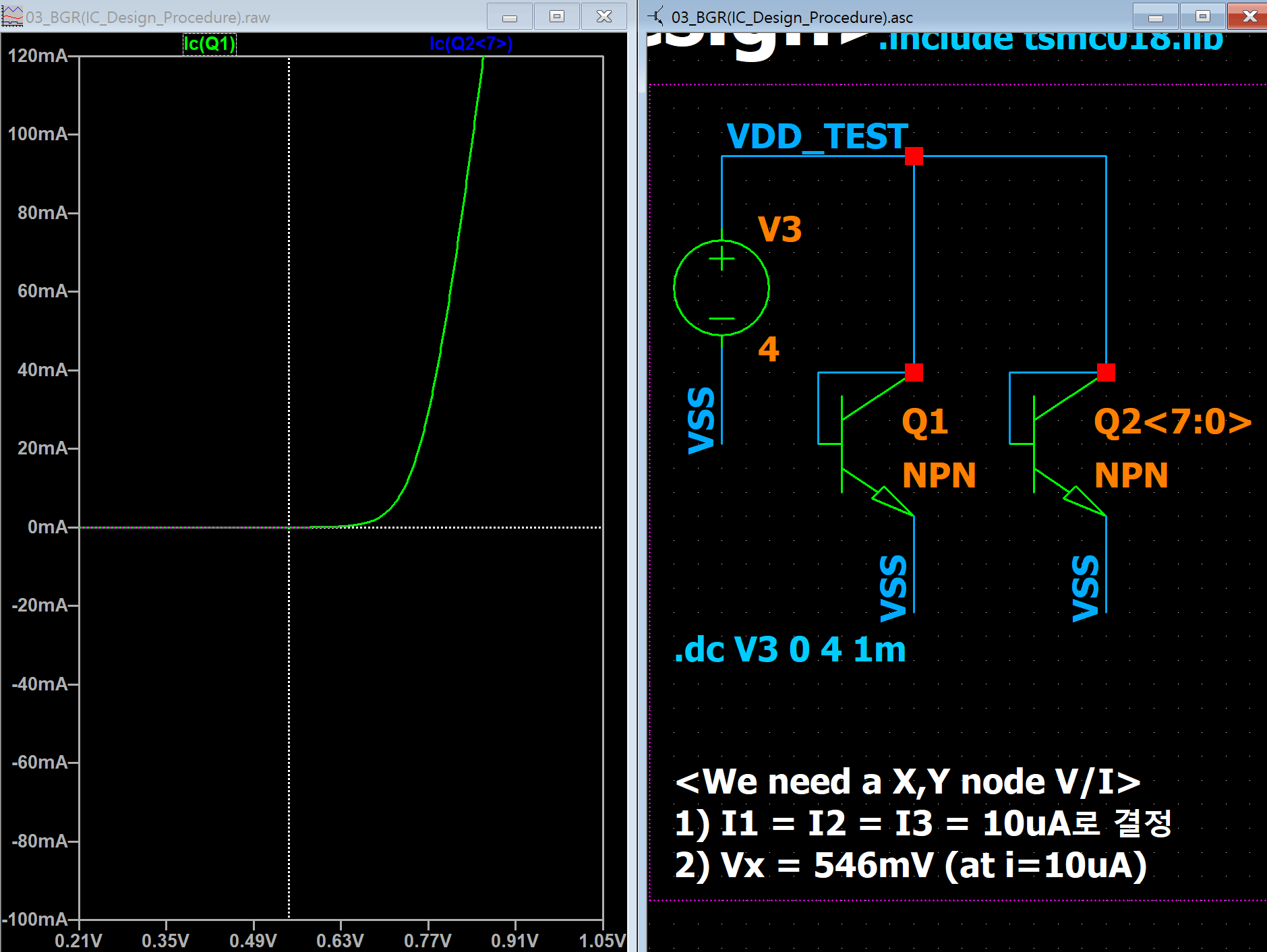

1) 강의를 참고하여 10uA를 흘리기 위한 X 노드 전압(Vx)을 계산하고 있는데, 제가 구한 값과 차이가 커서 어떤 부분이 잘못됐는지 잘 모르겠습니다.

삼코치님은 Vx를 약 613mV로 두셨고, 이 경우 R이 약 14kΩ로 계산되는데, 저는 Vx 값이 다르게 나와서 R이 약 5.7kΩ로 잡히는 상황입니다. 혹시 어떤 부분을 다시 확인해봐야 할지 조언해주실 수 있을까요?

2) BJT Layout 시 Common Centroid 방식으로 구성한다고 하셨는데요, 왜 BJT가 총 10개로 구성된 것인지 궁금합니다. 일반적으로 1:7:1 비율로 배치해야 Common Centroid가 성립하지 않을까 생각합니다.

3) Nmos 바디를 gnd로 하지않는 이유도 궁금합니다. (바디이펙트, 공정)

4) self biasing 회로에서 전류 오차 0.01uA정도 생겨, 아래 X, Y 쪽 전류는 오차가 0.8uA까지 증가합니다. 따라서 Vx, Vy도 오차가 2mV정도 차이가 나는데 상관없는지 궁금합니다

5) 갑자기 궁금한 부분인데, 이러한 BGR는 ip마다 들어가나요 아니면 chip 하나에 1개인가요??

감사합니다

퀴즈

아날로그 회로에서 Bandgap Reference (BGR)의 주된 역할은?

전압 강하를 줄여 전력 효율을 높인다.

온도와 공급 전압 변동에도 일정한 기준 전압을 제공한다.

디지털 신호의 전압 레벨을 변환한다.

고주파 클럭 신호를 생성한다.

답변 2

0

안녕하세요. 좋은 질문 주셔서 감사합니다.

질문하신 내용을 하나하나 짚어가며 설명드리겠습니다.

우선 첫 번째로, Vx 전압값에 차이가 나는 부분은 아주 핵심적인 고민입니다. 제가 강의에서 제시한 Vx ≒ 613mV는 특정한 조건(공정 모델, 온도, BJT 파라미터 등)에서 얻어진 기준값입니다. 하지만 여러분이 직접 시뮬레이션하실 때 사용하는 라이브러리 버전이나 모델 파일, 시뮬레이션 조건(예: 온도 설정, 모델의 IS, β 등)이 다르다면 당연히 다른 V_BE 전압값이 나올 수 있습니다. 중요한 건 Vx 자체의 절대값이 아니라, 그 전압에서 정확히 10μA가 흐르는 조건을 만족하는가입니다. 만약 Vx = 546mV에서 Ic = 10μA라면, 그것이 그 환경에서는 정확한 기준이 되는 것입니다. 그 값에 따라 저항을 설계하시면 됩니다. 오히려 이걸 통해 BJT의 파라미터가 결과에 얼마나 영향을 주는지 감각을 익히는 것이 더 중요합니다.

-> 그리고 ltspice 버전 차이로 인해서 다른 수강생분들도 동일한 현상이 있어서 이 부분도 그럴 수 있습니다.

두 번째로, BJT를 왜 10개로 구성했는가에 대한 질문도 매우 좋은 포인트입니다. 일반적으로 Bandgap Reference 회로에서는 Q1:Q2를 1:8의 면적비로 설계하게 됩니다. 그런데 단순히 트랜지스터 1개와 8개를 나란히 배치하면, 공정의 gradient(도핑 농도 변화, 식각 편차 등)로 인해 mismatch가 발생합니다. 이를 보정하기 위한 대표적인 기법이 바로 Common Centroid 배열입니다. 예를 들어 ‘1-2-4-2-1’이라는 대칭 구조를 사용하면, 중심 기준으로 좌우가 대칭이 되기 때문에 위치에 따른 오차가 상쇄되는 효과를 얻을 수 있습니다. 이 구조를 쓰기 위해 총 10개의 셀을 사용하게 되는 것이죠. 실제 아날로그 레이아웃에서는 이러한 미묘한 기생요소에 대한 감각이 매우 중요하기 때문에, 단순히 면적 비뿐만 아니라 배치 구조에도 신경을 쓰셔야 합니다.

세 번째 질문은 NMOS 바디를 왜 GND에 묶지 않았는가 하는 내용인데요, 이는 공정 특성에 따라 다릅니다. 일반적으로는 NMOS의 바디(P-well)를 GND에 연결하지만, Triple-well이나 Deep N-well 공정을 사용하는 경우, 바디를 isolation 시켜서 다른 바이어스를 줄 수 있습니다. 이런 방식은 아날로그 회로에서 매우 유용한데, 노이즈 isolation이나 바디 이펙트 제어, threshold 조정 등이 가능해지기 때문입니다. 예를 들어, Bandgap에서 생성한 기준 전압을 다른 회로로 안정적으로 전달하기 위해서는, 바디를 GND에 단단히 묶는 것보다 isolation을 주고 바이어스를 조정하는 것이 유리할 때가 많습니다.

네 번째로 self-biasing 구조에서 전류 오차와 그에 따른 전압 오차는 실무적으로도 흔히 발생하는 현상입니다. 말씀하신 것처럼 전류 오차가 0.01μA밖에 안 되더라도, 그 오차가 mirror를 타고 전파되면서 다음 노드에서는 0.8μA까지 커질 수 있습니다. 전압으로 환산하면 수 mV 차이가 나겠죠. 하지만 Bandgap 회로의 본질은 온도 보상이 정확히 이루어지는가, Vref가 안정적으로 나오는가이지, 노드 간 전류나 전압의 절대 오차가 몇 uA/mV 나느냐가 아닙니다. ±2mV 정도의 차이는 BGR 구조 설계에서는 충분히 허용 가능한 범위이며, 실리콘 레벨에서도 보정 없이 만족하는 수준입니다. 고정밀도를 요구하는 경우에는 trim bit을 활용하거나, layout matching을 더 정교하게 조정해서 개선할 수 있습니다.

마지막 질문은 실무에서 많이들 궁금해하시는 부분인데요, BGR 회로는 칩마다 1개만 존재하는 게 일반적입니다. 전압 기준 소스로서 칩의 모든 IP 블록에 레퍼런스를 제공하는 역할을 하기 때문에, 전체 회로의 '기준점'이 되는 하나의 BGR을 중심으로 bias current와 reference voltage가 분배됩니다. 다만, 고정밀 ADC나 노이즈 민감한 RF 회로처럼 별도 isolation이 필요한 경우에는 로컬 기준 회로를 별도로 갖거나, 공유된 Vref에 버퍼를 달아서 안정도를 보강하기도 합니다. 즉, IP마다 BGR을 따로 갖는 구조는 아니고, 하나의 중심 BGR에서 다수의 IP로 분기해 나가는 구조가 기본입니다.

0

안녕하세요, 인프런 AI 인턴입니다. han님.

현재 질문하신 내용은 DC 스윕 시뮬레이션과 관련된 문제로 보입니다. LTspice에서 설정값에 따라서 시뮬레이션 결과가 다르게 나오는 것은 회로 구성이나 설정에 따라 발생할 수 있는 일반적인 문제입니다.

특히 여러분이 공유해주신 아날로그 회로 설계 실무에서 BGR 회로 설계 관련하여, 특정 전류 조건에서의 특정 노드 전압 설정이 중요한데, 이 부분에서 혼란이 있으신 것 같습니다.

문제점과 관련하여 고려해 볼 수 있는 몇 가지 사항은 다음과 같습니다:

컴포넌트 값 확인:

- 회로 내의 모든 소자 값(저항, 트랜지스터) 등이 강의에서 설명된 값과 동일한지 다시 한번 체크해 보시기 바랍니다.

- 회로 내의 모든 소자 값(저항, 트랜지스터) 등이 강의에서 설명된 값과 동일한지 다시 한번 체크해 보시기 바랍니다.

모델 파라미터 검토:

- 사용하신 트랜지스터 모델 및 파라미터가 정확한지를 확인해야 합니다. 모델 파일 내 정의가 다르거나 오류가 있을 수 있습니다.

- 사용하신 트랜지스터 모델 및 파라미터가 정확한지를 확인해야 합니다. 모델 파일 내 정의가 다르거나 오류가 있을 수 있습니다.

시뮬레이션 설정:

.dc커맨드와.step커맨드를 사용하는 경우, 범위와 단계 값을 꼭 확인하세요. 그래프가 세부 사항을 포함하여 올바르게 설정되어 있는지 확인하세요.

시뮬레이션 환경 설정:

- LTspice 설정 중

Netlist옵션이나 다른 환경 설정이 잘못되어 있을 수도 있습니다. 예를 들면, 시뮬레이션 토폴로지나 전류 방향에 주의가 필요합니다.

- LTspice 설정 중

강의 내용 재검토:

- 삼코치님의 강의 내용 중 중요한 부분들을 다시 확인해 보시고, 제공된 자료나 링크에서 관련 설명을 체크해 보시면 도움이 됩니다.

- 삼코치님의 강의 내용 중 중요한 부분들을 다시 확인해 보시고, 제공된 자료나 링크에서 관련 설명을 체크해 보시면 도움이 됩니다.

아래 유사한 질문 및 해결 방법 관련 링크를 공유드립니다:

- BGR 설계의 Low-voltage Reference 개선 관련 질문 및 답변

- LTspice 시뮬레이션에서 발생할 수 있는 일반적인 문제 해결 방법

이러한 단계를 통해 문제를 해결하시길 바랍니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

답변 감사합니다 !!!!