테스트 벤치에 질문이 있습니다.

안녕하세요 덕분에 AXI4에 대해 많이 배웠고 또 검증하는데 있어서 많은 경험을 쌓았습니다.

40장 영상을 토대로 맛비님께서 알려주신 빌드의 형식이 아닌, block design 형태로 만들어서 좀더 직관성 있게 만들어보고자 시도 중에 있습니다. (차후 다른 커스텀ip를 불러와 파라미터를 block쪽에서 수정 및 재활용)

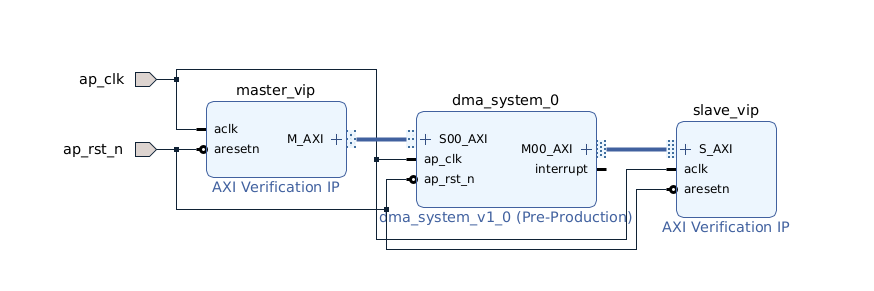

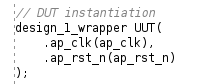

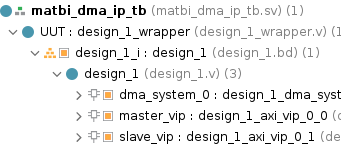

따라서 블럭 디자인은 다음과 같고 최상위 TB의 인스턴스 및 ctrl, m00_axi 경로 수정을 해주었습니다.

따라서 블럭 디자인은 다음과 같고 최상위 TB의 인스턴스 및 ctrl, m00_axi 경로 수정을 해주었습니다.

(사용하지않는 인스턴스 및 wire 삭제)

(사용하지않는 인스턴스 및 wire 삭제)

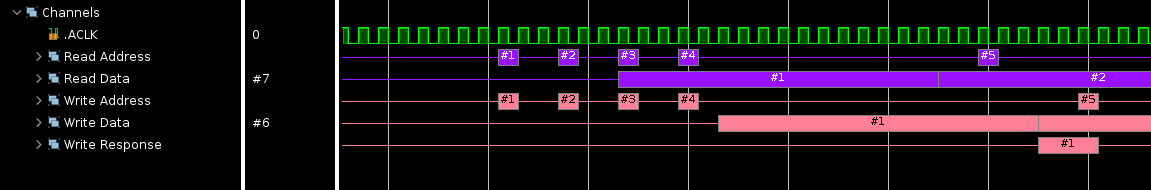

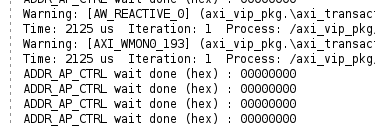

결과적으로 말씀드리면 기존과 동일한 결과값을 보이며 마지막 에러또한 뜨지않아 정상적이라 생각합니다.

하지만 Tcl Console 창에서 경고가 대량으로 발생하였는데 아마 Cache Value 문제라 생각됩니다.

Warning: [AW_REACTIVE_0] (axi_vip_pkg.\axi_transaction::set_cache ) 1935000 ns : Attempted to send CACHE(0x0000) when SUPPORTS_NARROW is low. According to UG1037,AxCACHE[1] has to be 1 to ensure that any downstream upsizer can fully pack data up to wider widths Time: 1935 us Iteration: 1 Process: /axi_vip_pkg/axi_slv_wr_driver(C_AXI_WDATA_WIDTH=64,C_AXI_RDATA_WIDTH=64,C_AXI_WID_WIDTH=1,C_AXI_RID_WIDTH=1,C_AXI_AWUSER_WIDTH=1,C_AXI_WUSER_WIDTH=1,C_AXI_BUSER_WIDTH=1,C_AXI_ARUSER_WIDTH=1,C_AXI_RUSER_WIDTH=1,C_AXI_SUPPORTS_NARROW=0)::get_and_drive/GET_AND_DRIVE Scope: axi_vip_pkg.\axi_transaction::set_cache File: /tools/Xilinx/Vivado/2023.1/data/xilinx_vip/hdl/axi_vip_pkg.sv Line: 2909올라간 코드에서는 Cache Value는 형식상 있을뿐 사용하지않는걸로 알고있는데

혹시 저러한 경고문을 접해본 경험이 있으신가요?

터무니없는 질문 봐주셔서 감사합니다..

답변 2

1

아이고 자문자답 죄송합니다

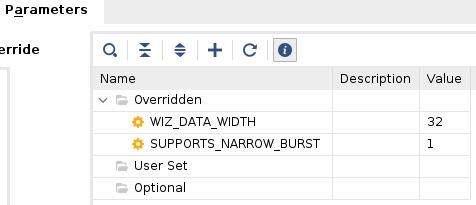

dma ip 제작할때 마스터 인터페이스 파라미터에 Narrow를 1로 안바꾸고 있었네요.

바꾸니까 경고없이 잘됩니다. 앞으로 질문할때 더 많은걸 고려해보고 올리겠습니다. 죄송합니다.

[HDL 32장-2부] 참고 링크 관련

1

38

2

[HDL 22장] F/F CE 관련 질문

1

47

2

13강에 언급된 강의 내용 질문

1

62

2

22장 vaild/ready

1

99

1

output, reg 선언

1

82

3

gvim

1

65

1

fifo의 stall과 퍼포먼스 드랍

1

60

2

Design Valid I/F

1

75

2

valid/ready 스트림 구조 관련 질문이 있습니다!

1

93

2

IDLE state의 시점관련

1

65

2

skid buffer의 handshake 방향이 반대로 되어 있는 이유

1

110

3

[wdma] AWLEN_w의 값이 1일 경우 r_burst_cnt_w와 AWLEN_w의 async 인한 bready 발행X 이슈?

1

72

2

system verilog 사용이유.

1

133

2

AXI_VIP 사용 시 glitch 발생

1

96

1

왜 배속이 안되요?

1

115

2

다이어그램 이해

1

74

2

27.[프로젝트-1] Mem copy IP를 FPGA에 올려보기

1

76

2

27.[프로젝트-1] Mem copy IP를 FPGA에 올려보기

1

91

3

[HDL 38장: RDMA 코드 실습편] MOR fifo에서 "ARLEN_r" 존재의 이유가 궁금합니다

1

115

2

[HDL 35장 AXI-Stream I/F 실습편] sync_fifo 사용 이유

1

130

1

예외처리 관련 질문

1

79

2

AXI의 ID의 역할은?

1

191

2

28장 강의 AXI 이론편관련질문

0

113

1

37장 Data bit width 질문

1

60

2