Pipeline에서 질문

`timescale 1ns / 1ps

module power_of_8(

input clk,

input reset_n,

input i_valid,

input [31:0] i_value,

output o_valid,

output [63:0] o_power_of_8

);

/////// Type ////////

reg [2:0] r_valid;

reg [63:0] r_power_of_2;

reg [63:0] r_power_of_4;

reg [63:0] r_power_of_8;

wire [63:0] power_of_2;

wire [63:0] power_of_4;

wire [63:0] power_of_8;

// flow of valid

always @(posedge clk or negedge reset_n) begin

if(!reset_n) begin

r_valid <= 3'd0;

end else begin

r_valid <= {r_valid[1:0], i_valid};

end

end

// data buffer (f/f)

always @(posedge clk or negedge reset_n) begin

if(!reset_n) begin

r_power_of_2 <= 64'd0;

r_power_of_4 <= 64'd0;

r_power_of_8 <= 64'd0;

end else begin

r_power_of_2 <= power_of_2;

r_power_of_4 <= power_of_4;

r_power_of_8 <= power_of_8;

end

end

// Power Operation

assign power_of_2 = i_value * i_value;

assign power_of_4 = r_power_of_2 * r_power_of_2;

assign power_of_8 = r_power_of_4 * r_power_of_4;

assign o_valid = r_valid[2];

assign o_power_of_8 = r_power_of_8;

endmodule

==================================== 테스트벤치 ==============================

`timescale 1ns / 1ps

module tb_power_of_8;

reg clk , reset_n;

reg i_valid;

reg [31:0] i_value;

wire o_valid;

wire [63:0] o_power_of_8;

// clk gen

always

#5 clk = ~clk;

integer i;

integer fd;

initial begin

//initialize value

$display("initialize value [%d]", $time);

reset_n = 1;

clk = 0;

i_valid = 0;

i_value = 0;

fd = $fopen("rtl_v.txt","w");

// reset_n gen

$display("Reset! [%d]", $time);

# 10

reset_n = 0;

# 10

reset_n = 1;

# 10

@(posedge clk);

$display("Start! [%d]", $time);

for(i=0; i<100; i = i+1) begin

@(negedge clk);

i_valid = 1;

i_value = i;

@(posedge clk);

end

@(negedge clk);

i_valid = 0;

i_value = 0;

# 500

$display("Finish! [%d]", $time);

$fclose(fd);

$finish;

end

// file write

always @(posedge clk) begin

if(o_valid) begin

$fwrite(fd,"result = %0d\n", o_power_of_8);

end

end

// Call DUT

power_of_8 u_power_of_8(

.clk (clk),

.reset_n (reset_n),

.i_valid (i_valid),

.i_value (i_value),

.o_valid (o_valid),

.o_power_of_8 (o_power_of_8)

);

endmodule

위 코드는 맛비님이 주신 코드입니다(테스트벤치에서는 #숫자만 바꾸고 나머지는 동일합니다)

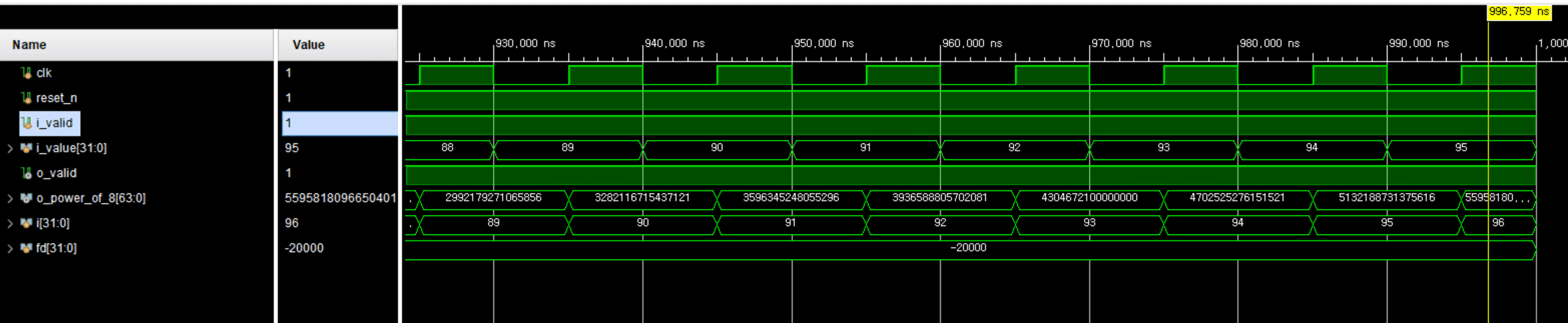

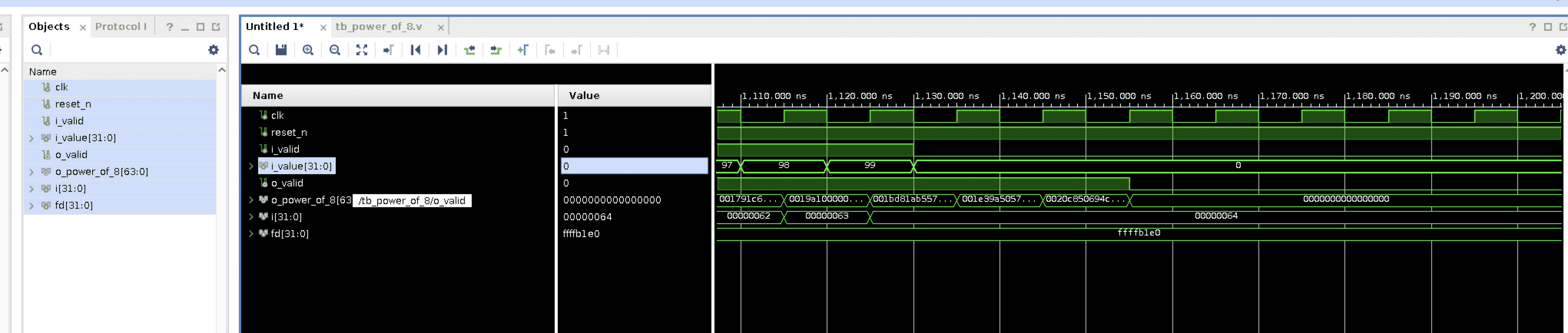

해당 코드를 vivado에서 돌리면

아래와 같이 i_valid와 i 의 값이 99까지 나오지 않습니다

제가 아무리 테스트벤치에서 # 숫자를 조작해도 맛비님이 보여주신 것처럼 i가 99까지 돌지를 않는데 왜 그런지 궁금합니다

테스트벤치에서 # 숫자를 조작하지 않고 맛비님이 주신 오리지날 코드로 돌렸을 때는 i가 88에서 그래프가 멈췄습니다

답변 1

1

테스트벤치에서 # 숫자를 조작하지 않고 맛비님이 주신 오리지날 코드로 돌렸을 때는 i가 88에서 그래프가 멈췄습니다

제가 드린 코드가 99 까지 나오지 않는 다는 뜻인가요?

저는 나오는데, 처음부터 받아서 확인해보세요 :)

latency 개념 구현

1

84

3

비바도 all os버전

1

67

2

초기화를 reset_n 이 '1'일 때가 아닌 '0' 일 때 실행시키는 이유 질문

1

68

2

다운로드용량

1

68

2

비바도리눅스설치

1

79

2

전체path복사넣기

1

59

2

Vivado 2025.2 리눅스 설치 후 실행 에러와 솔루션 (libxv_commontasks.so)

1

142

2

explorer.exe오류

1

99

3

mobaxterm설치오류

1

84

2

./build시, waveform 'divide color' 사용

1

51

2

Latch와 관련하여 (Time borrowing, Latch-based design)

1

122

2

clean 명령어가 안되는데, 따로 저장해줘야 하는지 궁금합니다.

0

57

1

안녕하세요 설치 관련 질문 드립니다.

1

60

3

16장 mealy 설계.

1

71

2

14장 Cycle 관련, Testbench 코드.

1

63

2

21강(16장) 초기값 설정이 적용되는 시점 질문

1

59

1

20강(15장) - 밀리 머신 관련하여 질문 드립니다.

1

63

2

build에러 질문

0

54

2

1장 ./build에서 에러가 나요

1

70

2

FPGA 강의 보드 문의 드립니다.

1

104

2

5장 DFF특성에 대한 질문

1

73

3

vivado linux 사용 이유.

1

134

2

메모리의 형태가 전체설계에 미치는 영향이 궁금합니다.

1

102

2

디스코드 멤버쉽 등업 관련 문제

1

91

2