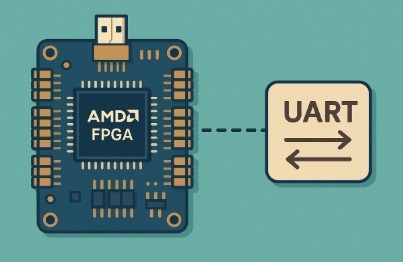

Implementing UART on FPGA

EasyFPGA

UART is the most basic and widely utilized serial communication method, making it a very suitable learning topic for beginners new to FPGA design. In this course, we will thoroughly understand the communication principles and frame structure of UART, and based on this, we will proceed with directly implementing transmit/receive logic through RTL (Register Transfer Level) design. By implementing UART on an FPGA, you can systematically develop your digital circuit design skills and gain experience verifying its operation at the actual hardware level through simulation and verification. Furthermore, by learning the method utilizing the MicroBlaze soft processor and Xilinx UART IP, you will gain a broad understanding of processor-based system design flow and interface configuration. This will enable you to acquire comprehensive development capabilities encompassing both logic design and processor design.

초급

FPGA, system-verilog, uart