Basic Design Synthesis Training (디지털 회로설계 구현)

MetaEncore

₩330,000

입문 / EDA, digital-logic, vlsi, soc, asic

5.0

(6)

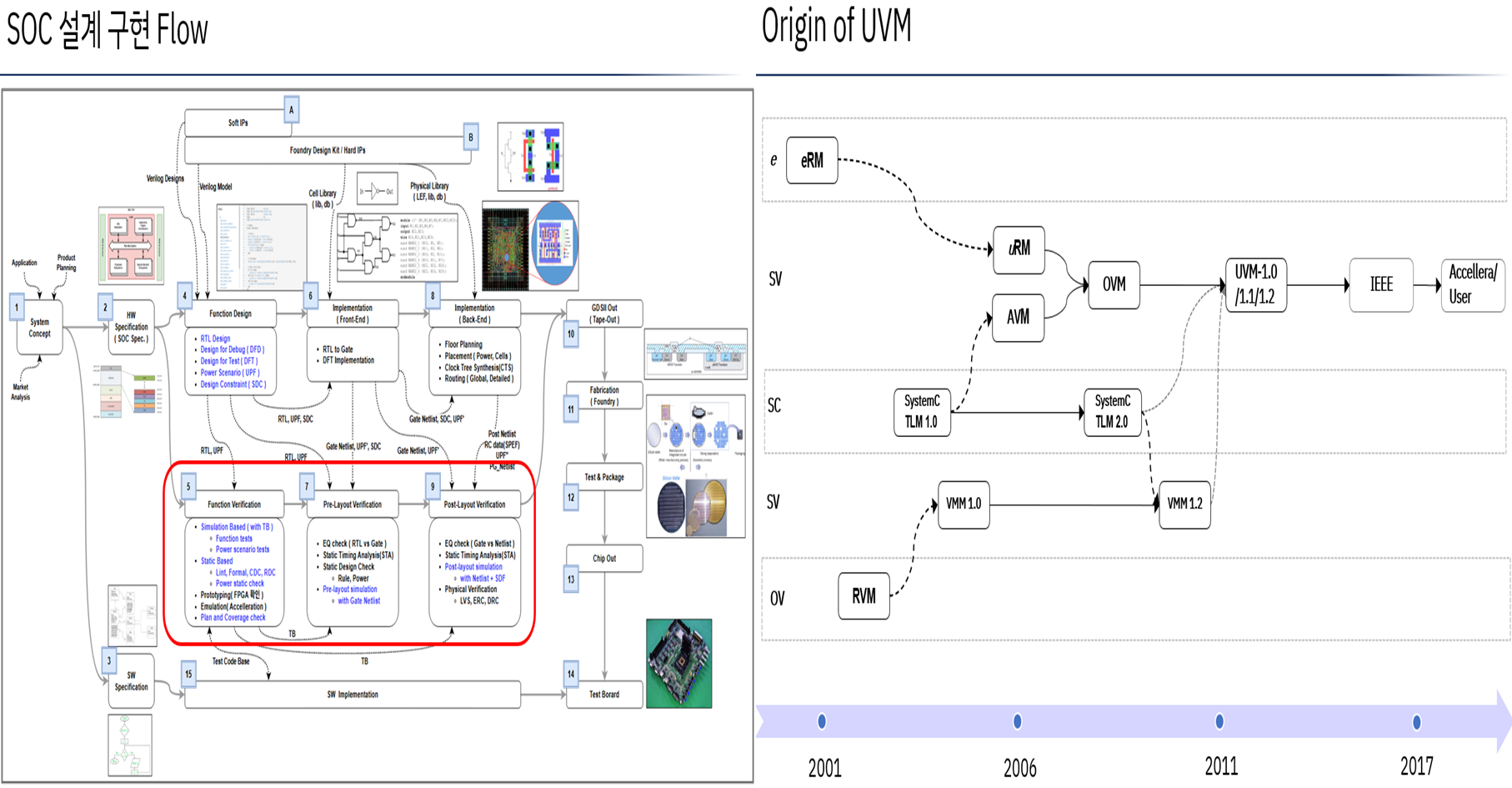

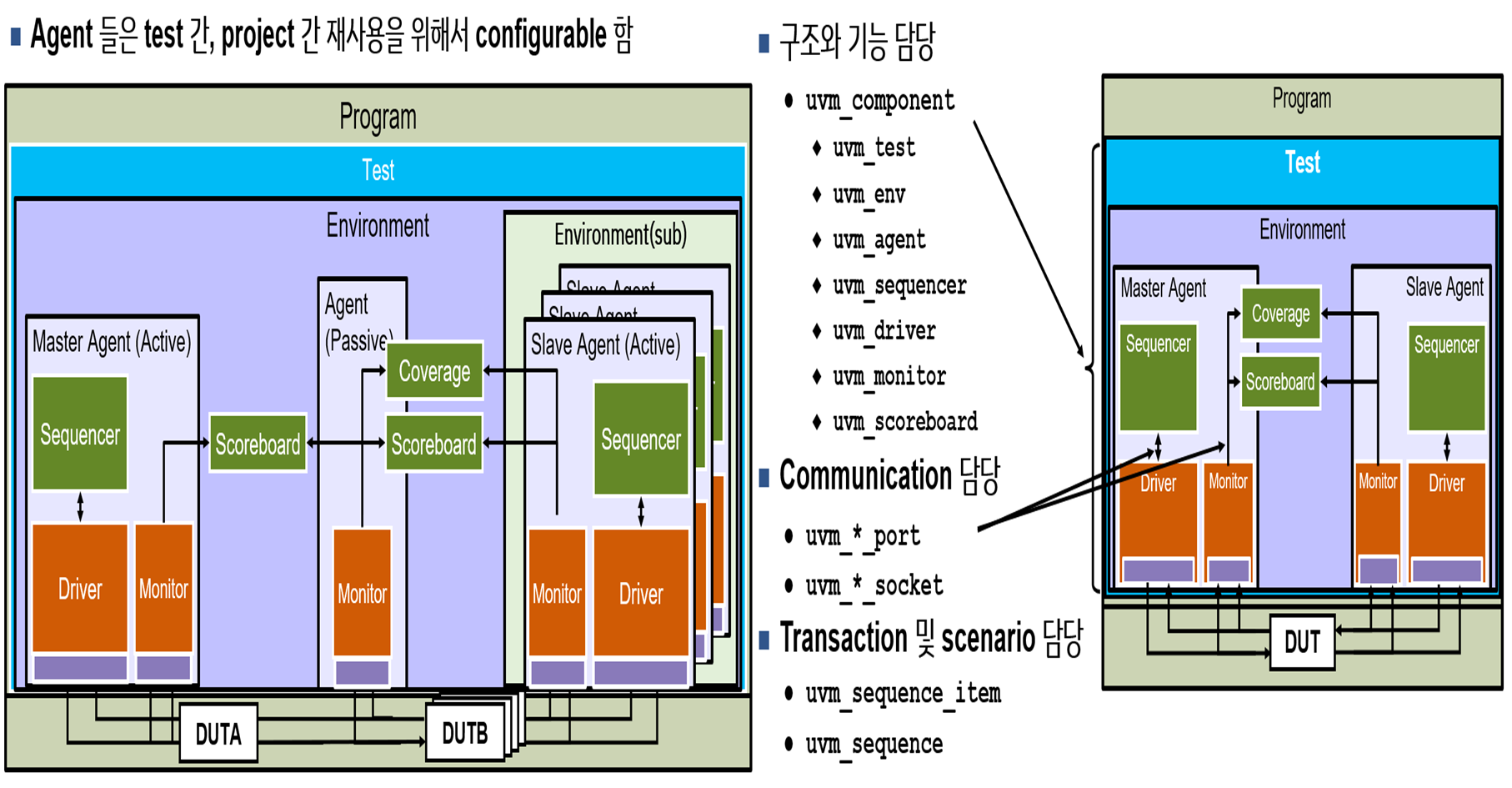

반도체 칩은 어떤 단계를 거쳐 설계되고 제조될까요? PI(Physical Implementation) /PD(Physical Design) 직무에서 필요한 논리회로의 기본개념들과 Chip Design Flow에 대해서 한 step씩 살펴보고 현업에서 디지털 칩 회로설계에 사용하는 tool을 기반으로 합성 과정의 주요 개념에 대해서 살펴봅니다.

입문

EDA, digital-logic, vlsi