11장 카운터 실습 코드에 대한 질문입니다.

300

작성한 질문수 2

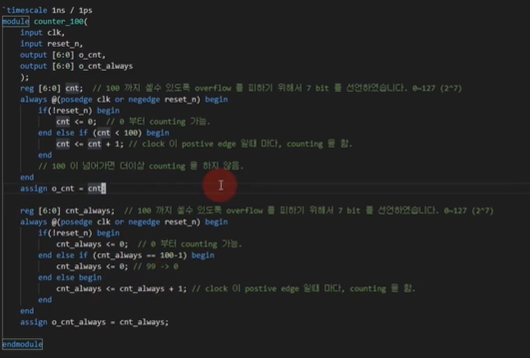

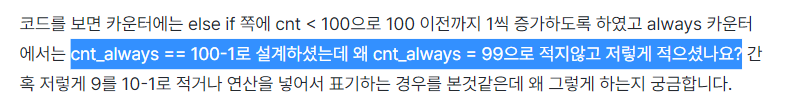

코드를 보면 카운터에는 else if 쪽에 cnt < 100으로 100 이전까지 1씩 증가하도록 하였고 always 카운터에서는 cnt_always == 100-1로 설계하셨는데 왜 cnt_always = 99으로 적지않고 저렇게 적으셨나요? 간혹 저렇게 9를 10-1로 적거나 연산을 넣어서 표기하는 경우를 본것같은데 왜 그렇게 하는지 궁금합니다.

답변 1

0

안녕하세요 :)

cnt < 100 은 100이 넘어가면, 더 이상 counting 을 하지 않습니다.

cnt_always == 100-1; // 99 와 같죠.

이거는 0으로 초기화를 통해서 다시 counting 을 합니다. clock 이 인가되는 한 계속 counting 을 하죠.

그래서 "always" 라는 surfix 를 붙였어요.

결론 : 교육용 코드이고요.

counting value 를 초기화를 해야 계속 counting 이 된다를 보여드리고 싶었어요. (그 이상 그 이하의 이유는 없습니다.)

======================================

합성기 입장에서는 (100-1) 이나, 99 이나 같은 결과로 인지합니다. (상수이기 때문에)

합성기 입장에서는 (100-1) 이나, 99 이나 같은 결과로 인지합니다. (상수이기 때문에)

간혹 멍청한? 합성기는 100-1 을 minus 로직을 넣는 경우가 있을 수 있습니다,, 만 (제가 현업에서 사용하는 상용 tool 에서는 본적은 없습니다.)

100 - 1 이면, 100개를 counting 하려고 하는구나 라는 설계자가 (제 입장) 인지하기 쉽게 하기 위함입니다. (이 또한 그 이상 그 이하의 이유는 없습니다.)

결론 : 코드를 인지하시기 편한 방법을 쓰시면 됩니다.

즐공하세요 :)

latency 개념 구현

1

87

3

비바도 all os버전

1

72

2

초기화를 reset_n 이 '1'일 때가 아닌 '0' 일 때 실행시키는 이유 질문

1

71

2

다운로드용량

1

71

2

비바도리눅스설치

1

80

2

전체path복사넣기

1

63

2

Vivado 2025.2 리눅스 설치 후 실행 에러와 솔루션 (libxv_commontasks.so)

1

149

2

explorer.exe오류

1

106

3

mobaxterm설치오류

1

90

2

./build시, waveform 'divide color' 사용

1

57

2

Latch와 관련하여 (Time borrowing, Latch-based design)

1

130

2

clean 명령어가 안되는데, 따로 저장해줘야 하는지 궁금합니다.

0

63

1

안녕하세요 설치 관련 질문 드립니다.

1

64

3

16장 mealy 설계.

1

74

2

14장 Cycle 관련, Testbench 코드.

1

64

2

21강(16장) 초기값 설정이 적용되는 시점 질문

1

60

1

20강(15장) - 밀리 머신 관련하여 질문 드립니다.

1

68

2

build에러 질문

0

57

2

1장 ./build에서 에러가 나요

1

73

2

FPGA 강의 보드 문의 드립니다.

1

107

2

5장 DFF특성에 대한 질문

1

77

3

vivado linux 사용 이유.

1

137

2

메모리의 형태가 전체설계에 미치는 영향이 궁금합니다.

1

104

2

디스코드 멤버쉽 등업 관련 문제

1

92

2