인프런 커뮤니티 질문&답변

FIFO read sequence waveform 관련 문의

해결된 질문

작성

·

82

0

안녕하세요, 공유해주신 FIFO verilog tb 관련하여 문의 드립니다.

read transaction (task fifo_rd) 에서

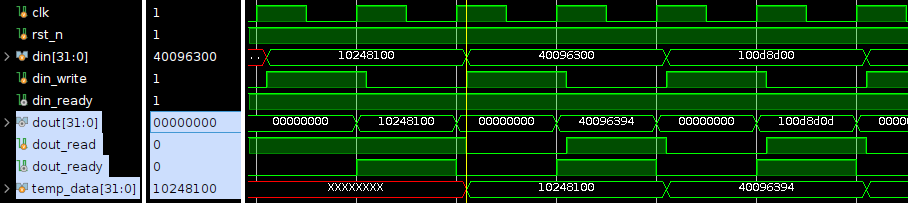

temp_data = dout; 동작과 dout_read = 0;의 동작이 같은 시간대에서 진행되고 있습니다.

코드 상에서는 temp_data = dout; 이후에 #(input_delay) 만큼 시간이 지난 후에

dout_read = 0;이 되는 것으로 이해했는데, 이런 경우는 compile 과정에서 문제가 있는 것인지 궁금합니다.

답변 2

0

wwa9981 님,

코드를 보시면 @(posedge clk) 에서 2개의 operation이 이루어 지고

현재 VCS로 실행하시는 경우에 input_delay = 0 으로 되어 있어서 동일한 시간대로 보이는 것이 맞습니다.

어디에 공유된 것을 말씀하시는지 그 부분도 알려 주시면 좀 더 자세히 확인해 볼 수 있을 것 같습니다.

안녕하세요, 답변 주셔서 감사합니다.

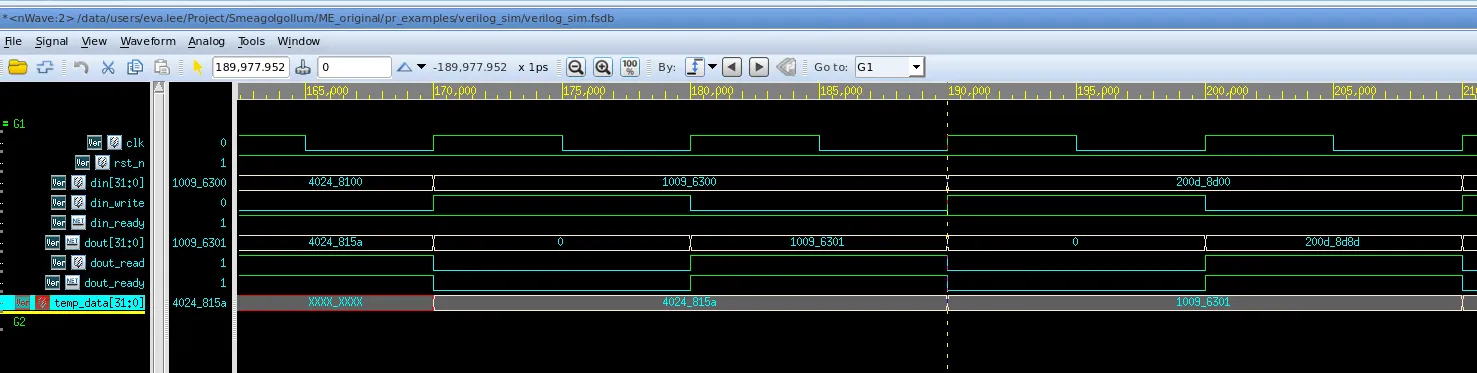

현재는 WSL을 통해 제 pc에서 linux 환경으로 vivado를 사용하고 있습니다.

예제 및 미션 DB 압축 해제한 파일에서 하기 경로의 코드입니다.

.../pr_examples/verilog_tb/tb_verilog.v

vivado run에 따라 VCS를 define하지 않으므로, input_delay가 1입니다.

1) posedge clk에 맞춰 temp_data = dout;

2) 이후 input_delay에 맞춰 dout_read = 0;

위 순서대로 진행이 되는 게 정상인데, 실제로는 temp_data = dout의 수행이

posedge clk에 맞춰서 되는 게 아니라 input_delay를 먹어서 dout_read = 0과 같이 수행되고 있는 것처럼 보입니다. 이러한 현상이 발생하는 이유를 잘 모르겠습니다.

wwa9981 님,

네, 생각하신 부분이 맞습니다. 코드상으로는 말씀하신 대로 동작해야 합니다.

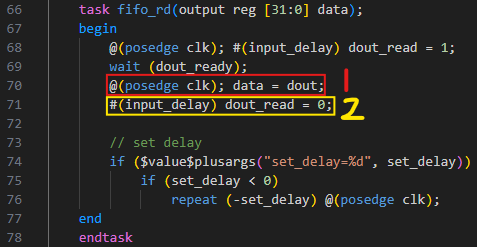

문제는 task fifo_rd 에 전달되는 argument 때문입니다.

output 으로 전달된 temp_data 는 task가 끝날 때 copy가 되어서 전달됩니다.

그래서 input_delay가 적용된 이후에 temp_data 로 data가 copy가 되기 때문입니다.

그래서 fifo_rd의 argument를 저희가 원하는 대로 동작하도록 하려면, output이 아니라 ref로 해야 합니다. 본 강의의 task/function 부분을 참조해 주세요.

아래와 같이 수정해서 돌려보시면 됩니다.

저희가 예제를 조금 더 신중히 만들었어야 했는데요. 수정해야 겠네요.

task fifo_rd(ref reg [31:0] data);

begin

@(posedge clk); #(input_delay) dout_read = 1;

wait (dout_ready);

@(posedge clk) data = dout;

#(input_delay) dout_read = 0;

// set delay

if ($value$plusargs("set_delay=%d", set_delay))

if (set_delay < 0)

repeat (-set_delay) @(posedge clk);

end

endtask0

안녕하세요, 인프런 AI 인턴입니다.

님께서 문의 주신 FIFO Verilog Testbench의 read transaction 관련 내용에 대해 설명드리겠습니다.

디지털 회로 시뮬레이션에서 발생할 수 있는 이러한 동작은 가끔 컴파일러의 최적화나 race condition에 의해 발생할 수 있습니다. 주어진 로직에서 signal의 업데이트가 의도한 대로 시간이 지연된 후 발생하기 위해서는 몇 가지 사항을 고려해야 합니다.

데이터 전개 및 지연:

temp_data = dout;와dout_read = 0;두 명령이 순차적으로 이루어지도록 time delay를 명확하게 설정해야 합니다. 즉,temp_data에dout을 전개한 후 일정 간격을 두고dout_read값을 변경하는 방식인데, 이를 위한#(input_delay)설정이 중요합니다.Scheduler와의 상호작용: RTL 시뮬레이터가 일정한 시뮬레이션 시간표를 사용한다면, 명령 간의 발생 순서가 기대와 다를 수 있습니다. 이는 특정 컴파일 옵션이나 시간 설정에 의해 무시될 수도 있으며, 이러한 경우 고정된 시간 지연을 사용하는 것이 중요합니다.

Waveform 확인: 시뮬레이션 결과로 생성된 waveform을 통해 signal 간의 올바른 시퀀스를 관찰할 수 있습니다. 문제의 로그나 시뮬레이션 결과를 통해 코드가 의도한 대로 동작하지 않는다면, RTL 코드의 순서와 timing을 다시 확인하여야 합니다.

컴파일러 최적화: 컴파일러의 최적화가 문제를 일으킬 수 있으므로, 최적화 옵션을 낮추거나 debug 모드에서 테스트해보는 것도 도움이 될 수 있습니다.

관련 과제에서 명확하지 않은 부분이나 추가적인 정보를 위해 해당 강의 페이지에서 제공하거나 참고할만한 문서를 통해 자세한 내용을 확인하는 것도 좋은 방법입니다. 만약 이러한 조치 후에도 문제가 발생한다면, 지금 시점에서 waveform 분석을 통해 원인을 파악하는 것이 좋습니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 재현 환경 링크를 추천해드립니다. 현재 베타 기능으로 방해가 됐다면 양해를 부탁드리며, 추가로 궁금한 사항은 언제든 질문해 주세요. 곧 지식공유자께서 더욱 자세한 답변을 드릴 것입니다. 🙏

관련 질문 URL: SystemVerilog Testbench에서 요소들의 시간 동기화 문제 해결

wwa9981 님,

혹시 현재 어떤 simulator로 진행하신 건지요?

사용하신 환경을 공유해 주시거나, EDAPlayground 에서 공유해 주실 수 있으실까요?