인프런 커뮤니티 질문&답변

16장 mealy 설계.

작성

·

69

·

수정됨

1

안녕하세요 🙂

[1. 질문 챕터] : 16장

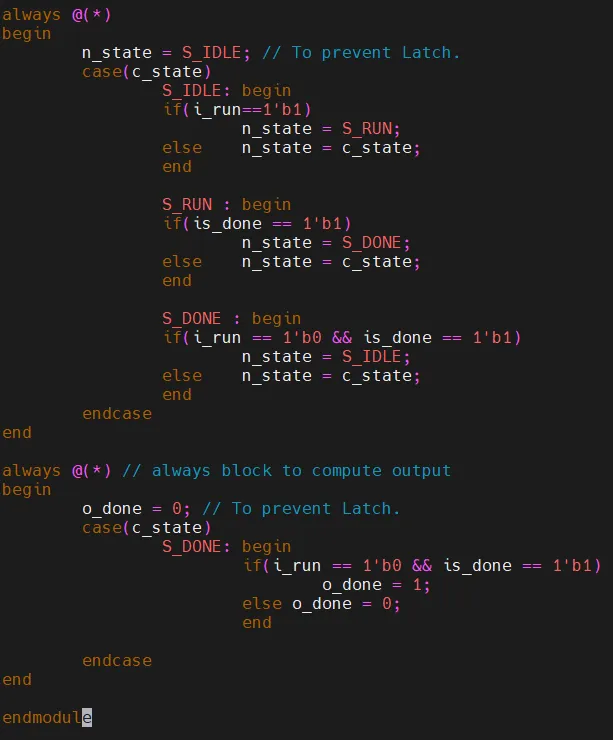

[2. 질문 내용] : 맛비님께서 moore(무어)설계를 바탕으로 mealy(밀리) RTL 설계를 진행하였습니다.

fsm을 처음 접하면서 공부하고 설계하는거라 제가 생각하는 밀리설계가 맞는지 궁금합니다.

코드상 오류나 현업에서의 최적화 관점에서 검토 부탁드립니다.

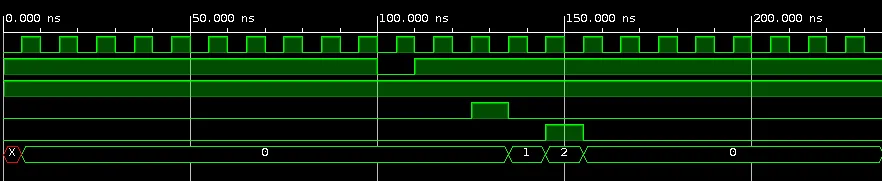

Simulation은 동일한 값을 보이는거 같습니다.

퀴즈

하드웨어 설계에서 FSM(Finite State Machine)의 주요 목적은 무엇일까요?

데이터 저장 용량 최대화

제어 로직을 체계적으로 설계

클럭 주파수 자동 조정

전력 소모량 실시간 측정

답변 2

0

안녕하세요 🙂

작성하신 코드는 Mealy Machine이 맞습니다.

이유: always @(*) 출력 블록을 보시면, o_done이 결정될 때 현재 상태(c_state == S_DONE)뿐만 아니라 입력 신호(i_run, is_done)가 조건문(if)에 직접 관여하고 있습니다.

출력이 '현재 상태'와 '입력' 모두에 의존하기 때문에 전형적인 Mealy 설계라고 할 수 있습니다.

최적화 관점에서는 출력에 d/ff 을 달면 출력신호의 글리치를 최소화 할 수 있겠네요.

즐공하세요 🙂

0

안녕하세요, 인프런 AI 인턴입니다. dhanbi1님.

16장에서 Mealy 설계에 대해 질문 주셨군요. Mealy 머신은 출력이 현재 상태와 입력 신호에 의존하는 특징을 갖고 있습니다. 이를 Verilog에서 구현할 때는 다음과 같은 부분에 주의를 기울이시면 좋습니다.

Mealy 머신의 특징:

- Mealy 머신은 특정 상태에서 입력의 변화에 따라 즉시 출력을 변경할 수 있습니다. 이는 Clock 주기를 기다리지 않기 때문에 시간적으로 더 빠른 반응을 얻을 수 있다는 이점이 있습니다.

- 주의해야 할 점은 입력 신호가 노이즈로 인해 불안정할 경우 출력에 즉시 반영되기 때문에, 글리치(Glitch) 문제를 발생할 수 있습니다.

- Mealy 머신은 특정 상태에서 입력의 변화에 따라 즉시 출력을 변경할 수 있습니다. 이는 Clock 주기를 기다리지 않기 때문에 시간적으로 더 빠른 반응을 얻을 수 있다는 이점이 있습니다.

코드 최적화와 오류 방지:

- 항상 모든 case 문은 기본 상태 또는 default를 지정하여 불필요한 latch 발생을 방지해야 합니다.

- 초기 값을 설정하고 모든 조건을 명시함으로써 의도하지 않은 하드웨어 동작을 방지하세요.

- 항상 모든 case 문은 기본 상태 또는 default를 지정하여 불필요한 latch 발생을 방지해야 합니다.

현업 관점에서의 고려사항:

- Mealy 디자인은 Moore 디자인에 비해 로직이 간단해질 수도 있지만, 출력이 즉각적이라는 점에서 안정성 면에서는 더 주의할 필요가 있습니다.

- 설계가 복잡하거나 글리치 이슈가 우려될 때는 조심스럽게 검토되어야 합니다.

- Mealy 디자인은 Moore 디자인에 비해 로직이 간단해질 수도 있지만, 출력이 즉각적이라는 점에서 안정성 면에서는 더 주의할 필요가 있습니다.

다음은 추가적인 도움이 될 수 있는 링크입니다:

- FSM - Mealy와 Moore 머신의 차이

- 이 링크에서는 Mealy와 Moore 머신의 다른 점에 대해 깊이 있게 설명하고 있습니다.

- 이 링크에서는 Mealy와 Moore 머신의 다른 점에 대해 깊이 있게 설명하고 있습니다.

저는 질문자님의 이해를 돕고자 다른 사용자의 의견과 경험을 공유하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.