인프런 커뮤니티 질문&답변

Motor Driver Schematic 질문

해결된 질문

작성

·

53

·

수정됨

0

SP/SN 신호에 Rsense 연결 관련하여 질문드립니다.

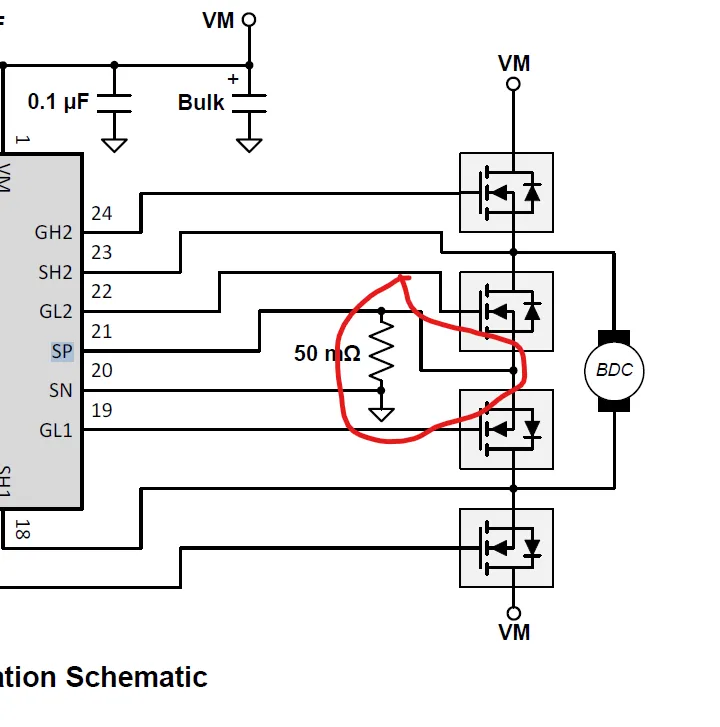

데이터시트에는 아래와 같이 명시되어 있습니다.

SP와 SN이 sense 저항으로 연결이 되어야 한다.

또한 Application에도 low side FET 2개의 소스가 SP로 연결되며, SP와 SN이 50 m옴으로 연결되어 있습니다.

따라서 아래와 같이 Schematic이 설계되어야 하는 것이 맞는 것 같은데,

제가 잘못 이해한 부분이 있는지 질문드립니다.

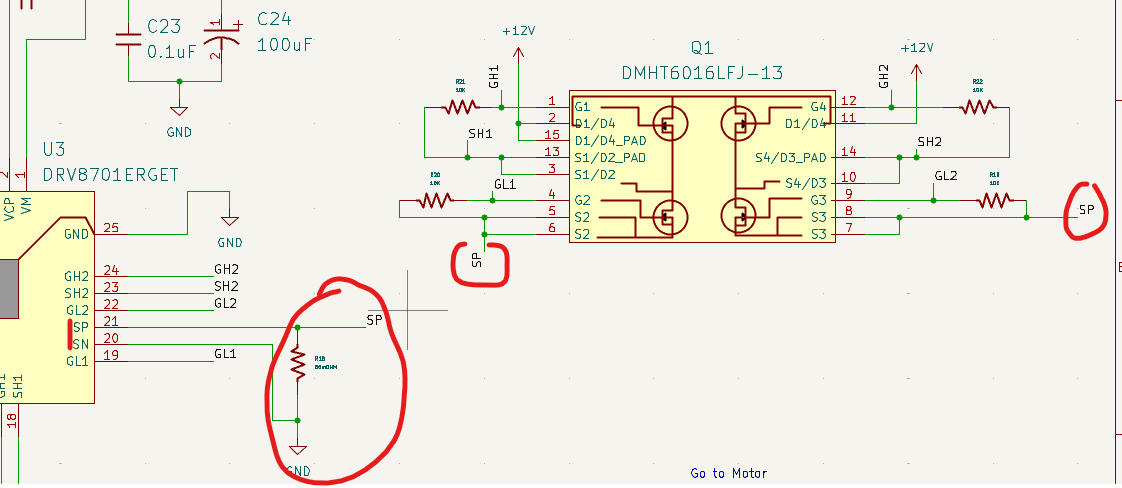

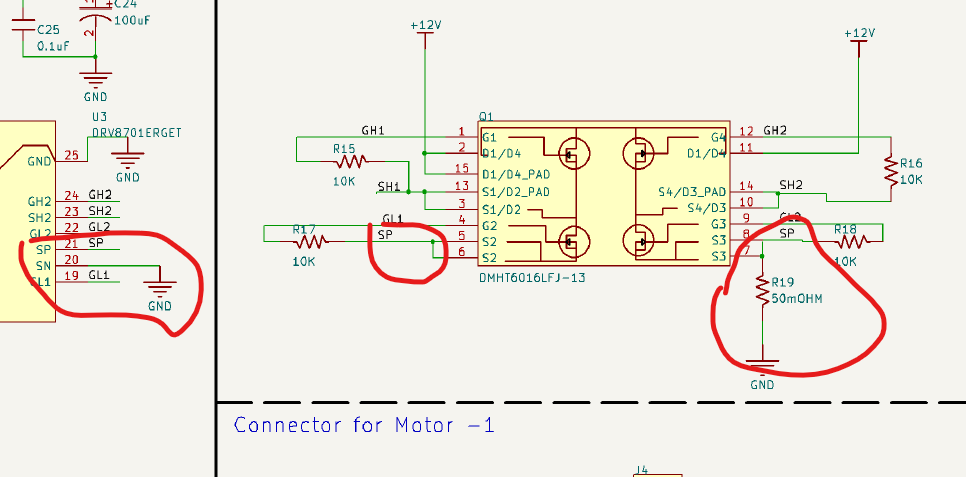

아래는 강의자료의 Schematic 입니다.

아울러, 데이터시트에 명시되어 있는 nFault와 SNSOUT 신호의 pull-up 관련해서는 강의에서 빠진 것 같은데 맞을까요?

답변 2

0

안녕하세요, 답변 남겨드립니다.

네, 맞습니다. 실제로 자세히 비교해보면 두 회로 모두 SP와 SN 단자 사이에 전류 검출 저항(Rsense)이 존재하는 동일한 동작 원리를 갖습니다. 데이터시트나 애플리케이션 회로에서는 Rsense가 명확히 “SP–SN 사이에 위치”하는 형태로 도식화되어 있지만, 어떤 회로도에서는 기호 표현상 SP와 SN이 바로 이어진 것처럼 보이기도 합니다. 그러나 실질적으로는 Low-side MOSFET 소스 노드와 GND 사이에 저항이 존재하고, 그 양단이 SP와 SN으로 연결되어 있기 때문에 동일한 기능을 수행합니다.

이런 착시는 주로 회로도 심볼 배치나 그라운드 심볼 처리 방식 때문입니다. 예를 들어 SN이 GND 심볼로 직접 내려가 있는 것처럼 보이더라도, 실제 Net 이름이 Rsense 하단 노드(GND_SENSE 등)로 따로 지정되어 있다면, 내부적으로 SP–Rsense–SN 구조가 유지됩니다. 즉, 전류 루프 상에서는 완전히 동일한 경로입니다.

따라서 현재 회로가 Rsense를 통해 Low-side 전류 검출이 이루어지고, 그 양단이 SP/SN으로 연결되어 있다면, 기능적으로 전혀 문제가 없는 정상적인 설계로 보셔도 됩니다. 이런 경우에는 오히려 데이터시트의 단순화된 블록 표현이 오해를 불러일으킬 수 있습니다.

혹시 nFAULT나 SNSOUT의 Pull-up 관련 회로를 함께 확인하신다면, 그것들은 Open-drain 출력이므로 외부 풀업 저항(보통 10kΩ 내외)을 추가해야 하며, MCU 입력핀 전압 레벨(VIO, 보통 3.3V 또는 5V)에 맞춰 풀업 전원을 연결해 주셔야 합니다. 예를 들어 nFAULT → 10kΩ → 3.3V, SNSOUT → 10kΩ → 3.3V 형태로 설계하시면 MCU 인터페이스 레벨과 정확히 매칭됩니다.

0